纲要:

1.SDF如何标识具体的dly

2.后仿真如何模拟transition

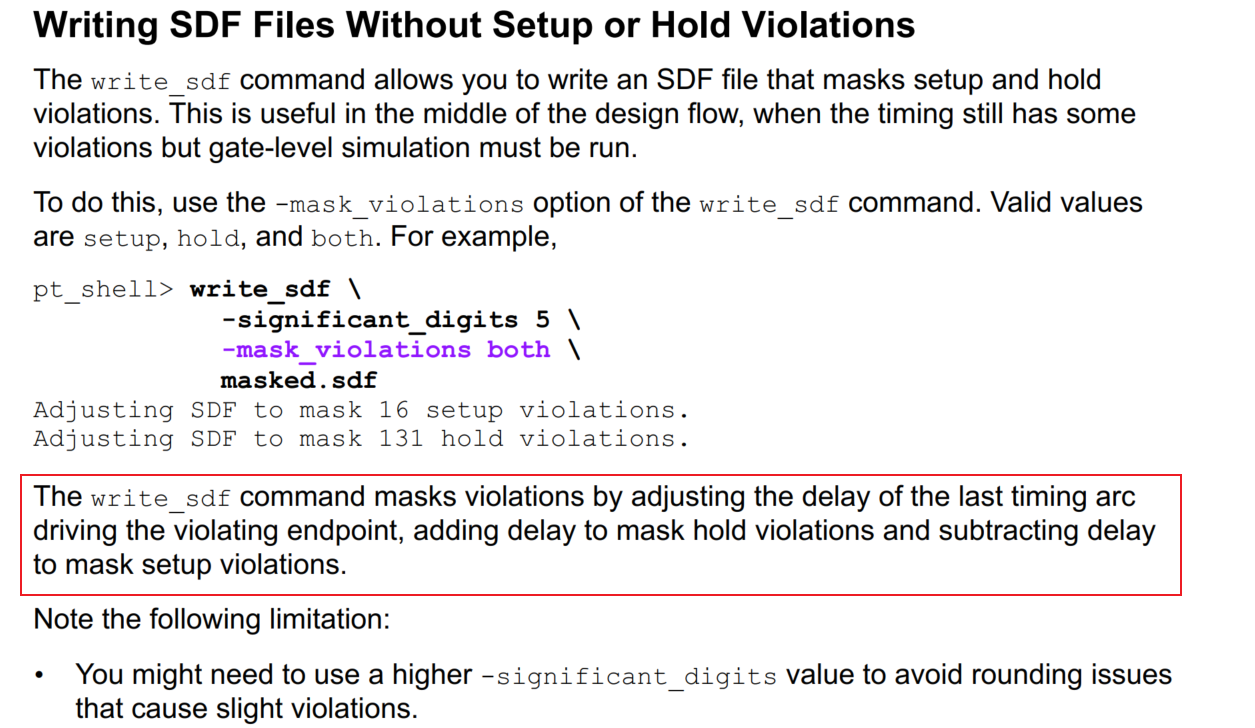

3.如何屏蔽时序违例的检查

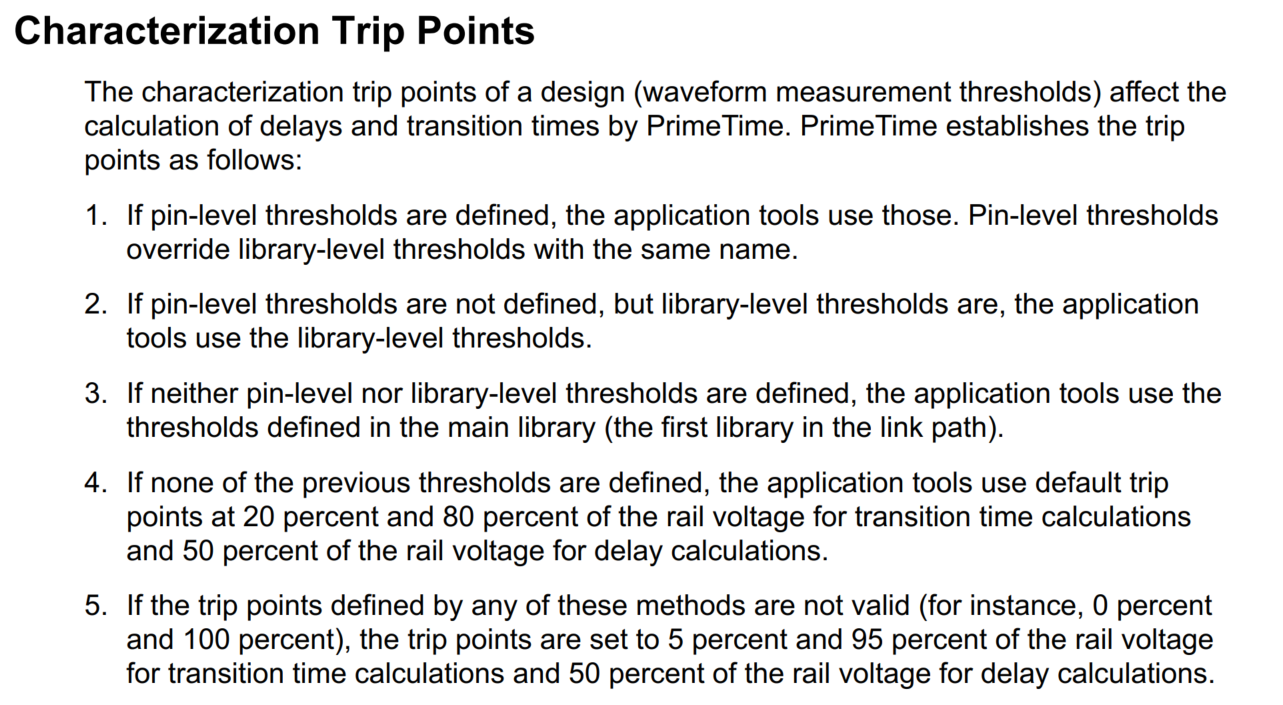

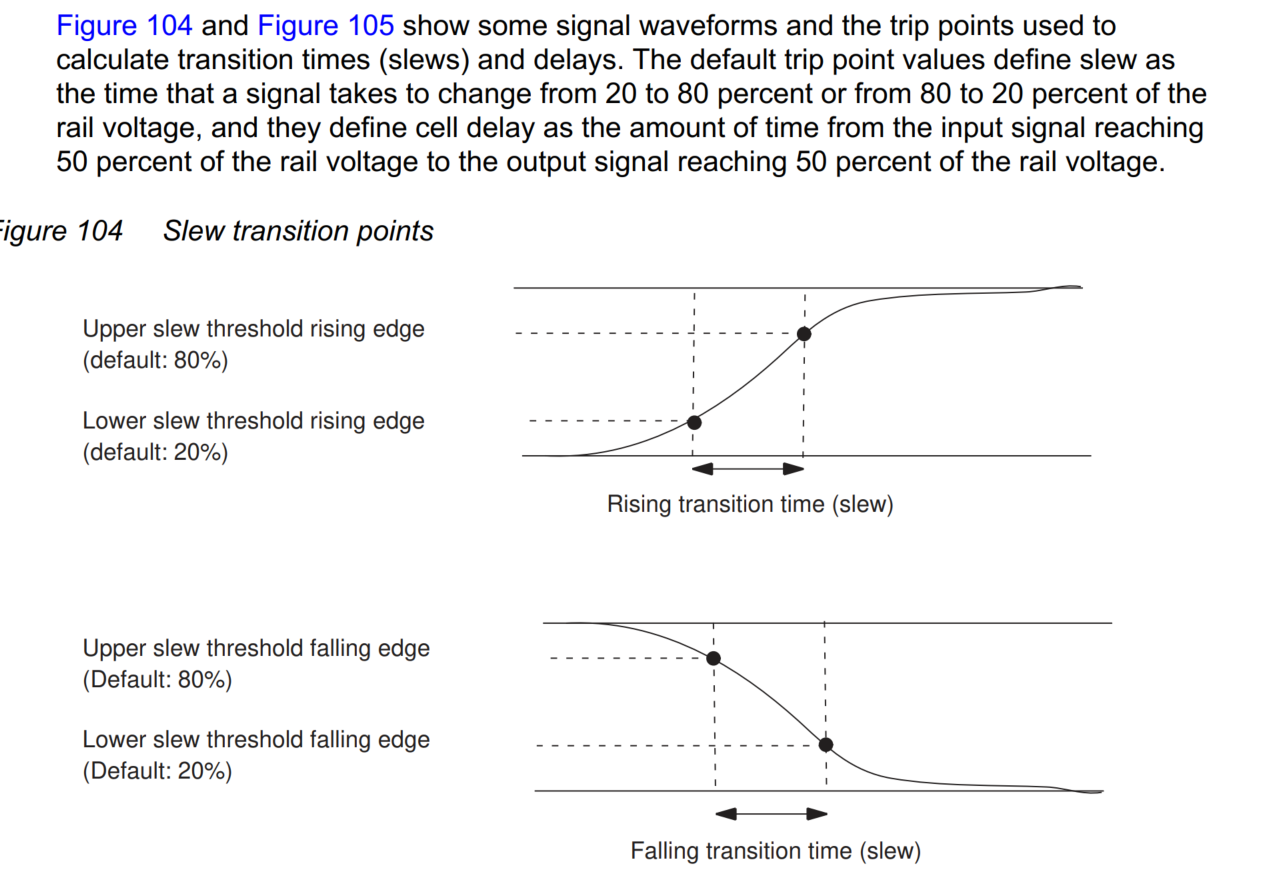

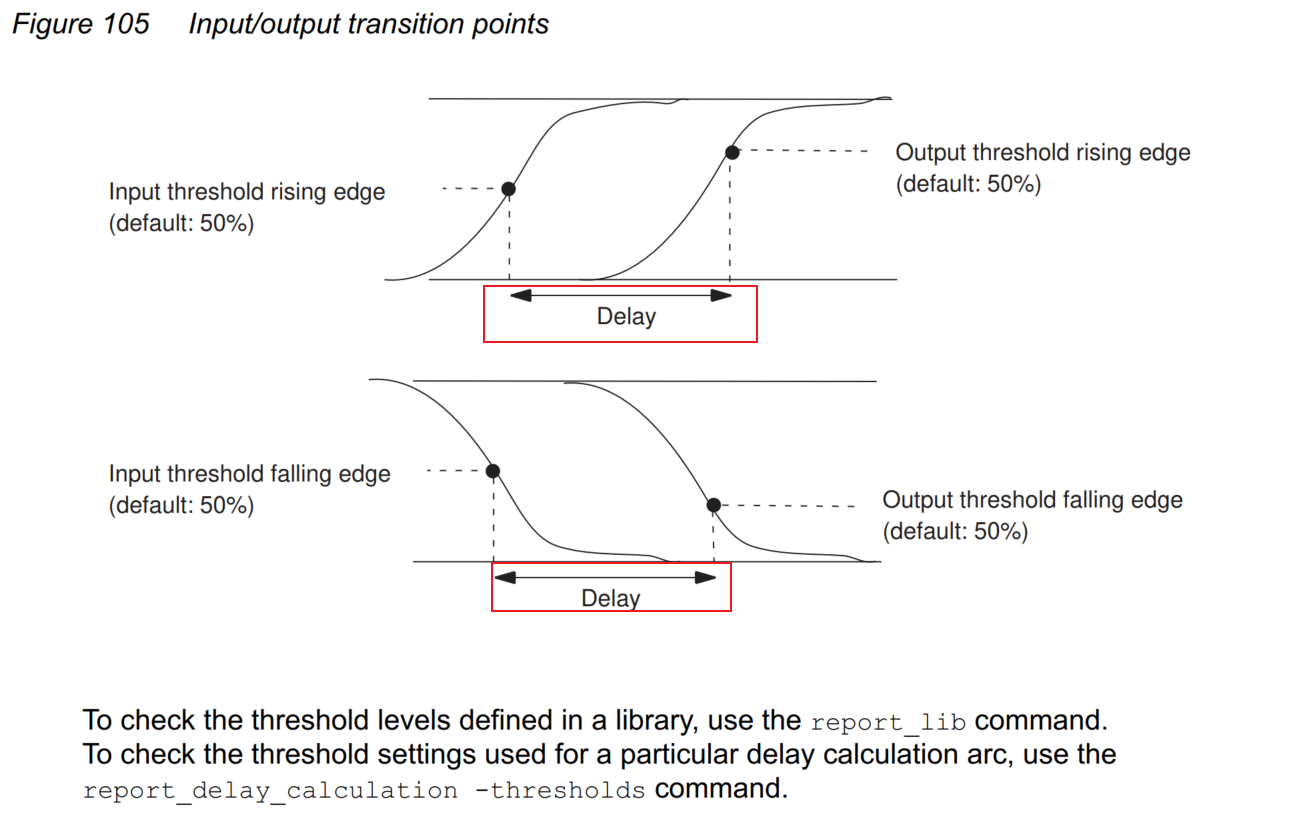

1.Delay Calculation

简单而言,工具在给出Dlay信息时,已经将transition的影响考虑在内,因此后仿真尽管在波形上的体现是没有transition斜率的体现,但是其Delay信息已经将其考虑在内;

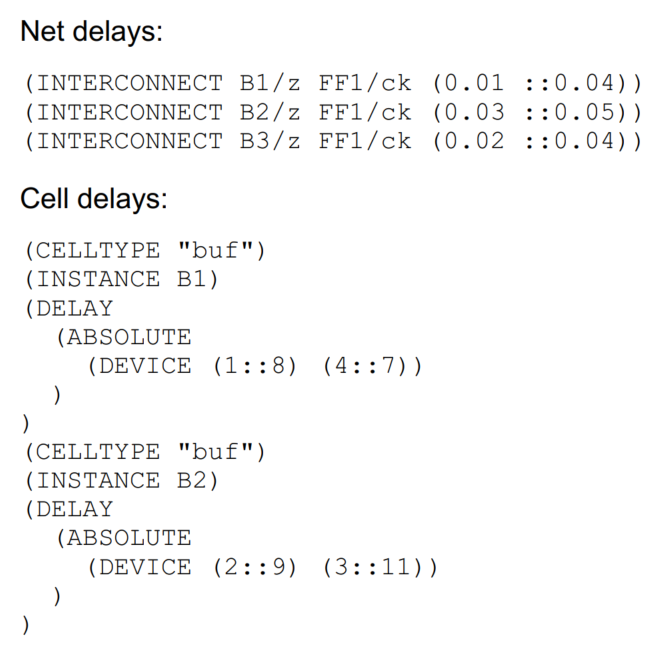

2.Back-Annotation

The SDF is used to gate-sim include the Net delays and Cell delays.

Note:

a.Hisilicon流程,ICC2(PR)-->starRC(SPEF net dly)-->STA(Signoff/SDF gatesim)

b.数模混合:尽管std cell的lib参数是由H-Spice仿真生成的,数字IP等也可由STA等工具生成lib文件用来数字后端的流程,但是由于Analog电路需要数模接口的详细电气特性,并不能建模来完美的对模拟电路进行仿真,因此Analog的电路部分需要和数字接口进行联合仿真,以保证数模系统的可靠运行,单独的模拟电路进行LVS等流程并不能完全保证连接上数字电路后系统可以可靠的运行。

参考材料:synopsys <pt ug>

<Static Timing Analysis to Nano Design>

最后

以上就是怕黑项链最近收集整理的关于Veri3.SDF后仿真时序检查的全部内容,更多相关Veri3内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复