我是靠谱客的博主 负责小刺猬,这篇文章主要介绍RISC-V— 蜂鸟 E200 设计总览和顶层架构介绍1、处理器设计和验证的特点2、蜂岛 E200 处理器核设计特点3、E200处理器核 RTL 代码风格4、蜂岛 E200 模块层次划分,现在分享给大家,希望可以做个参考。

目录

- 1、处理器设计和验证的特点

- 2、蜂岛 E200 处理器核设计特点

- 3、E200处理器核 RTL 代码风格

- (1)使用标准 DFF 模块例化生成寄存器

- (2)使用 **assign** 语法替代 **if-else** 和 **case** 语法

- 4、蜂岛 E200 模块层次划分

- a) Hierarchy

- b) e203_cpu_top

- c) Pipeline structure

1、处理器设计和验证的特点

处理器设计作为一种特殊 的 ASIC 设计,也需我们了解某些方面的背景知识和特点,归纳如下 。

- 熟悉汇编语言及其执行过程 。

- 了解软件如何经编译、汇编、链接最后成为处理器可执行的 二进制码的过程 。

- 了解计算机体系结构的知识。

- 处理器对时序和面积的要求一般会非常严格,需不断反复地优化时序和面积,因 此 对电路和逻辑设计的理解 需要 比较深刻 。

处理器的验证也有其特点,通常 需要从 3 个不同层面对处理器进行验证 。

- 需使用传统的模块级验证手段(例如 UVM 等 〉对处理器的子模块进行验证 。

- 需使用人工编写或者随机生成的汇编语 言测试用例在处理器上运行进行验证 。

- 需使用高等语言( 譬如 C、 C++ )编写的测试用例在处理器上运行进行验证。

2、蜂岛 E200 处理器核设计特点

- 模块化和可重用性

- 面积最小化,以追求低功耗、小面积

- 结构简单化

- 性能不追求极端

3、E200处理器核 RTL 代码风格

蜂鸟 E200 处理器核采用一套统 一 的 Verilog RTL 编码风格( Coding Style ) , 来自于严谨 的工业级开发标准,其要点如下。

- 使用标准 DFF 模块例化生成寄存器。

- 推荐使用 Verilog 中的 assign 语法替代 if-else 和 case 语法进行代码编写。

(1)使用标准 DFF 模块例化生成寄存器

a)对于寄存器避免直接使用 always 块编写 ,而是应该采用模块化的标准 DFF 模块进行例化 。

b) 使用标准DFF模块例化的好处包括以下内容。

- 便于全局替换寄存器类型。

- 便于在寄存器中全局插入延迟。

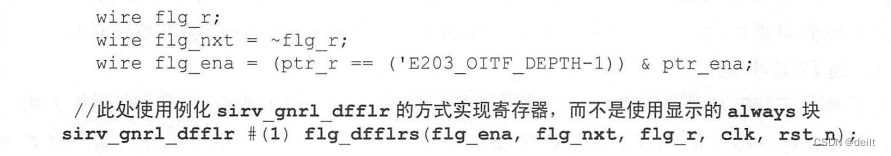

- 明确的 load- enable 使能信号(如下例的 flg_ena )方便综合工具自动插入寄存器级别的门控时钟以降低动态功耗.

- 便于规避 Verilog 语法 if-else 不能传播不定态的问题.

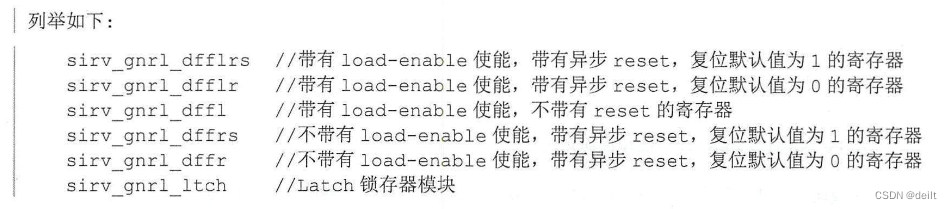

c) 标准 DFF 模块是一系列不同的模块

d) RTL code 如下:

//标准 DFF 模块 , 以 sirv_gnrl_dfflr 为例 , 代码片段如下

module sirv_gnrl_difflr

#(

parameter DW = 32

)

( input lden,

input[DW-1:0] dnxt,

output[DW-1:0] qout,

input clk,

input rst_n

);

reg [DW-1:0] qout_r ;

//使用 always 块编写寄存器逻辑

always @(psoedege clk or negedge rst_n)begin:DFFLR_PROC

if(rst_n == 1'b0)

qout_r <= {DW{1'b0}};

else if(lden == 1'b1)

qout_r <= dnxt ;

end

assign qout = qout_r;

//使用 assertion 捕捉 lden 信号的不定态

`ifndef FPGA_SOURCE//{

`ifndef SYNTHESIS//{

sirv_gnrl_xchecker #( //该模块内部是个 SystemVerilog 编写的断言,如下文详解

.DW(1)

)

u_sirv_gnrl_xchecker(

.i_dat(lden),

.clk(clk)

);

`endif//}

`endif//}

endmodule

//sirv_gnrl_xchecker模块代码片段

//此模块专门捕 捉不定 态, 一旦输入 的主 dat 出现不定 态,则会报错并终止仿真。

module sirv_gnrl_xchecker #(

parameter DW = 32

)(

input[DW-1:0] i_dat;

input clk ;

);

CHECK_THE_X_VALUE:

assert property (@(posedge clk)

((^i_dat)) !== 1'bx)

)

else $fatal ("n Error : Oops, detected a X Value !! This should never happen.n");

endmodule

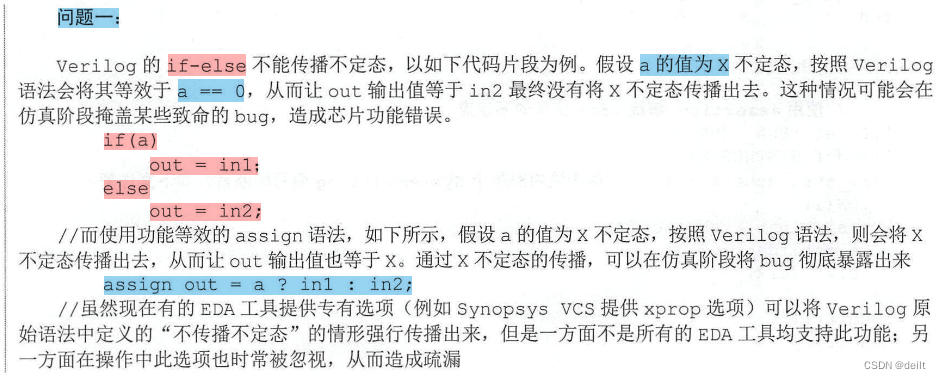

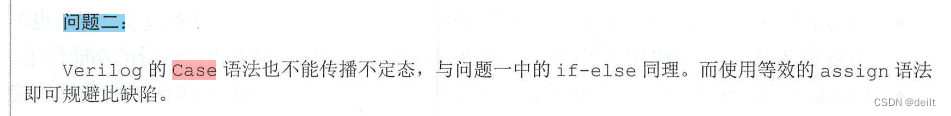

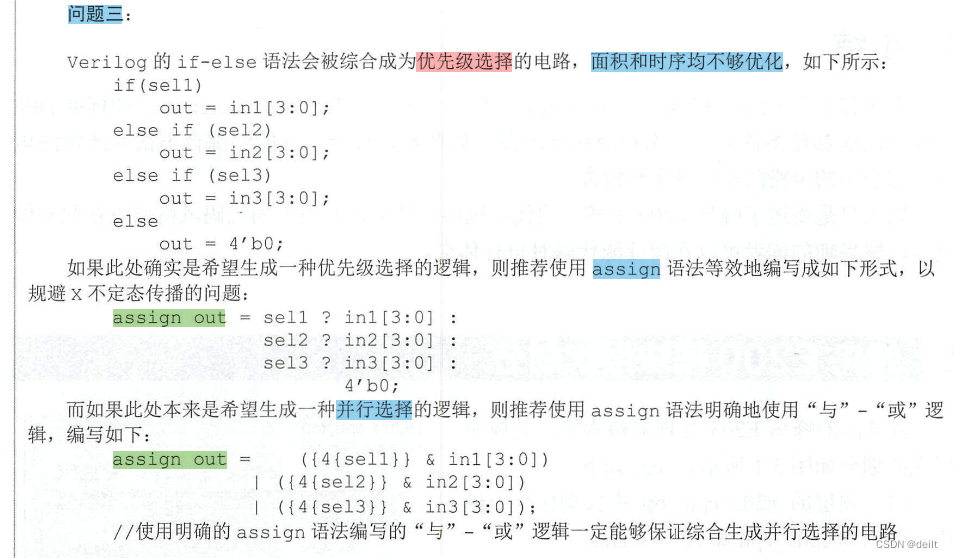

(2)使用 assign 语法替代 if-else 和 case 语法

Verilog中的 if-else 和 case 语法存在两大缺点。

- 不能传播不定态。

- 会产生优先级的选择电路而非并行选择电路,从而不利于时序和面积。

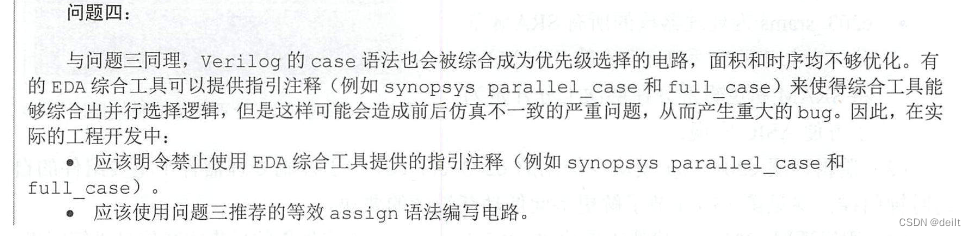

4、蜂岛 E200 模块层次划分

a) Hierarchy

| e203_cpu_top | Top module |

|---|---|

| e203_cpu | Logic top module of core |

| e203_clk_ctrl | Clock control module |

| e203_reset_ctrl | Reset control module |

| e203_irq_sync | Asynchronous interrupt signal sync module |

| e203_itcm_ctrl | ITCM control module |

| e203_dtcm_ctrl | DTCM control module |

| e203_core | Main logic top module of core |

| e203_ifu | Top module of fetch unit |

| e203_exu | Top module of execution unit |

| e203_lsu | Top module of load & store unit |

| e203_biu | Bus interface unit module |

| e203_srams | SRAM top module of core |

| e203_itcm_ram | ITCM SRAM module |

| e203_dtcm_ram | DTCM SRAM module |

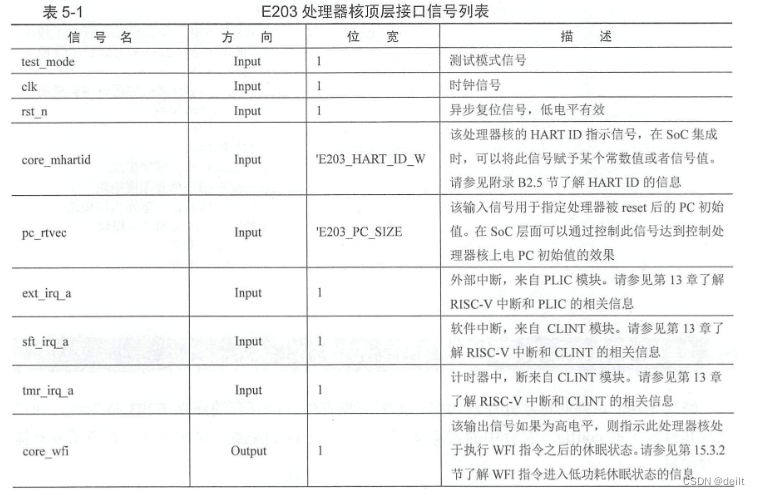

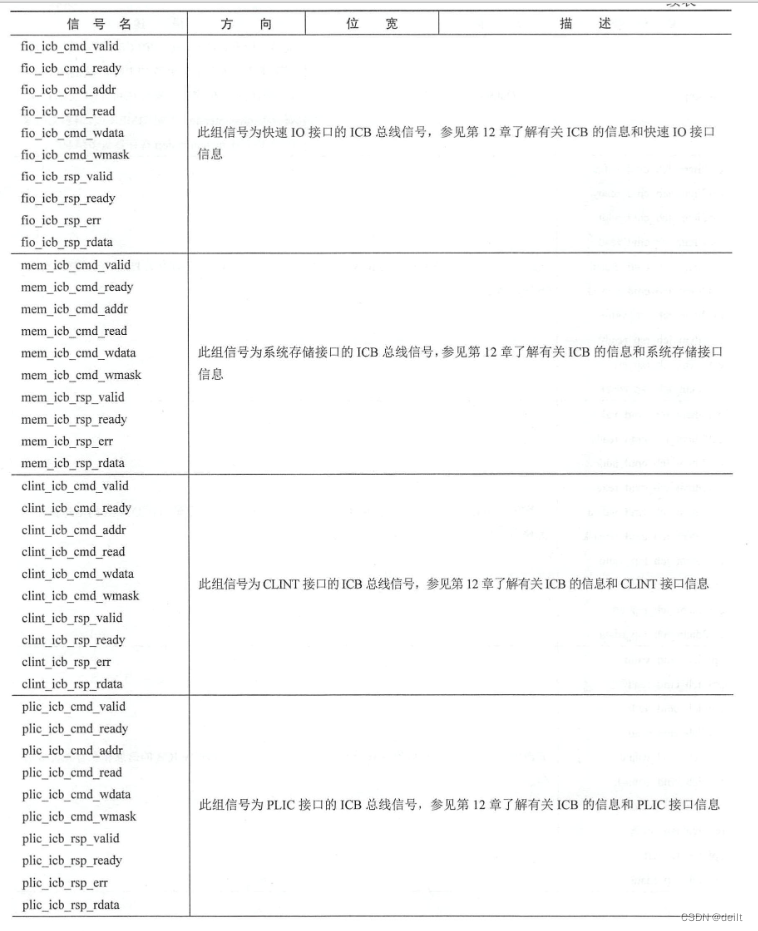

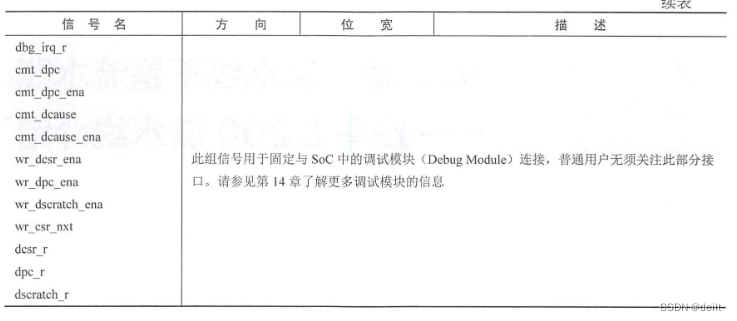

b) e203_cpu_top

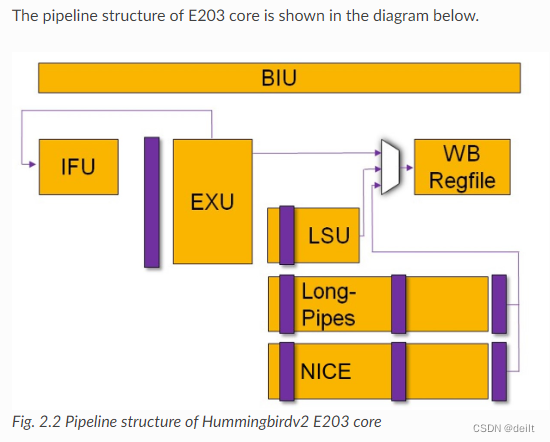

c) Pipeline structure

本文参考于《手把手教你设计CPU-RISC-V》(胡振波),详情请自行阅读此书。

最后

以上就是负责小刺猬最近收集整理的关于RISC-V— 蜂鸟 E200 设计总览和顶层架构介绍1、处理器设计和验证的特点2、蜂岛 E200 处理器核设计特点3、E200处理器核 RTL 代码风格4、蜂岛 E200 模块层次划分的全部内容,更多相关RISC-V—内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复