一、设计要求

- 1、 设计四位十进制的简易数字频率计,能够利用系统时钟产生1KHZ-9999KHZ方波信号,并且设计模块对1KHZ-9999KHZ的方波信号进行频率测量;

- 2、测量的方波频率值要在4位数码管上进行显示

- 3、此频率计要设有一个整体复位控制(有reset 按键),可恢复初始状态;

- 4、利用2个按键控制方波频率在1KHZ-10MHZ可调,步进1kHZ。1个按键按下频率增加1KHZ,另外一个按键按下频率减少1KHZ;

二、设计思路

- 1、分析要求,由设计要求知简易频率计可以分为两个部分:

第一部分:频率范围是:1KHZ-9999KHz,且频率可调,步进值为1kHz的方波发生器;

第二部分:简易的频率计;

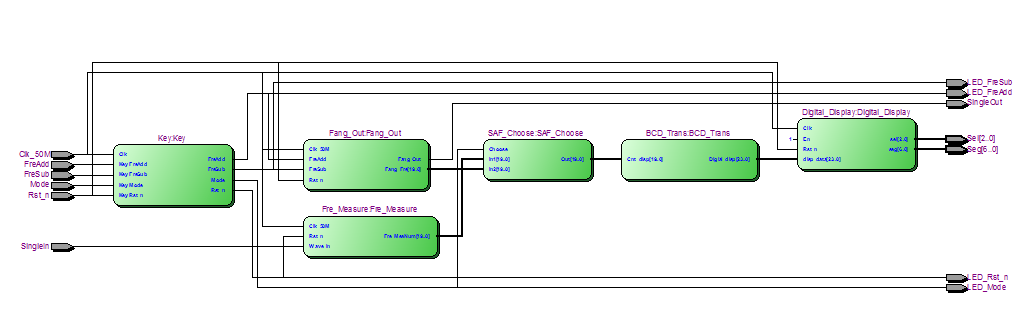

- 2、通过顶层化设计思想,可以将任务分为四个模块:

第一部分:按键模块,(四个按键:复位、模式选择、频率加、频率减),其需要包含按键消抖模块;

第二部分:数码管显示模块,需要显示:方波发生器的方波频率;和频率计的测量频率;其需要一个BCD码转换模块和模式按键作为选择端的二选一模块;

第三部分:方波发生模块,其需要一个分频可键控的分频器;

第四部分:频率计模块,采用预置闸门法进行频率测量,因此需要一个计数器和分频器产生一个预置闸门;

三、模块讲解

第一部分:按键模块

1、按键消抖原理讲解

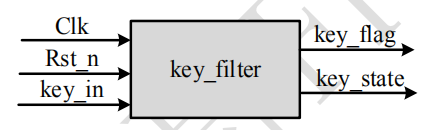

- 对于单按键的消抖模块,其接口如图所示,接口声明功能描述如下

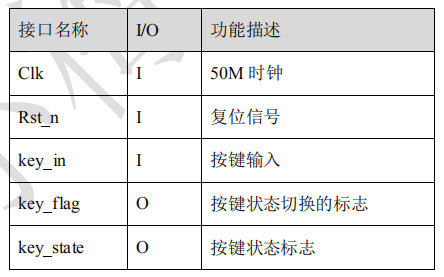

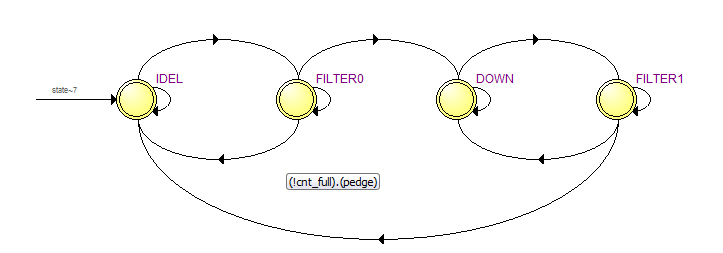

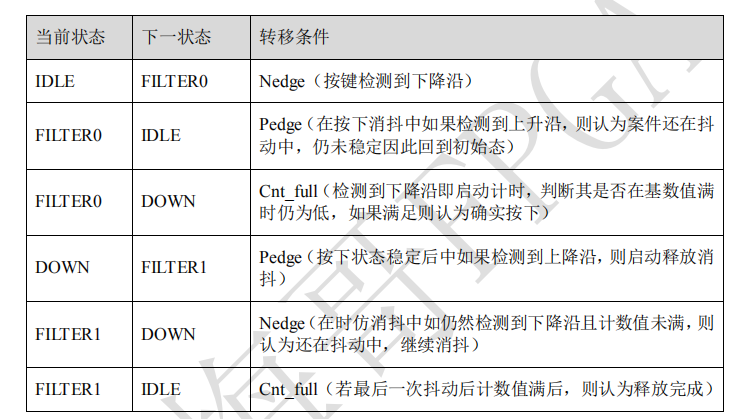

- 按键消抖经常使用状态机来进行消抖,按照状态机的状态可以分为以下四个状态:为按下空闲时IDLE、按下抖动滤除状态FILTER0、按下稳定状态DOWN、释放抖动滤除状态FILTER1.其状态转换图如下:

其转移条件入下表所示:

2、按键具体模块

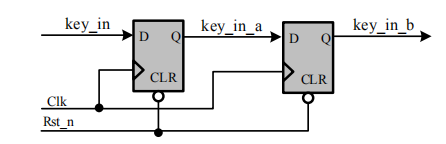

1)单bit信号同步

- 按键信号对于FPGA内部信号来说是一个异步信号,如果不进行处理直接输入,很容易出现时序违例出现亚稳态。因此需要将按键信号先同步到FPGA的时域里面,常见的方法便是二级触发器,其结构如图所示:

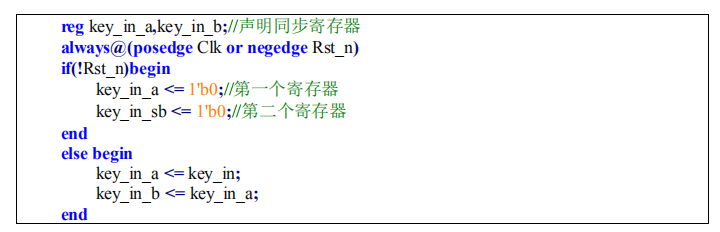

Verilog代码:

Verilog代码:

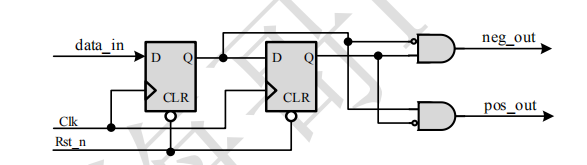

2) 边沿检测电路

- 通过上述状态机可以以看出,在转换条件中需要边沿检测电路,因此设计边沿检测电路,其原理图如图:

- 其检测过程:

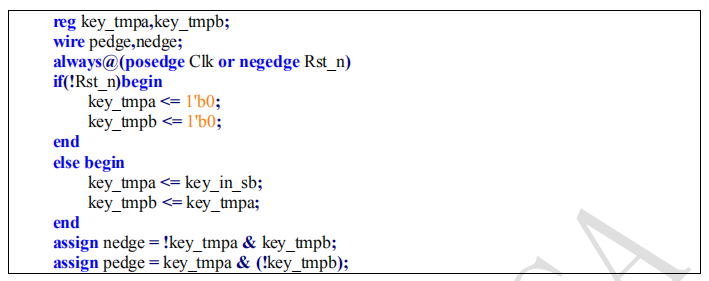

根据上图可知,其为比较两个时钟输入信号电平是否一样,当前一个时钟为1,后一个时钟为0时:pos_out=1;反之neg_out=1;其他状态两个口为0;

Verilog代码:

3)状态机消抖设计

代码请参考上传资料;

第四部分:显示模块

1、数码管动态显示

-

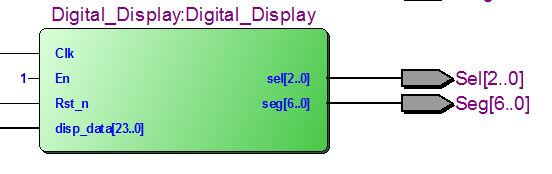

对于数码管显示模块,其接口如图所示,接口声明功能描述如下

-

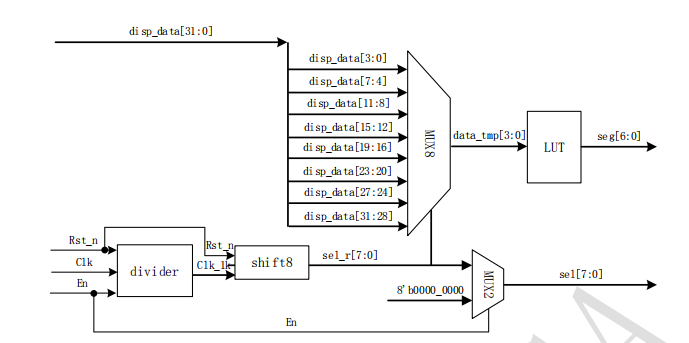

数码管逻辑图为:

-

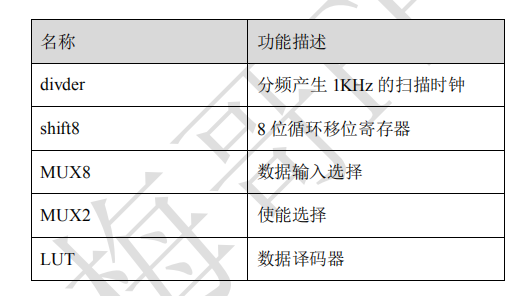

子模块功能描述

第三部分:频率计模块

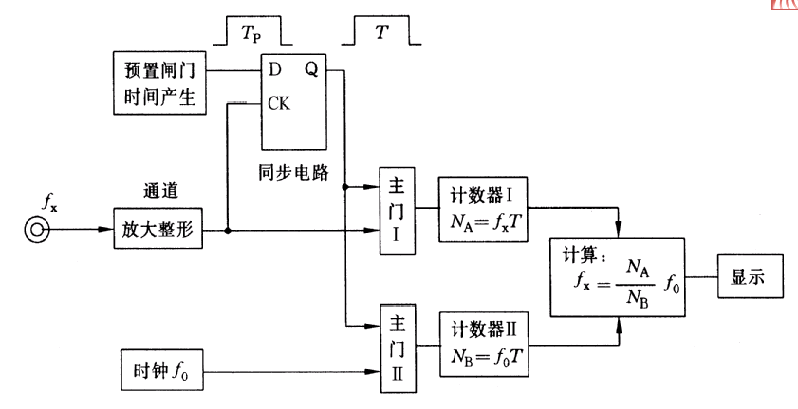

1、预置闸门法原理

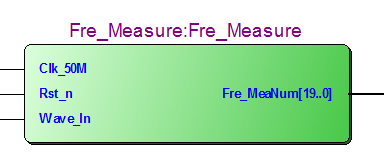

- 对于数码管显示模块,其接口如图所示

- 其逻辑图为:

D触发器的功能:对应 CK 端上升沿,D端的信号传送到Q端。

由于D触发器的同步作用,计数器Ⅰ所记录的 NA已不存在 ±1 字误差的影响。 但是,实际的闸门时间T已不等于预置的闸门时间TP。因此,还需要同时测量实际的闸门时间T的大小。为了测量实际的闸门时间T,设置了计数器Ⅱ,并用标准时钟 f0 进行计数来确定实际闸门时间T的大小。

2、预置闸门法代码

具体代码请参考上传的文件内容;

由于频率计部分原理同分频器一致再次不进行叙述;

三、最后视图

最后代码,及原理图均已上传,详情参照具体代码;

下载地址:https://download.csdn.net/download/weixin_42348938/12063614

最后

以上就是飞快缘分最近收集整理的关于基于FPAG的简易数字频率计设计一、设计要求二、设计思路三、模块讲解三、最后视图的全部内容,更多相关基于FPAG内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复