文章目录

- 前言

- 参考链接

- 一些常用指令

- 例程1 CLA ADC Sampling and Filtering

- 例程2 CLA ADC Sampling and Filtering with Buffering in a Background Task

- 例程3 CLA background nesting task

- 例程4 Controlling PWM output using CLA

- Selects the master core of a specified pin

- 关于CLA全局变量初始化

- 例程5 Just-in-time ADC sampling with CLA

- 实验分析

- 实验结果

- 例程6 Optimal offloading of control algorithms to CLA

- 配置

- 分析

- 验证

- 例程7 Handling shared resources across C28x and CLA

- 参考文献

前言

相比于旧版软件,C2000Ware_3_01_00_00多更新了几个CLA例程,十分的贴近实际需求,有助于初学者入门。当前共有7个例程。

所有的例程可以在C:tic2000C2000Ware_3_01_00_00driverlibf28004xexamplescla找到。

学习顺序建议4 -> 3 -> 1 -> 2 -> 6 -> 7 -> 5

其中例程6与实际应用比较贴近。

参考链接

已经有许多其他博客总结了一些有用的知识,列在这里备用。

- 28377d双核仿真与CLA仿真

- DSP28377扩充CLA程序空间的问题

一些常用指令

__attribute__ // 指定属性

extern float duty; // 指定外部变量

#pragma diag_suppress=770 // 屏蔽编译器770号警告

volatile // 特征修饰符,作用是作为指令关键字,确保本条指令不会因编译器的优化而省略,且要求每次直接读值。

__mdebugstop(); // CLA调试时当做断点使用

例程1 CLA ADC Sampling and Filtering

此示例将EPWM1A配置为以10 KHz(周期=0.1 ms)运行,以触发ADC通道A0上的start-of-convertion (SOC)。该通道将依次对设置为以1KHz运行的EPWM4A进行采样。转换结束时,触发ADC中断。中断信号将用于触发运行FIR滤波器的CLA任务。滤波器设计为低通滤波器,截止频率为1KHz;它将消除输入信号中的奇次谐波,使方波平滑为正弦波形。

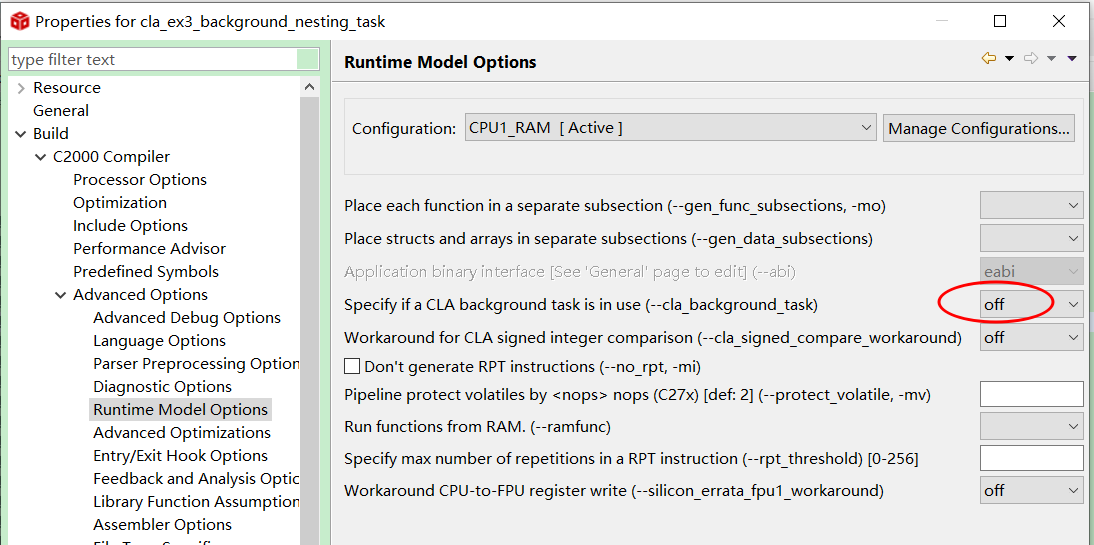

注意,由于此示例不使用后台 CLA task,因此此项目的编译标志CLA_background_task已关闭。将此标志设置为on以启用后台CLA任务。此选项在Project Properties -> C2000 Build -> C2000 Compiler -> Advanced Options -> Runtime Model Options.

例程2 CLA ADC Sampling and Filtering with Buffering in a Background Task

此示例将EPWM1A配置为以1 KHz(周期=1 ms)运行,以触发ADC通道A0上的SOC。此通道将依次采样设置为以100Hz运行的EPWM4A。转换结束时,触发ADC中断。中断信号将用于触发运行FIR滤波器的CLA任务。滤波器设计为低通滤波器,截止频率为100Hz;它将消除输入信号中的奇次谐波,使方波平滑为正弦波形。CLA后台任务将在循环缓冲区中连续缓冲已滤波的输出。

注意,此项目的编译标志CLA_background_task已经打开。启用后台任务将在任务切换期间添加额外的保存/还原周期,从而增加触发到任务(trigger-to-task)延迟。如果应用程序不使用后台CLA任务,建议关闭此标志以获得更好的性能。将此标志设置为on以启用后台CLA任务。此选项在Project Properties -> Build -> C2000 Compiler -> Advanced Options -> Runtime Model Options.

需要CLA后台任务的时候可以参考该例程的写法。

例程3 CLA background nesting task

此示例将CLA任务1配置为由以2赫兹(周期=0.5秒)运行的EPWM1触发。后台任务被配置为由运行在.5Hz(周期=2s)的CPU定时器触发。CLA task 1在任务开始和结束时切换LED1,后台任务在任务开始和结束时切换LED2。后台任务将被Task1抢占,因此即使在LED2打开时,LED1也将切换。

注意,此项目的编译标志CLA_background_task已经打开。启用后台任务将在任务切换期间添加额外的保存/还原周期,从而增加触发到任务(trigger-to-task)延迟。如果应用程序不使用后台CLA任务,建议关闭此标志以获得更好的性能。将此标志设置为on以启用后台CLA任务。此选项在Project Properties -> Build -> C2000 Compiler -> Advanced Options -> Runtime Model Options.

例程4 Controlling PWM output using CLA

这个例子展示了如何使用CLA更新PWM信号输出。EPWM1被配置为在固定频率100kHz的两个信道上生成互补信号。EPWM4被配置为用于触发频率为10 KHz的周期性CLA控制任务。CLA任务的控制逻辑非常简单,通过在每次迭代中增加0.1并将其保持在0.1-0.9的范围内来改变EPWM1的输出。对于实际的应用场景,可以根据应用程序将控制逻辑修改为更复杂的逻辑。另一个CLA任务(CLA task 8)在程序开始时由软件触发,用来初始化CLA的全局变量。

个人觉得这个例子适合用来入门CLA。除了手册中提到的内容,这个例子还可以尝试和验证一些其他内容。以下内容是个人理解,如有错误还望不吝赐教:

Selects the master core of a specified pin

虽然由CLA控制ePWM1的输出,但其实CLA只是修改CMPA寄存器,实际ePWM1模块对应的GPIO仍由c28内核控制,故初始化的控制内核仍是c28:

//

// GPIO0 is set to EPWM1A

// GPIO1 is set to EPWM1B

//

GPIO_setMasterCore(0, GPIO_CORE_CPU1);

GPIO_setPadConfig(0,GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_0_EPWM1_A);

GPIO_setMasterCore(1, GPIO_CORE_CPU1);

GPIO_setPadConfig(1,GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_1_EPWM1_B);

关于CLA全局变量初始化

例程中将CLA中全局变量duty的初始化放在了CLA task 8中,然后使用软件触发。

__attribute__((interrupt)) void Cla1Task8 ( void )

{

//

// Uncomment this to debug the CLA while connected to the debugger

//

//__mdebugstop();

// duty = 0.1f;

}

但其实把初始化放到main函数中也是可以的。也即并不需要特意在CLA中做变量初始化,只要在CLA任务执行前,在c28的代码中完成初始化就行。

例程5 Just-in-time ADC sampling with CLA

这个例子展示了如何利用ADC的早期中断特性,结合CLA的低中断响应,实现更快的系统响应和高频控制回路。EPWM1被配置为产生频率为1MHz的脉冲宽度调制输出信号,这也用于在每个周期触发ADC采样。ADCA被配置为对通道0上的输入进行采样,并在S/H+偏移周期结束时生成早期中断。此中断用于触发CLA控制任务。CLA的任务实现了控制逻辑,在及时(just-in-time)读取ADC采样数据的基础上更新PWM输出的占空比,即一旦ADC结果被锁定,CLA的早期中断特性和低中断延迟允许在读取ADC数据之前进行一些预处理,并且在下一个中断到来之前仍然完成对PWM输出的更新,即数据读取和脉冲宽度调制更新在1兆赫周期内完成。为了说明这一点,我们使用三点移动平均滤波器来模拟一些处理过程,并且在读取ADC结果之前对滤波代码进行了一些步骤,我们将这些步骤视为预处理代码。ADC中断偏移量根据预处理代码消耗的周期进行编程。

中断偏移值的计算如下:

- 已编程的ADC采集周期=10 SYSCLKS

- 12位数据的转换时间=10.5 ADCCLKS=N=42 SYSCLKS

- CLA任务触发器到获取第一条指令的延迟=4

设中断偏移值为“x”,CLA控制中的代码在ADC读取前的任务需要以下周期:

- 设置分析gpio:3个周期

- 预处理:13个周期

- 总计=3+13=16个周期

如手册TRM中所述,为了及时读取,读取ADC之前的总延迟应为(N-2)周期=40,即:x+4+16=40,x=20

注:-此项目的优化已关闭,上面引用的周期与此案例相对应。

GPIO2用于分析。GPIO2在CLA任务1开始时设置,在任务结束时重置。因此GPIO2的开启时间表明CLA的运行时间。为了验证示例功能,观察CRO上的GPIO0(PWM输出)和GPIO2(GPIO分析)。GPIO0和GPIO2的上升沿之间的周期差表示从ADC触发时间到在CLA任务中建立分析GPIO的总延迟,基于上述计算,该总延迟应在44个周期(440 ns)左右。

实验分析

-

DSP的主频是100MHz,也即一个系统时钟周期是10ns。

-

ePWM1模块被配置为1MHz,增计数,在TB=0时输出高电平,TB=CMPA时输出低电平。也即每个PWM周期开始时输出高电平。

-

当TB=0时触发ADC中断,ADC采样窗口10个系统时钟周期,也即100ns。

-

ADC转换数据需要42个系统时钟周期,即420ns。

-

CLA任务开始的中断并不是传统的ADC-EOC中断,而是提前了20个系统时钟触发。

实验结果

手边的设备采样率不是很高,所以本应是方波的波形有些畸变。

- 1通道橙色是PWM信号,上升沿是每周期的开始,此时会触发AC采样;

- 2通道紫色是CLA中断的执行时间,高电平时程序正在执行;

- ADC采样到CLA程序开始执行共耗时约440ns;

- 在新的PWM周期开始前,CLA中断能够执行完毕,将新的占空比更新到寄存器中。

例程6 Optimal offloading of control algorithms to CLA

配置

这个例子展示了如何将控制算法从CPU移植到CLA,以满足系统需求。在本例中,模拟了两个控制回路,速度较快的一个(回路1)在200 KHz下运行,速度较慢的一个(回路2)在20 KHz下运行。回路1感应ADCA通道0的第一个参数,运行PI控制器,并对EPWM1A的输出贡献80%的权重。回路2感应ADCB通道2的第二个参数,运行PI控制器,并对EPWM1A的输出贡献20%的权重。需要注意的是,由于这些只是软件模拟的控制回路,但不涉及实际的物理过程,因此更新输出不会对采样输入产生任何影响。

ADCA被配置为使用SOCs 0-3对第一参数进行过采样以抑制噪声,并且类似地ADCB被用于对第二参数进行过采样。EPWM4和EPWM5配置为分别在环路1和环路2频率触发ADCA和ADCB采样。一旦所有4个soc的转换完成,CPU ISR或CLA任务将基于用户的配置被触发。

主回路中还有一个后台任务,当“system_OFF”设置为1时,该任务将禁用整个系统,包括PWM输出和控制回路。当“system_OFF”恢复为0时,系统将再次启用。默认情况下,system_OFF设置为0,但它的值可以通过将其添加到表达式窗口并写入其中来动态更新。

项目中包含了DCL库,以在两个环路中使用的最优PI控制器。已将用户可配置的预定义符号“run_loop1_cla”添加到项目选项中,以指定是在C28x上运行loop1还是在cla上运行loop1。GPIO2和GPIO3用于分析loop1和loop2的执行。

loop2一直在C28内核运行,loop1可选在C28或CLA;

如果在C28内核运行,还提供了中断嵌套的代码;

提供了停用和复用ADC中断的代码;

通过该示例也能获得一个事实:对于280049C来说,单PI控制器控制的环路速度上限约为200kHz。

分析

对于run_loop1_cla==0,即两个循环都在CPU上运行

- loop1利用率=77.5

- Loop2利用率=6

- 后台任务在一个while内循环

总CPU利用率大于利用率限制(UB),因此系统是不可调度的,低优先级任务(Loop2)的执行永远不会完成(在GPIO3上没有观察到切换),而且后台任务也没有机会执行。

对于run_loop1_cla==1,即高频控制环路(loop1)被移植到cla,而loop2在CPU上运行:

- loop1利用率=77.5

- Loop2利用率=6

总CPU利用率仅为6,因此系统完全可调度,任何环路都不会发生丢失,将loop1卸载到cla将节省CPU带宽到同时执行后台任务。

验证

为了快速检查示例功能,可以向模拟信道提供恒定的DC高/低输入,而不是改变模拟电压。两个回路的目标值都设置为一些中间值,即3500对应于 2.8V。现在,因为传感输入是常数,与目标值不同,因此控制器输出很快就会饱和为1或0。因此,“占空比”变量只能取基于回路中使用的方程的固定值,实际上,占空比输出是非常直观的。例如,如果两个输入都很低(GND),控制器将尝试产生最大占空比,因为目标高于感测值,因此占空比应为1.0(0.2+0.8),但将饱和到0.9(定义的最大值)。同样,如果两个输入都设为高,则占空比为0.1(定义的最小饱和值)。

例程7 Handling shared resources across C28x and CLA

这个例子展示了如何应对跨C28x和CLA共享资源的挑战。由于外围设备在CLA和CPU之间共享,它们对寄存器的重复“读-改-写”可能导致数据竞争,最终导致数据冲突或不正确的功能。在本例中,CPU ISR和CLA任务独立运行。CPU ISR由EPWM4@10KHz触发,通过控制AQCSFRC的CSFB位,翻转EPWM1B输出。CLA任务由EPWM5@100Khz触发,通过控制AQCSFRC的CSFA位,翻转EPWM1A输出。因此,在这个过程中,CPU和CLA在不同的频率独立地对AQCSFRC寄存器进行“读-改-写”操作,这样就有可能出现竞争,并且其中一个来源的更新会丢失或被覆盖。这可以通过将“phase_shift_ON”设置为0U并将EPWM1A和1B输出至示波器来观察到。

这是一个典型问题,可以通过mutex等软件握手机制来处理。但是大多数实时控制程序都是时间敏感的,并且无法承受额外的软件开销,因此本示例建议使用另一种基于硬件的技术来避免CPU和CLA之间的共享资源冲突:

利用EPWM模块的移相机制,根据需要调度CLA任务和CPU-ISR。EPWM4每ZERO事件产生一个同步脉冲,并向EPWM5提供20个周期的相移。这样,CLA task和C28x ISR都以原始频率运行,即100KHz和10KHz,但CLA task的相位偏移为20个周期,相对于CPU ISR。因此,不会发生对AQCSFRC的并发读修改写入,并且EPWM1A和EPWM1B的输出符合要求,即EPWM1A上的一致50 KHz脉冲宽度调制输出和EPWM1B上的一致5 KHz脉冲宽度调制输出,两者的占空比均为50%。为了在本例中使用此移相机制,请确保将“phase_shift_ON”设置为1。

参考文献

[1] F28004x Firmware Development Package USER’S GUIDE

最后

以上就是震动柚子最近收集整理的关于TMS320F280049C 学习笔记11 控制率加速器 CLA 例程前言例程1 CLA ADC Sampling and Filtering例程2 CLA ADC Sampling and Filtering with Buffering in a Background Task例程3 CLA background nesting task例程4 Controlling PWM output using CLA例程5 Just-in-time ADC sampling with CLA例程6 的全部内容,更多相关TMS320F280049C内容请搜索靠谱客的其他文章。

发表评论 取消回复