考研408复习日志

计算机组成原理

>随机存取存储器RAM基本概念

(1)随机存取存储器(RAM) Random Access Memory,即随机存取存储器,这个名字的由来,是因为当我们给定一个存在于 存储芯片的内存地址后,我们访问这个地址所花的时间,不会和这个地址大小有正比或者反比的关系 ,因为存取都是随机的。 RAM分为两类,一类称为静态随机存取存储器,另一类称为动态随机存取存储器,这两类在存储元密度,运行速度,功耗等指标上,有着明显区别。

(1.1)动态随机存取存储器(DRAM)

(1.1.1)基本原理

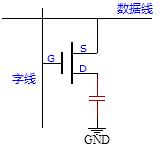

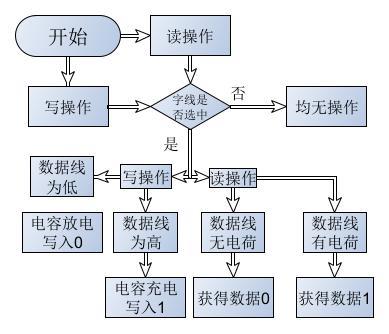

该类存储器的基本原理是:利用电容储存电荷,用字线决定MOS的导通/截止,当字线为高电平 ,即选中该存储元,如果电容中存在足够的电荷,那么电荷就会通过MOS管流到数据线上,数据线 即判断该存储元存储的是信号1(即高电平),反之,如果选中该存储元后,MOS管也导通后,数据 线并未检测到电荷的流动,则说明该存储元存储的是信号0(即低电平),具体原理图和流程图如图 1,图2:

(1.1.2)性能指标

#存取速度:

衡量存取速度的指标是存取周期的大小,存取周期一般包括读周期和写周期,这里我们讨论 读周期。 由之前的基本原理部分可知:如果存储的数据是1,那么当数据线检测到电流从电荷流出后 ,就说明电容中已无电荷,等于变成了存储数据0,我们仅仅是想要读取该存储元的内容,而不应 该破坏它,但是就目前情况来看,就好像是看完一本书后,就把书烧掉一样,所以DRAM的读取 方式是破坏式读取,那么要保证读取完数据之后,源数据保持不变,就得在读取完后,再写一次 ,所以每一次数据的读取都包含两步:读取数据,重写数据。 并且图1之中,电容不是完全绝缘的,所以其上的电荷会逐渐流失,一般来说,充电完成之 后,2ms左右的时间,电荷就会流失掉大部分,所以需要定时刷新,保持原有的电容状态,而刷新的方式我们之后会讲到。

所以就目前而言,DRAM的读周期是包括读数据,重写数据,且定时刷新。

(1.1.3)DRAM的刷新

我们假设有一个128x128的存储矩阵,存/取周期为0.5us,刷新方式是按行刷新刷新一行的时 间 是0.5us,再生周期是2ms。

#存/取周期中刷新

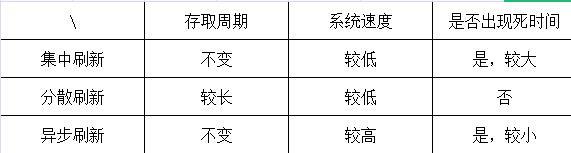

当进行了一次存/取操作后,立刻对第一行进行刷新,所以一次存/取+刷新耗时是1us,也 就是说只需要128us就可以对128x128的存储矩阵进行刷新,这就叫"分散刷新",把每一行的刷 新任务放到每一个存/取周期之中。

#再生周期中最后刷新

以再生周期为周期,再生周期前面一部分时间,用来进行正常存/取操作,但是再生周期 最后一段时间,用来给存储矩阵进行刷新,2ms一共有4000个0.5us,而最后要花费128个周 期对存储矩阵的128行进行刷新,(128/4000) x 100% = 3.2%,称之为死时间率,因为在刷新 期间,CPU无法对存储器进行存/取操作的(刷新是存储器自己完成的,CPU不介入控制 ), 所以称之为死时间,这种刷新方式称之为"集中刷新"。

#再生周期中规律刷新

在再生周期中按照一定规律刷新,再生周期为2ms,要对128行进行刷新,故2ms/128 = 15. 6us,也就是说每隔15.6us,就刷新一行,占用0.5us的时间,这种方式称之为"异步刷新"。 分散刷新的缺点是:将刷新操作和存/取操作一起作为一个周期,导致了周期变长,系统速 度下降。 集中刷新的缺点是:在再生周期的末尾进行刷新操作,虽然不会对前期的存/取操作有干扰 ,但是末尾这一整片的时间,CPU都不能对其进行操作,变成了死时间,降低了系统工作的效 率。 异步刷新则是克服了以上两种方式的缺点,将死时间降低的同时,又不影响系统速度,而 且如果把刷新操放在译码阶段,由于此时CPU并不对存储矩阵进行操作,即可大大节省间,具体如图3所示:

(1.2)静态随机存取存储器(SRAM)

(1.1.1)基本原理

请查阅教材,需要对双稳态电路和NMOS,PMOS性质有一定了解,这里不细说(想了解的请私信我,408复习该知识点不要求)。

(1.1.2)性能指标

#存取速度

因为SRAM的存储元是由6个MOS管构成的双稳态电路,所以并不会像DRAM一样要定 时刷新,而且也不是破坏性读出,数据读取之后源数据是不受影响的,所以在存取速度这一块 ,SRAM可以说是完胜DRAM的,SRAM的存取速度可以达到DRAM的8~16倍,但是,价格也 是DRAM的8~16倍,功耗也是如此,并且,由于SRAM是采用六晶体管构建的存储元,单位体 积内,SRAM的存储元数量是不如DRAM的,但是胜在速度快,所以一般来说,SRAM是充当 CPU和主存(DRAM)之间的高速缓冲器(Cache)。

(1.3)补充内容

(1.3.1)DRAM的地址线复用技术(了解就行)

如果要对地址0000111100001111进行存取操作,我们先将它发送至译码器,因为DRAM 的存储容量较SRAM是大了许多的,故存储元数量也是巨大的,如果把这16位地址一股脑地发 到译码器,译码器就得有2^16根片选线,这显然要命,所以我们这里把地址拆开来,拆成两个 8位,分批发送,那么就只要2 ^8根线,就可以了这就叫地址线复用技术。

PS:后续还会定期继续更新内容,直到考研结束!(想继续和我一起讨论的点波关注哦),我主要是想定期督促自己!哈哈!

》》2021/6/10于赣州

下一期内容:只读存储器

最后

以上就是坦率帽子最近收集整理的关于考研408复习日志之计算机组成原理-随机存取存储器RAM基本概念考研408复习日志的全部内容,更多相关考研408复习日志之计算机组成原理-随机存取存储器RAM基本概念考研408复习日志内容请搜索靠谱客的其他文章。

发表评论 取消回复