准备工作

首先在matlab下的simulink中创建测试模块,通过测试模块产生信号,再传送到FPGA。FPGA处理后将信号无处理传送回matlab。

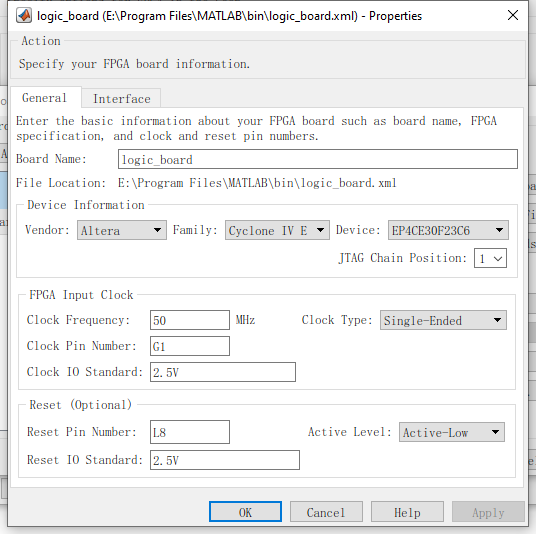

首先创建板子信息

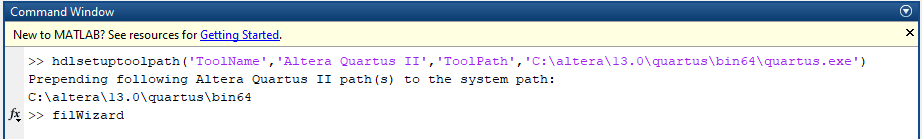

根据本机软件安装地址修改对应的ToolPath,ToolName是根据软件固定好的;

xilinx ISE的示例如下

hdlsetuptoolpath(‘ToolName’,‘Xilinx ISE’,‘ToolPath’,‘C:Xilinx14.2ISE_DSISEbinnt64’)

Xilinx Vivado的如下

hdlsetuptoolpath(‘ToolName’,‘Xilinx Vivado’,‘ToolPath’,‘C:appsVivado2013.4-mw-0Winbinvivado’)

altera的如下

hdlsetuptoolpath(‘ToolName’,‘Altera Quartus II’,‘ToolPath’,‘C:Altera12.0quartusbin64’)

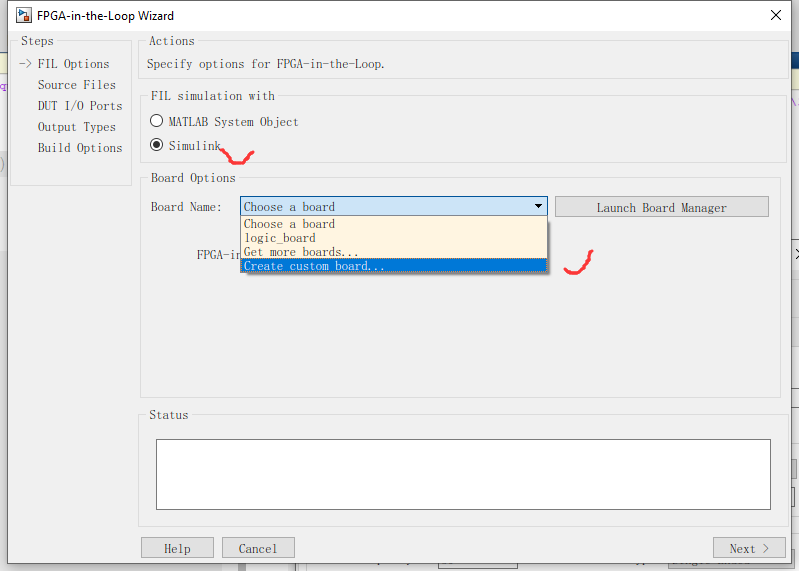

运行filWizard

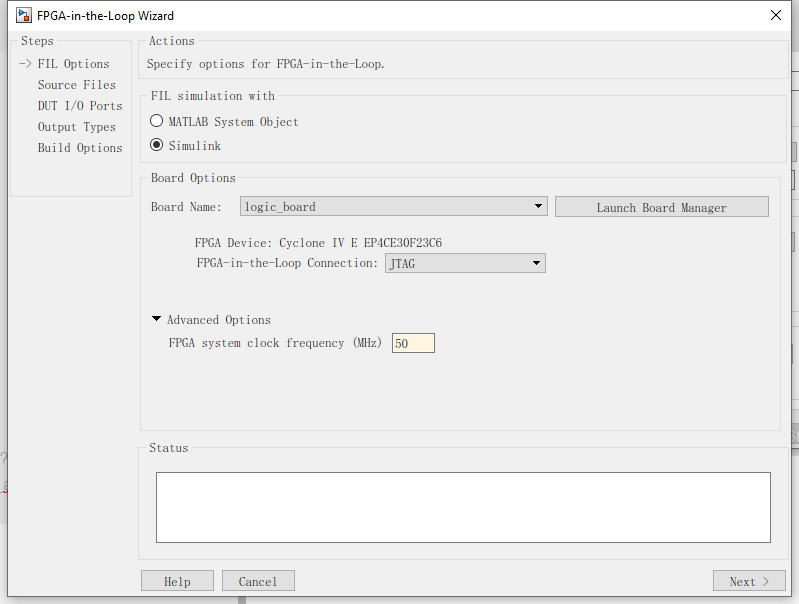

然后创建板子信息,一步步往下,这里选择JTAG方式调试(也可以是网络方式,最后有提及),这里板子信息为AC6102开发板;

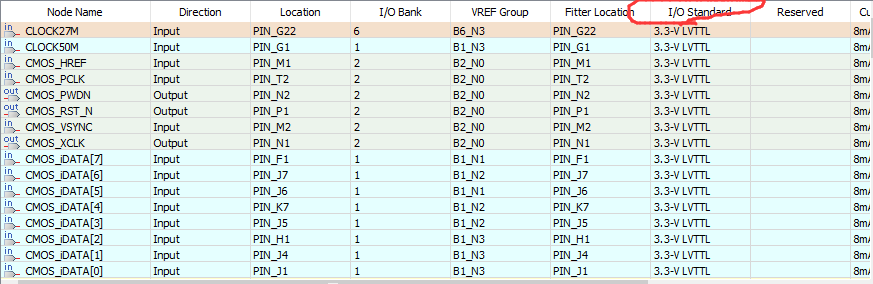

电平标准的名字不能随便填,可以是LVCMOS33这样子,具体参看自己的开发板工程中引脚配置的电平标准名字;

配置好之后板子信息如下所示:

选择创建好的一个板子

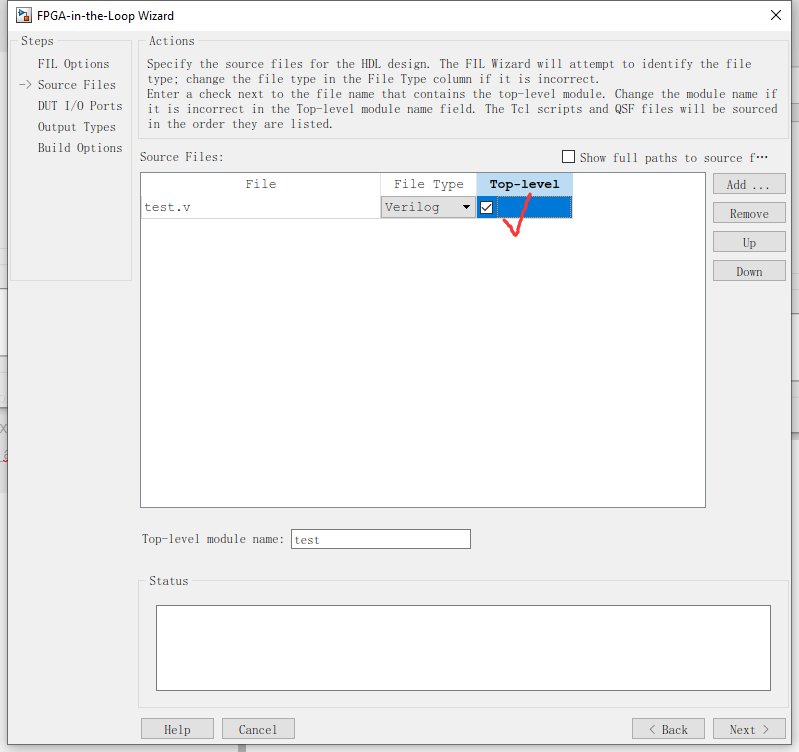

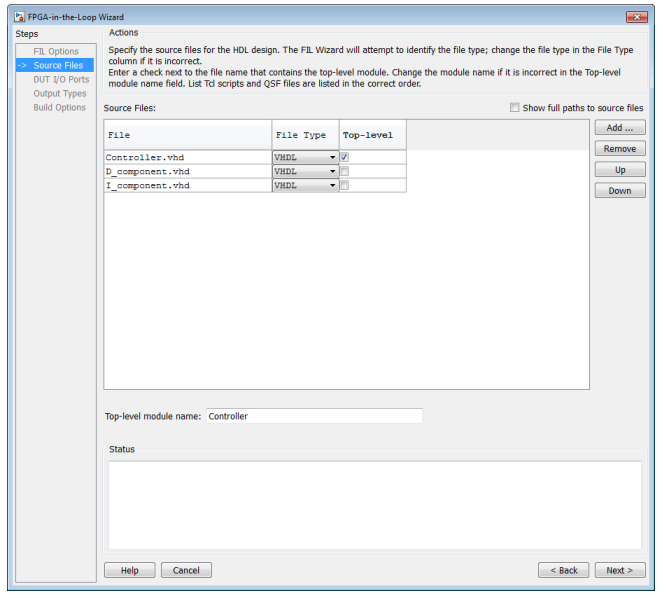

添加一个写好的.vhd或者.v文件,并设置顶层文件,多个文件同时载入也可以

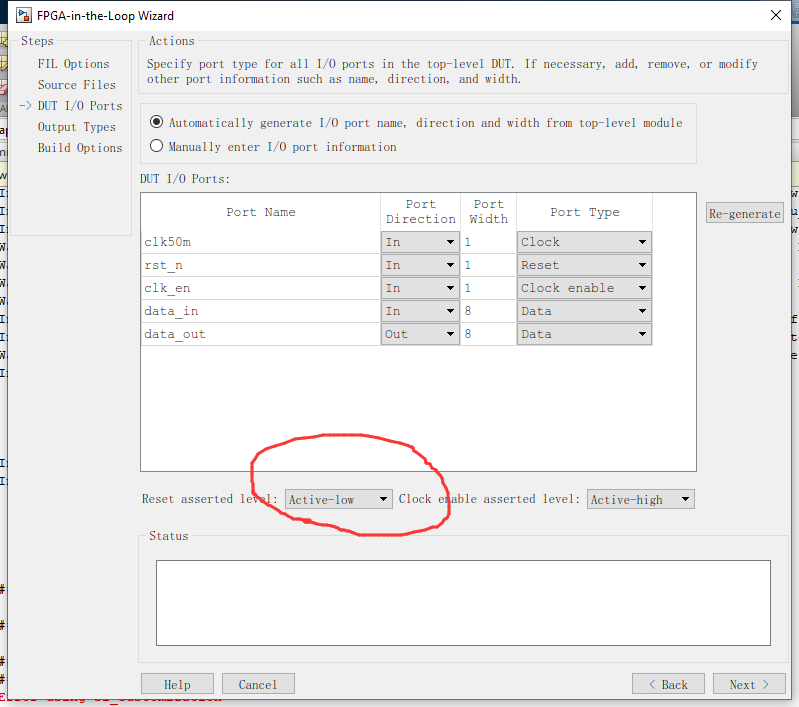

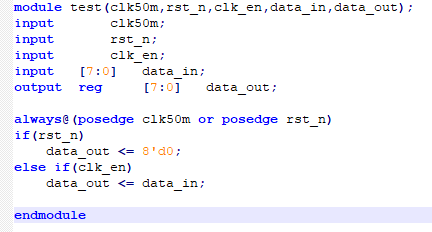

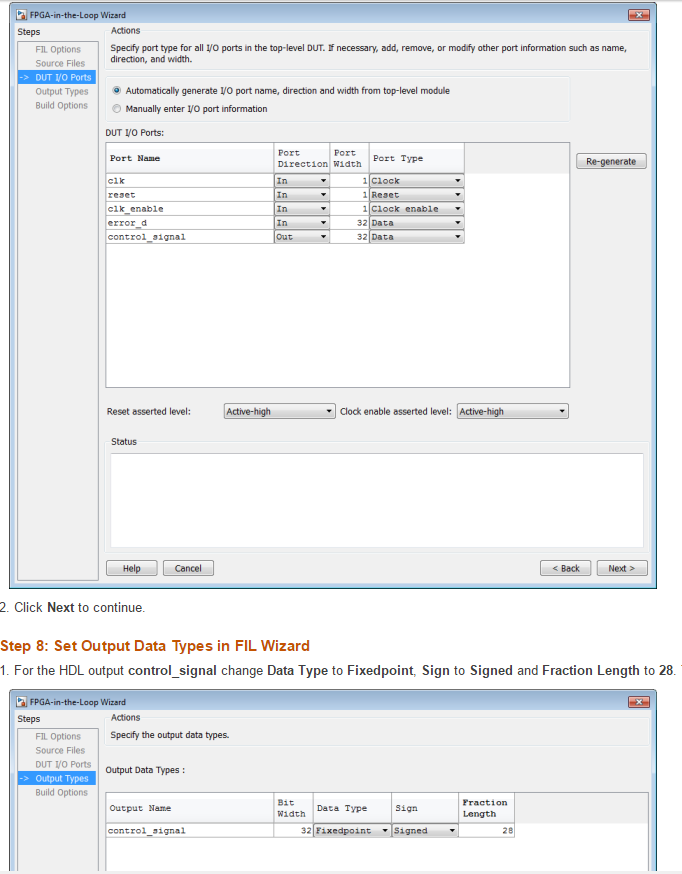

配置好IO口的信息,注意simulink运行后给的复位信号一直是低电平,并且一直处在这个状态,因此如果代码中是!rst_n复位的,那么simulink运行之后,电路状态会一直处在复位的逻辑处理当中。即便如下图1改动红圈内状态也没有作用;所以为了程序运行之后不处于复位逻辑,可以如图2这么写

图1

图2

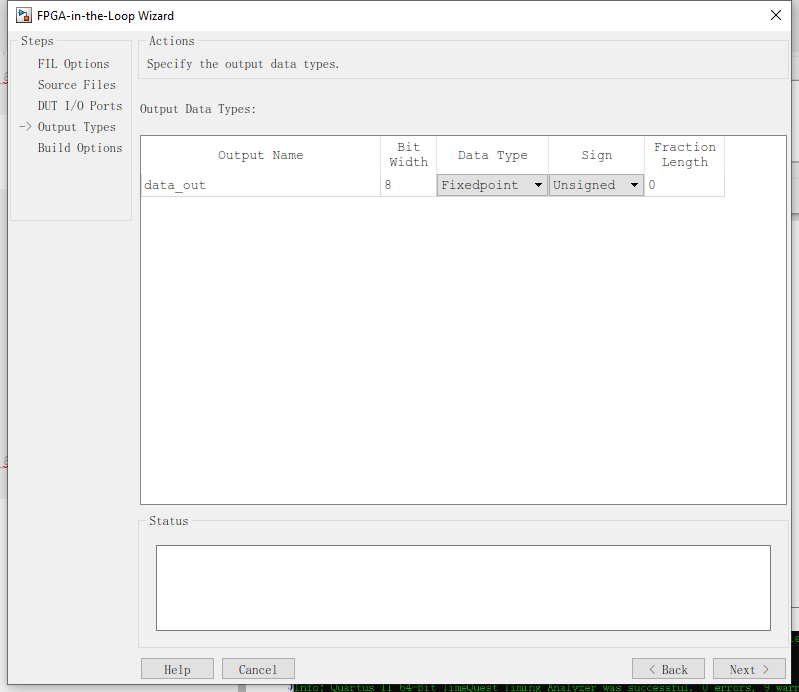

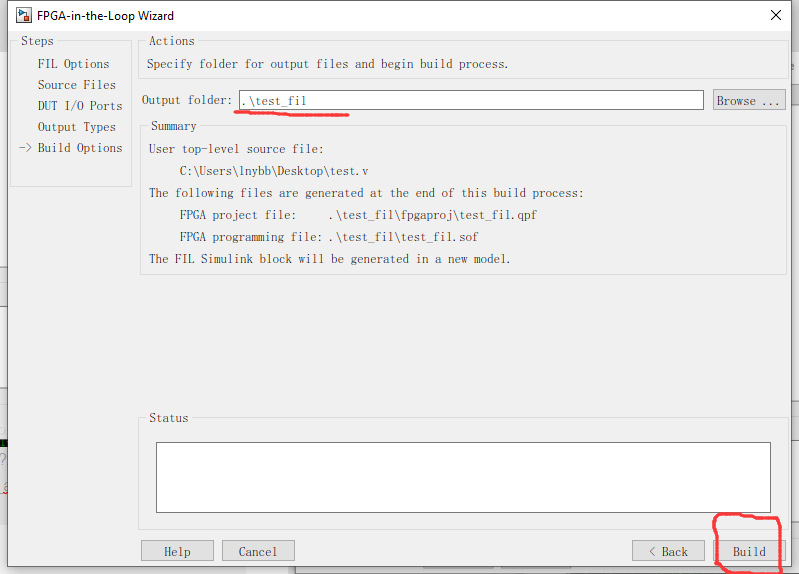

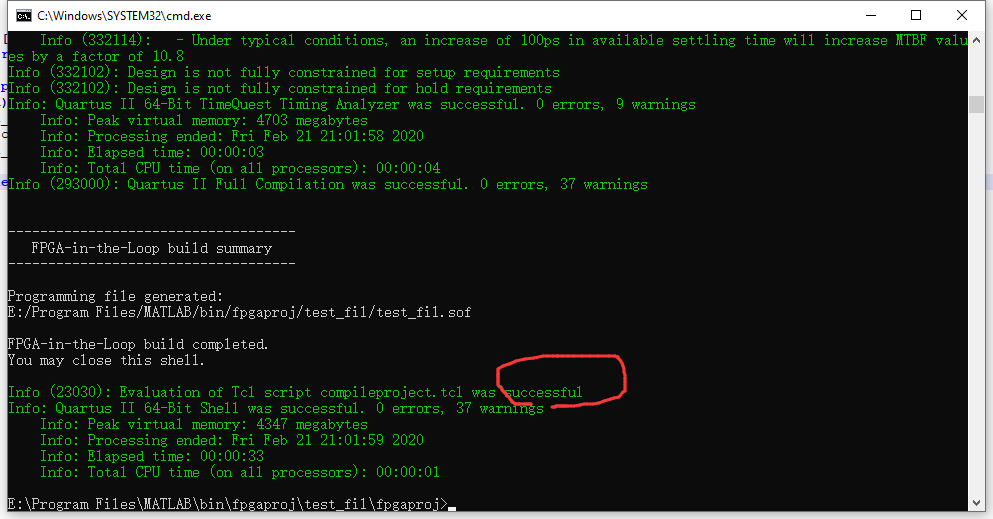

输出路径可以是默认的,之后点击编译,如果matlab命令窗口报错可能是文件语法错误,接着会弹出cmd窗口自运行TCL脚本,板子信息设置错误可能导致这一步出错,运行到最后会显示成功界面

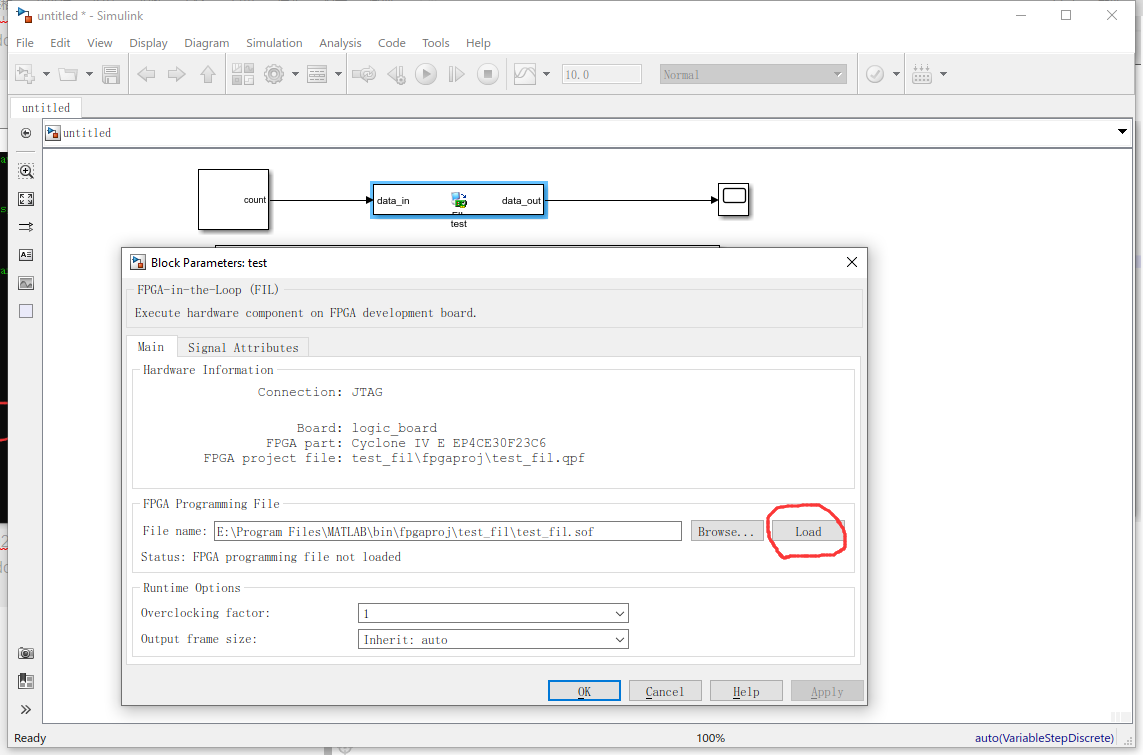

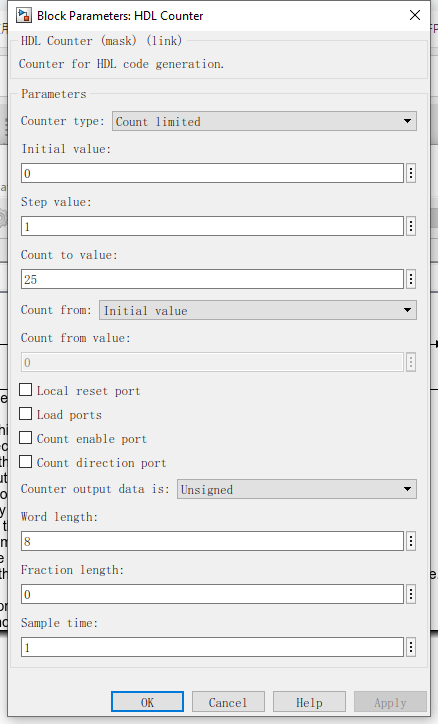

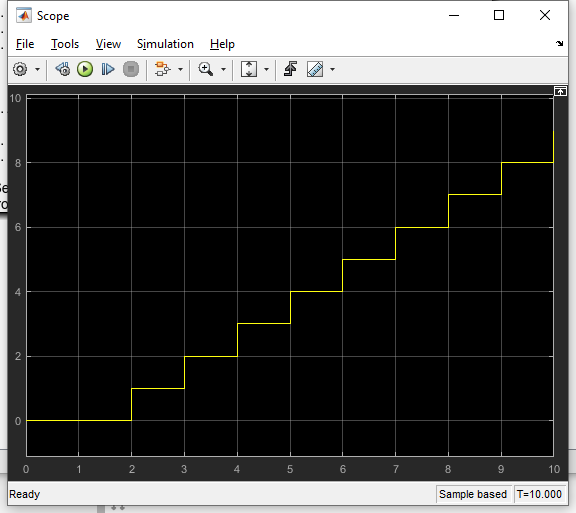

接着在生成的模型中加入测试源和示波器,这里就是简单的计数器,记得双击test模块load sof文件进入fpga,之后再Run simulink;

最终运行结果

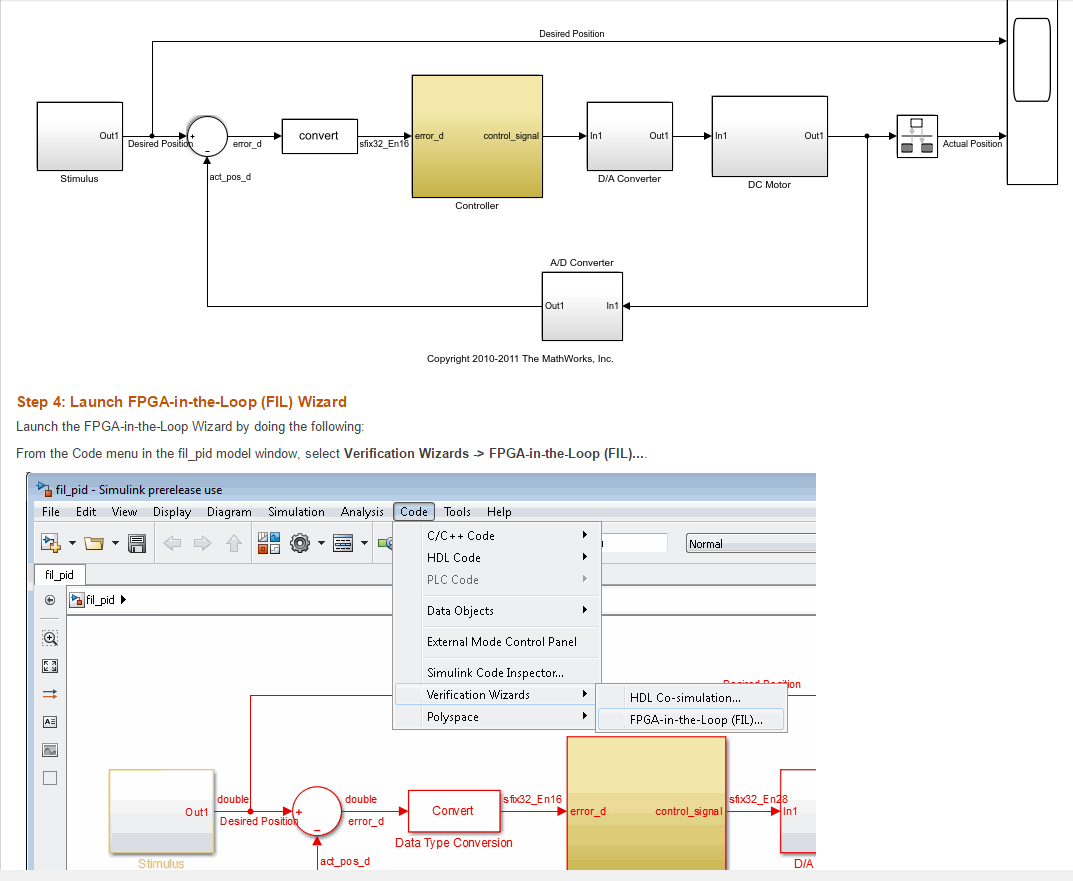

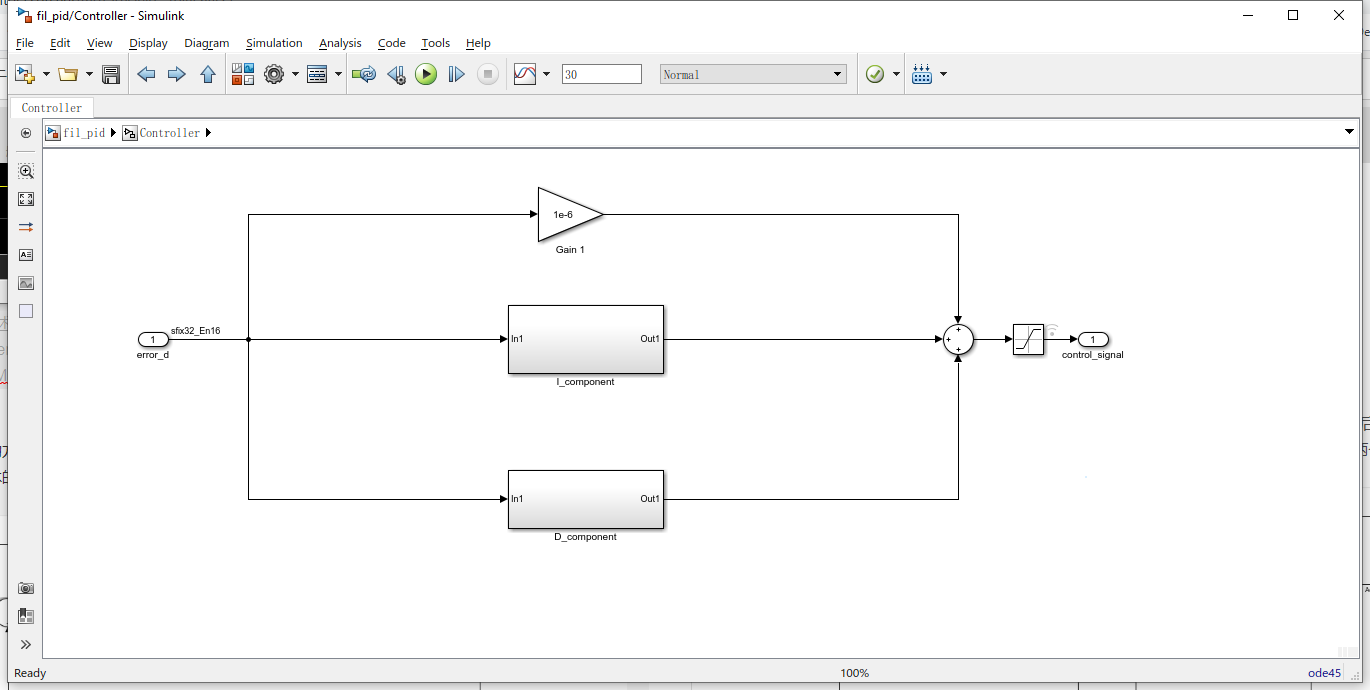

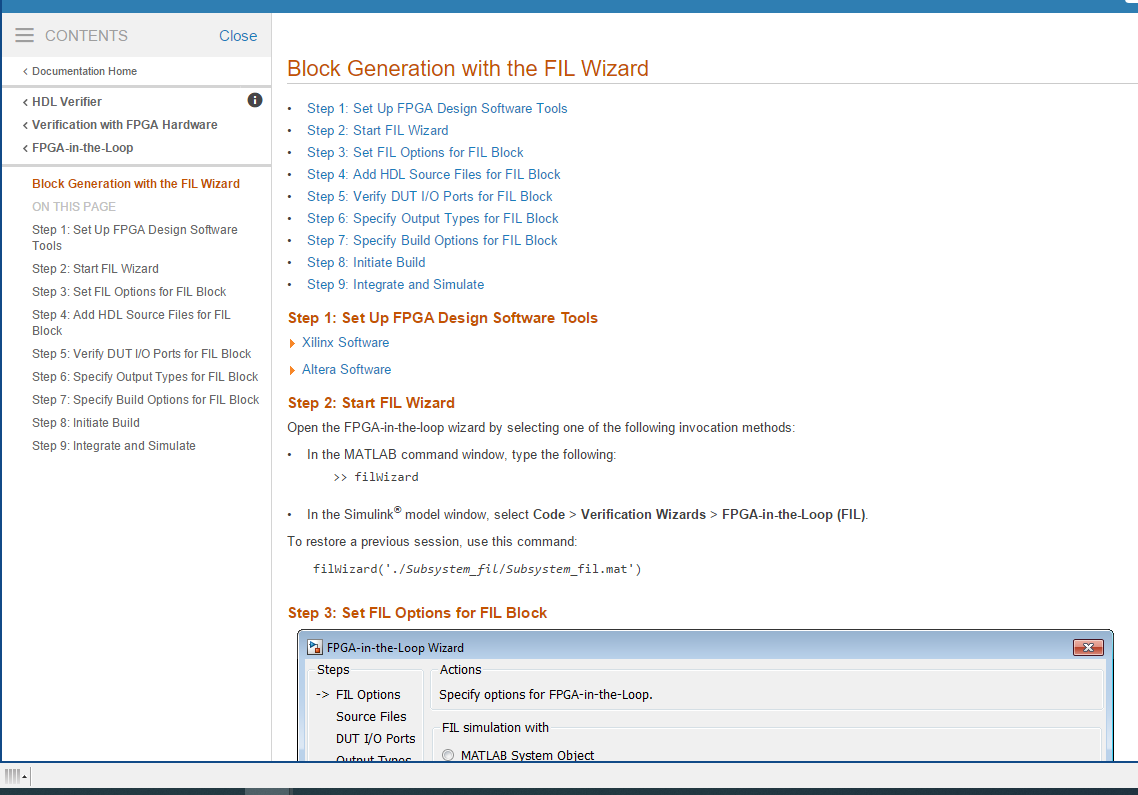

具体进行硬件在环的方式还可以通过先建立simulink模块,然后在code这里点击进入在环仿真,后面的步骤就是一样的,加入具体的硬件描述语言文件进行,这里比如是一个Controller顶层模块,里面还有两个模块;

所以加入的文件是这样子的

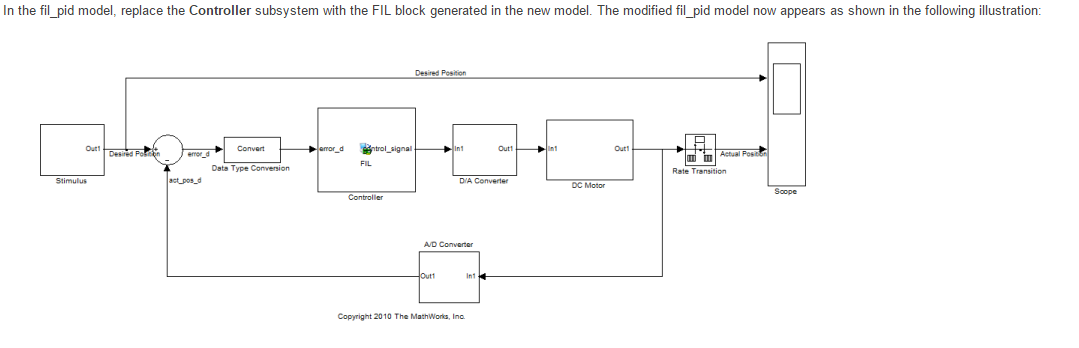

最后用生成的FIL 模块替换之前的模型即可

具体文档参考matlab的;

最后

以上就是淡然小海豚最近收集整理的关于基于matlab的fpga硬件在环仿真准备工作的全部内容,更多相关基于matlab内容请搜索靠谱客的其他文章。

发表评论 取消回复