基于“

PC+

运动控制器”结构的开放式机器人运动控制系统能够充分利用

PC

开放程

度高、通用性好、处理能力强等特点以及运动控制器运算速度快、实时性能好、控制能

力强等特点,因此得到较快发展,成为目前的研究热点。但目前采用此种结构的开放式

机器人运动控制系统中,不管是控制器供应商所提供的运动控制器或者是科研人员自主

设计的运动控制器,在通用性、软硬件可重构方面都存在一些问题,影响着机器人运动

控制系统的开放性。

因此,本文通过研究开放式机器人运动控制器的结构特点,制定了基于

DSP+FPGA

的开放式机器人运动控制器的总体设计方案。根据所制定的设计方案,设计并实现了基

于

DSP+FPGA

的开放式机器人运动控制器,并研究了基于开放式机器人运动控制器的

运动控制核心算法。

本文通过充分利用

DSP

的高速数字信号处理能力和

FPGA

的强大并发控制能力以

及丰富的逻辑资源来使运动控制器获得较高的运算与控制能力。通过充分利用

FPGA

的

逻辑编程能力来代替集成芯片以及实现逻辑连接,实现运动控制器的软硬件可重构,提

高机器人运动控制器的开放性。并通过研究曲线拟合预处理技术以及速度前瞻技术来提

高运动控制器的控制效率,实现高速运动控制。

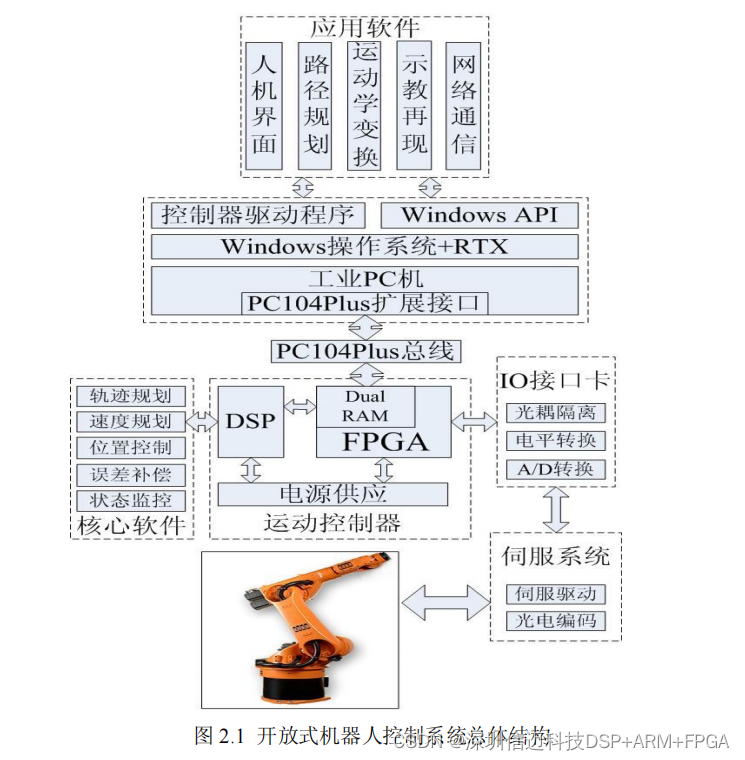

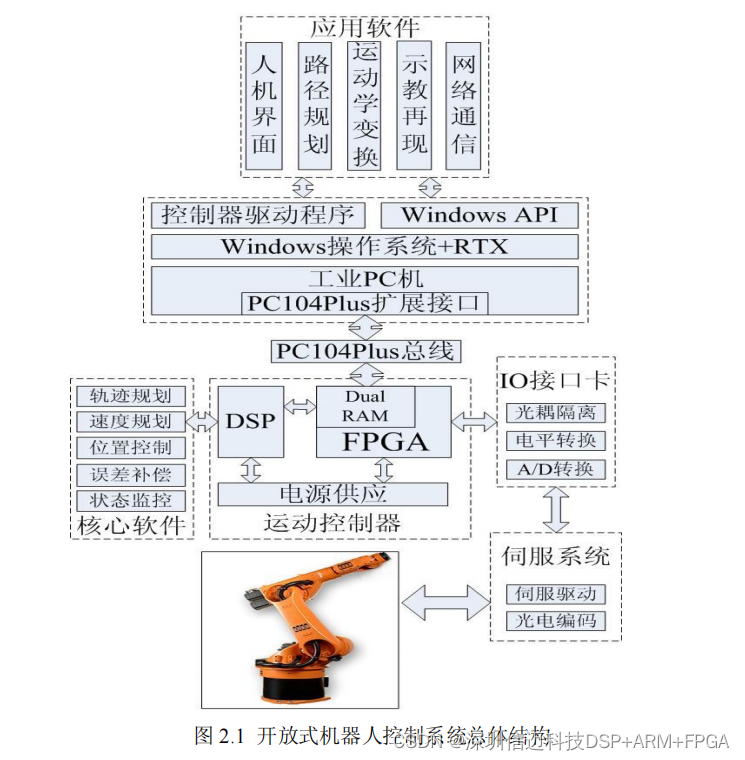

本文所设计的机器人运动控制器应用于开放式机器人控制系统中,与工业

PC

、伺

服系统、机器人本体等组成开放式机器人控制系统。控制系统结构形式为

PC+

运动控制

器,其中

PC

主要实现人机界面、参数配置、路径规划、机器人运动学正变换与逆变换、

多机通信等功能。而基于

DSP+FPGA

的运动控制器则主要完成实时性要求较高的轨迹

规划、速度规划、位置控制、以及状态反馈等任务。

PC

与运动控制器采用具有开放性

的

PC104Plus

总线进行通信,通过双端口

RAM 进行数据共享与同步。系统总体结构如

图

2.1

所示。其中

I/O

接口卡主要完成光耦隔离和电平转换,保护运动控制器不因来自

伺服系统的脉冲电压而受到损害。伺服系统实现对机器人运动关节的伺服驱动和光电编

码反馈,为运动控制器提供实时的机器人运动关节速度和位置状况。

2.5.2

基于

DSP+FPGA

的开放式机器人运动控制器总体结构

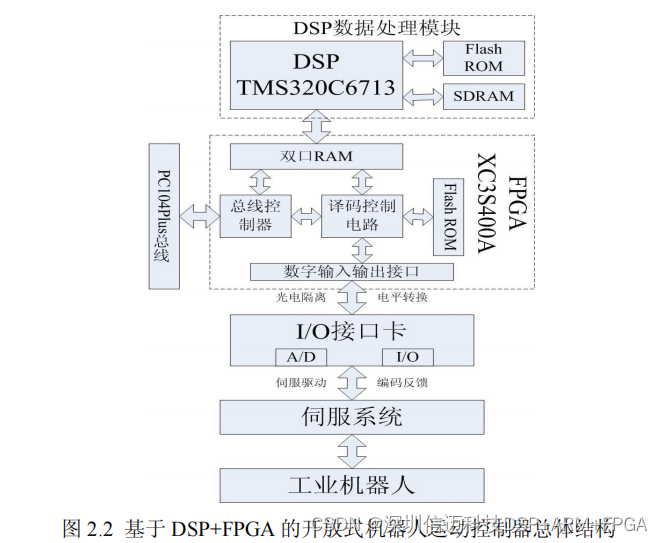

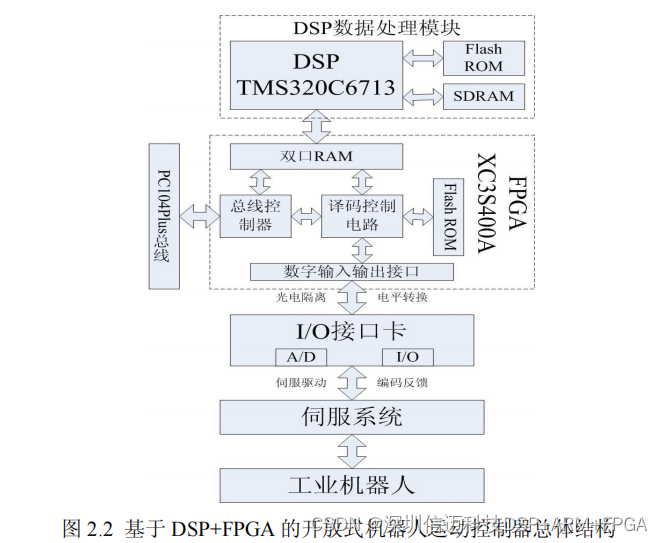

作为开放式机器人控制系统的核心控制模块,运动控制器承担着对各执行机构的实

时控制,状态反馈等任务。运动控制器必须能够满足运动控制的定位控制精度、速度调

节的性能等重要指标。经过反复对比论证,本课题所设计的开放式机器人运动控制器以

TI

公司的高速浮点型

DSP

芯片

TMS320C6713

作为控制计算的核心处理器完成轨迹规

划、速度规划、位置控制等任务,以

Xilinx

公司的高性能、大容量

FPGA

芯片

XC3S400A

实现各种输入输出接口、逻辑控制、脉冲接收器、脉冲发生器、地址译码、伺服系统控

制和功能扩展等功能。系统结构采用运动控制器核心板

+I/O

接口卡形式。运动控制器核

心板由

DSP

数据处理模块、

FPGA

外围电路、

PC104Plus

接口电路以及电源供应电路等

组成,实现所有与工业

PC

通信、运动控制计算以及伺服控制功能。其中双端口 RAM

以及

PC104Plus

控制电路分别采用

Xilinx

公司提供的已有

IP

核,由

FPGA

芯片实现。

I/O

接口卡主要是实现总线电路选择、光电隔离以及电平转换等功能,保护运动控制器不受

外部系统脉冲电压信号损害,提高系统抗干扰能力。运动控制器核心板与

I/O

接口卡采

用并行数据接口进行高速数据通信。控制器总体结构如图

2.2

所示:

系统启动后,在工业

PC

上计算出的运动控制指令及参数通过

PC104Plus

总线下载

到运动控制器的双端口

RAM

中,

DSP

模块从双端口

RAM

中获取来自

PC

的指令后,

启动内部的插补运算模块、加减速控制模块等进行插补运算与速度控制,运算结果由位

置控制模块保存至结果队列并定期从结果队列取出数据写回双端口

RAM

中,

FPGA

从

双端口

RAM

中读取插补运算结果,将位置控制命令转换为相应脉冲数及脉冲方向后,

进行细分处理,经过高速光耦,差分转换器,输出隔离后的差分信号到伺服系统,驱动

电机运动,并从位置编码器读取运动结果,保存到双端口

RAM

中供

PC

获取。最后

PC

定时从双端口

RAM

中获取各种状态并通过人机界面显示出来。所有的输入信号(通用、

专用

I/O

信号,编码器信号)均通过光耦隔离,隔离后的信号再输入到

FPGA

进行检测、

处理。

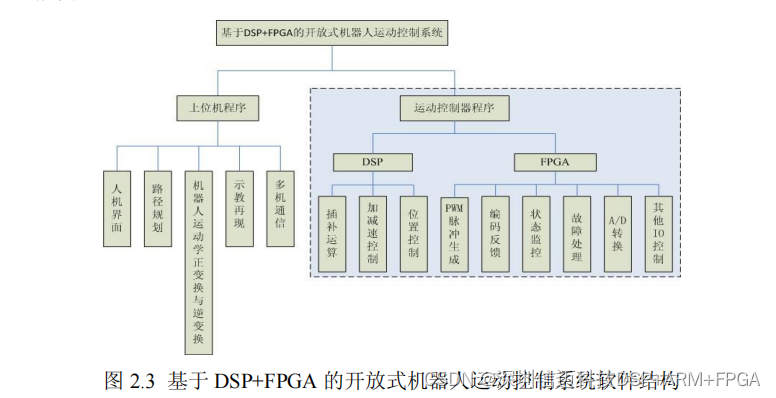

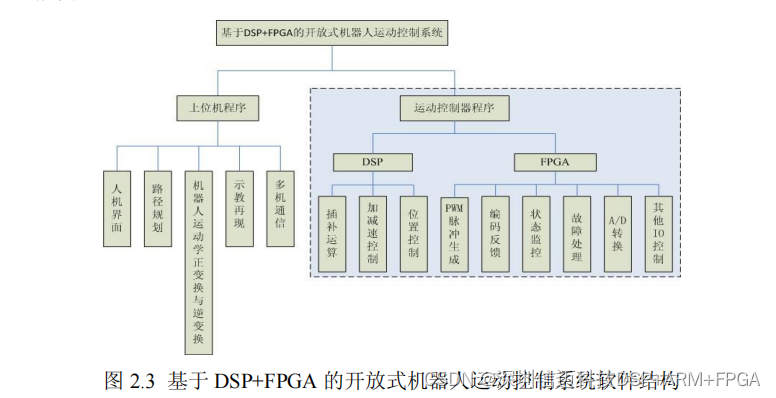

2.5.3

基于

DSP+FPGA

的开放式机器人运动控制器软件结构

基于

DSP+FPGA

的开放式机器人运动控制系统由上位机

PC

和下位机运动控制器两

部分组成。上位机主要实现一些实时性要求不太高的功能,主要包括人机界面、路径规

划、机器人运动学正变换与逆变换、示教再现、多机通信等功能。而下位机则主要实现

实时性要求较高的功能。主要包括插补运算、加减速控制、位置控制、

PWM

脉冲生成、

编码反馈、状态监控、故障处理、

A/D

转换、其他

IO

控制等。本设计采用模块化设计,

根据所要实现的功能对控制器软件结构进行模块划分。基于

DSP+FPGA

的开放式机器

人运动控制系统软件结构如图

2.3

所示,其中右侧阴影部分即为基于

DSP+FPGA

的开放

式机器人运动控制器软件结构。在控制器软件结构中,插补计算、加减速控制、位置控

制等数据运算全部在

DSP

实现,

PWM

脉冲生成、编码反馈、状态监控、故障处理、

A/D

转换、其他

IO

控制等所有控制任务全部在

FPGA

中实现。这样充分利用了

DSP

数据与

程序分离的哈佛结构和流水线操作以及特殊的乘法器结构所带来的强大数据处理能力

以及

FPGA

高主频、低功耗和强大的并发控制能力,使系统获得更快的速度和更强大的

数据处理能力。

2.5.4

开放式机器人运动控制器开放性与高速控制的实现

开放式机器人运动控制器与封闭式的机器人运动控制器相比较,其突出的特点就是

结构灵活,具有软硬件可重构功能,可方便地对系统软件和硬件结构进行修改和升级,

使得系统具有良好的开放性。另外,由于机器人运动控制器主要完成一些实时性要求较

高的任务,因此开放式机器人运动控制器必须具备较好的实时性。本设计中通过如下软

硬件方面的设计来保证开放式机器人运动控制器的开放性与高速控制特性:

(1)

运动控制器开放性的实现:机器人运动控制器开放性的最主要特征是软硬件可

重构。硬件的可重构,指的是对硬件结构可以方便作出修改、替换与升级等。硬件的可

重构,可通过采用

FPGA

编程来最大限度地代替分立元件来实现。目前在开放式运动控

制器的设计中,一般只使用

FPGA

来实现逻辑连接和地址译码。其他大部分功能还是由

独立芯片去实现。在本设计中通过充分利用

Xilinx FPGA

的

IP

核实现了双端口

RAM 和

PC104Plus

总线控制器,并且实现了对双端口

RAM

的地址译码和访问仲裁,以及逻辑

连接控制。同时,利用

FPGA

通过分频电路实现

PWM

脉冲发送电路,通过四倍频技术

实现脉冲编码信号的采集,通过

FPGA

实现

A/D

信号的转换,完成了伺服驱动与位置反

馈等功能。最后,通过

FPGA

控制通用

I/O

总线,实现了对输入状态信号的采集以及输

出信号的管理。由上述可知,本设计中通过

FPGA

编程实现与

PC

的高速通信以及对伺

服系统的控制与状态监控,在需要对硬件结构作出调整是只需简单修改

FPGA

的程序,

既减少了大量分立元件的使用,降低了电路的复杂度,提高了控制器的可靠性与稳定性,

同时也实现了硬件的可重构。软件的可重构,则可通过采用模块化设计的思想,将需要

实现的功能划分为各个独立任务模块,各模块之间在保证实时性的前提下,保持一种松

耦合的关系,使得对运动控制器各部分的功能可以方便作出修改而对其他部分不产生较

大影响,较好地实现了软件的可重构。通过对运动控制器的软硬件可重构的实现,使得

运动控制器具有较高程度的开放性。

(2)

运动控制器高速控制的实现:由于

DSP

数据与程序分离的哈佛结构和流水线操

作以及特殊的乘法器结构,使得

DSP

相对于其他微处理器来说具有更高的数据处理能

力和更快的数据处理速度。而

TMS320C6713

又是

TI

公司

C6000

系列高性能浮点型

DSP

芯片,具有高达

300MHz

的工作频率,最大处理能力可以达到

2400MIPS

,其浮点运算

能力使得系统可以获得较高的计算精度。而

Xilinx

公司的

XC3S400A FPGA

芯片也有高

达

200MHz

的工作频率,有利于提高系统运行速度。另外

PC104Plus

是专为

PCI

总线设

计的一种高速的开放式

PC

总线,可以连接高速外接设备,也具有非常高的数据传输速

度。将

DSP

和

FPGA

集成在同一板卡上使得两者之间数据传输直接快速。这一系列的

设计使得运动控制器在硬件结构上具有高速高精度的特性。而在软件的设计上则通过预

处理算法与速度前瞻算法等保证了在允许误差范围内实现运动轨迹段间的高速平稳过

渡,通过在速度规划算法中引入误差补偿来保证控制器的控制精度。通过以上软硬件方

面的设计,来充分保证运动控制器的高速控制特性。

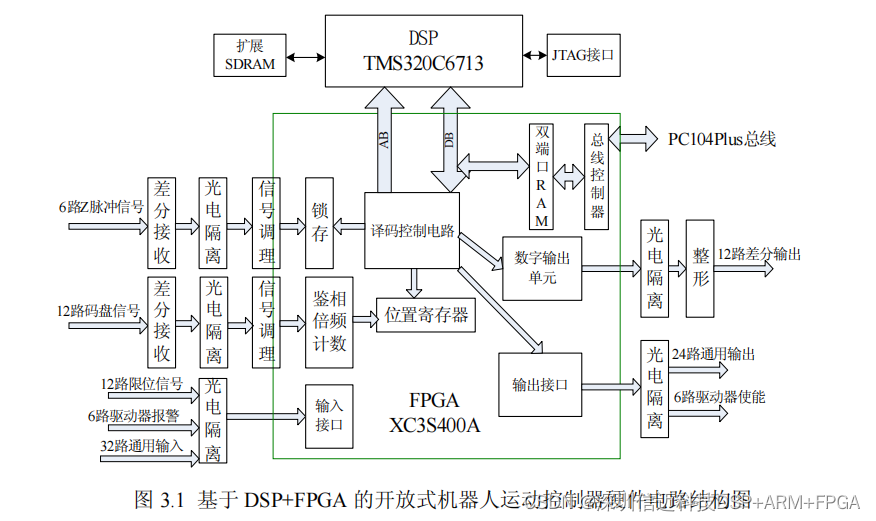

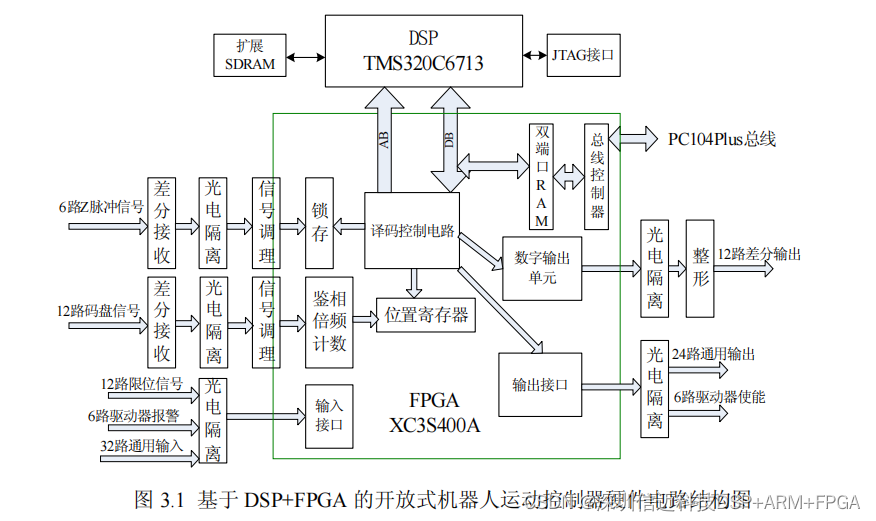

基于前文的分析,本课题所设计的运动控制器在机器人运动控制系统中主要完成实

时性要求较高的插补运算、位置控制、速度控制、伺服电机驱动以及状态反馈等任务。

控制器以

DSP+FPGA

为处理核心,以运动控制器核心板

+I/O

接口卡形式为系统结构,

DSP

和

FPGA

全部集成在核心板上,

I/O

接口卡仅实现光耦隔离、

A/D

转换和电平转换。

采用

PC104Plus

总线与工业

PC

进行数据交换。使用

FPGA

代替各种逻辑连接的分立元

件并通过

FPGA

的

PC104Plus

总线控制器

IP

核以及双端口

RAM IP

核代替

PC104Plus

总线控制芯片和双端口

RAM

芯片。核心板与

I/O

接口卡采用高速并行接口连接。运动

控制器需要控制的输入信号包括六路

Z

脉冲信号、

12

路码盘信号、

12

路限位信号、

6

路驱动报警器信号、

32

路通用输入信号等。运动控制器需要控制的输出信号包括

12

路

差分输出、

6

路驱动器使能信号以及

24

路通用输出信号等。根据实现功能的不同将运动

控制器硬件电路结构划分为

DSP

数据处理模块、

FPGA

外围电路模块以及电源电路模块

等,而

FPGA

外围电路模块又包含

PC104Plus

总线通信模块、伺服控制模块、

D/A

接口

模块、

I/O

接口模块等。运动控制器硬件电路结构如图

3.1

所示:

信迈支持DSP+FPGA运动控制方案设计。

最后

以上就是美丽寒风最近收集整理的关于基于DSP+FPGA高速运动控制器设计的全部内容,更多相关基于DSP+FPGA高速运动控制器设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复