Verilog HDL计数器设计(作业1)

目录:

- Verilog HDL计数器设计作业1

- 设计内容

- 信号定义

- RTL设计图

- Quartus RTL电路图

- 计数器波形仿真图

- 计数器代码

- 设计内容

- 信号定义

- RTL设计图

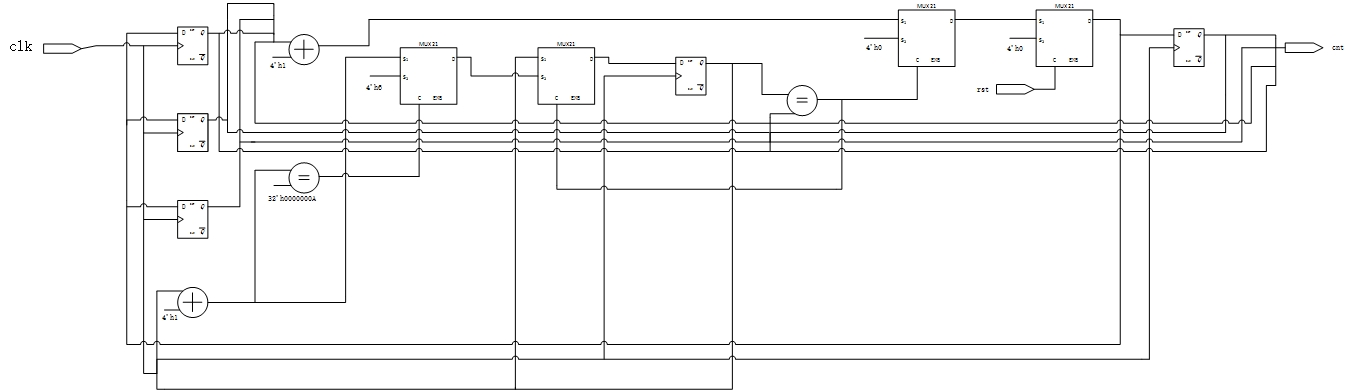

- Quartus RTL电路图

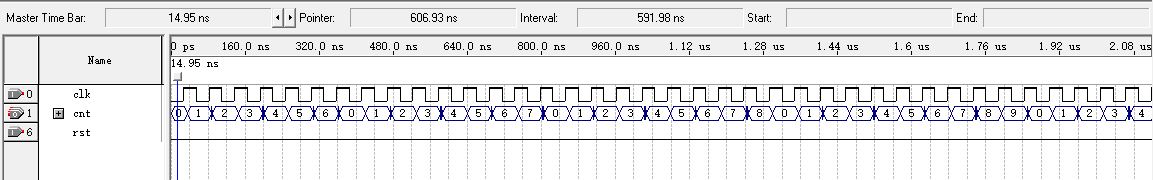

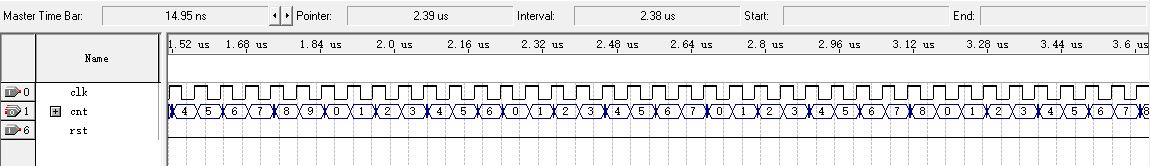

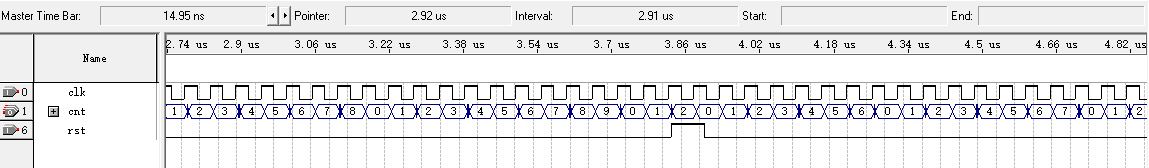

- 计数器波形仿真图

- 计数器代码

设计内容

设计一个计数器,该计数器在电路复位后会循环的从0值递增计数到最大值,计数最大值是一个循环变化的过程,计数器复位之后,第一次计数最大值是6,然后是7、8、9,然后计数最大值又变成6,如此往复循环,计数过程如下所示:

| 0 1 … 6 | 0 1 … 7 | 0 1 … 8 | 0 1 … 9 | 0 1 … 6 |

|---|

信号定义

| 信号名称 | 方向 | 位宽 | 说明 |

|---|---|---|---|

| CLK | 输入 | 1 | 输入时钟信号 |

| RST | 输入 | 1 | 输入复位清零信号,异步高电平有效 |

| Pipe | 输出 | 4 | 输出计数值信号 |

*RTL设计图

Quartus RTL电路图

计数器波形仿真图

计数器代码

module abc(cnt,rst,clk);

reg[3:0] length=4'D6;

input clk,rst;

output reg[3:0] cnt;

always @(posedge clk)

begin

if (rst)

cnt<=4'h0; //同步复位

else

begin

if (cnt[3:0]==length) //是否为6

begin

cnt[3:0]=0; //回0

length=length+1;

if (length==10)

length=6;

end

else

cnt[3:0]=cnt[3:0]+1;

end

end

endmodule最后

以上就是舒心铃铛最近收集整理的关于Verilog HDL计数器设计(作业1)Verilog HDL计数器设计(作业1)的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复