以hi3559av100为例。

首先从芯片的角度来了解视频输出的部分内容:

VDP(Video Display Processor)这是一个大的概念,官方给出的解释:VDP(Video Display Processor)模块主动从内存相应位置读取视频和图形数据,将视频层和图形层数据叠加后通过显示通道送出。

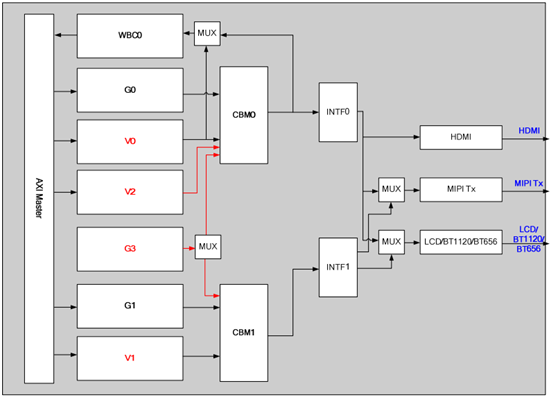

下图是VDP的总体框图,3559av100的引脚VO接口蓝色的字体HDMI,MIPI Tx,LCD/BT1120/BT656,其他的就是芯片内部的电路了,想看也看不见。

里面的术语解释:

CBM(CrossBar and Mixer,选通叠加器):视频层 V0/视频层 V2/图形层 G0/鼠标层 G3 叠加 CBM0、视频层 V1/图形层 G1/鼠标层 G3 叠加 CBM1。

VDP特点:

VO接口:

1. HDMI 2.0 输出接口:最大支持 2160P@60fps 输出。

2. MIPI Tx 输出接口:支持 1080P@60fpsYCbCr444/RGB 及以下时序显示。最大支持 2160@30fps(仅支持 YUV422 8bit)输出。

3. 数字输出接口:支持 ITU-R BT.1120 输出,支持 ITU-R BT.656 输出,支持LCD24bit 并行/16bit 并行/6bit 串行/8bit 串行输出。

视频层(Video Surface):V0、V1 和 V2 层。

图形层(Graphics Surface):G0、G1 和 G3 层。

回写通道(Write Back Channel):WBC0。

叠加特性:V0、V2、G0、G3 叠加、V1、G1、G3 叠加。

VDP 包含 2 个显示通道,每个通道有 1 个垂直时序中断以及 1 个低带宽中断。

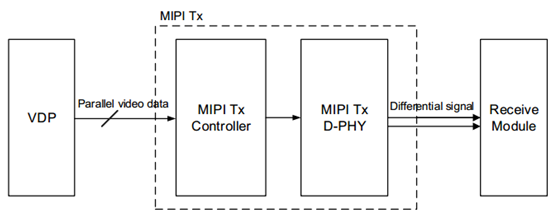

下面介绍一下3559av100的mipi_tx,下图是mipi_tx在系统的框图:

Tx D-PHY 支持 MIPI D-PHY ver1.2 协议,主要实现了物理层的传输规范。

Tx Controller 根据 MIPI DSI 和 CSI-2 协议要求对数据格式进行封装。

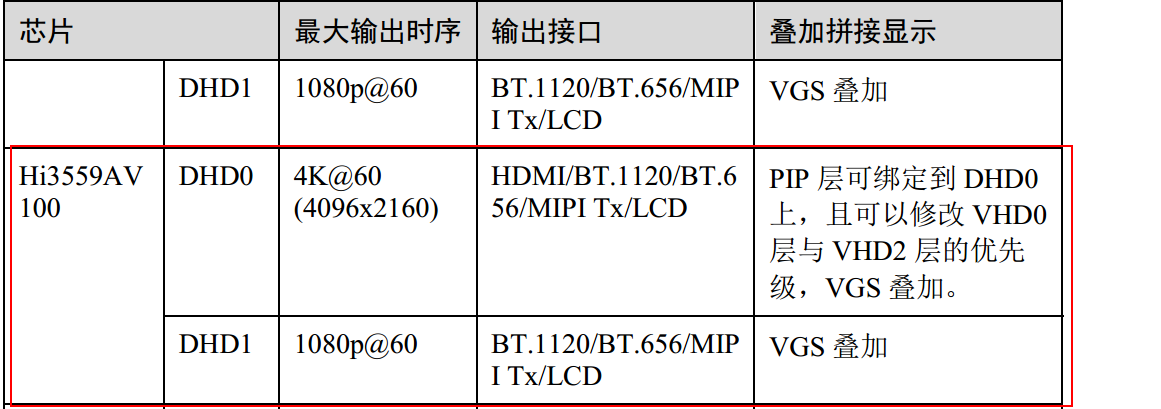

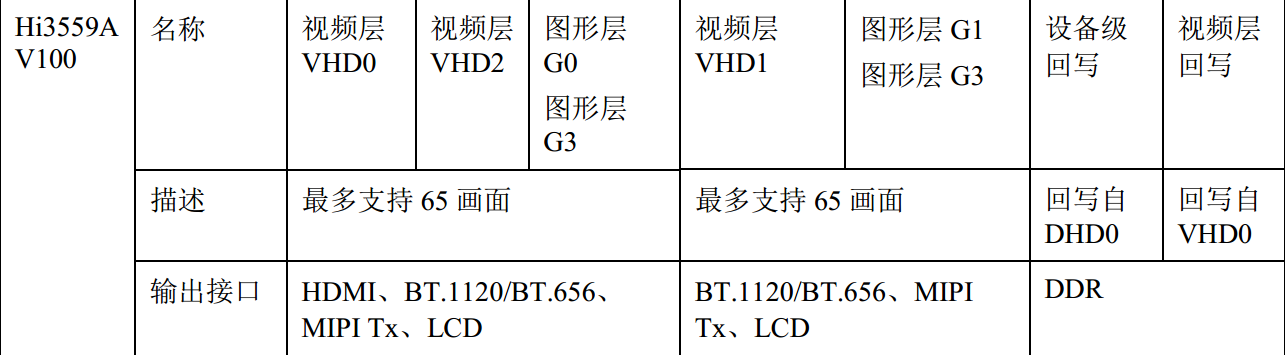

芯片支持的显示/回写设备、视频层和图形层

输出接口:

超高清显示设备DHD0----HDMI、BT.1120/BT.656、MIPI Tx、LCD

高清显示设备DHD1---- BT.1120/BT.656、MIPI Tx、LCD

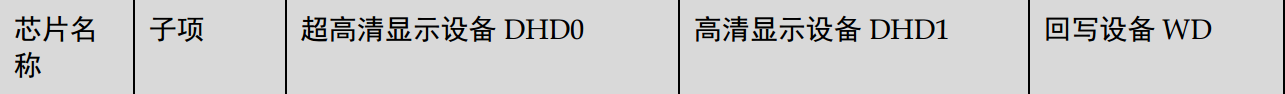

芯片支持的显示/回写设备、视频层和图形层:

Hi3559AV100 支持 3 个图形层(G0,G1,G3),G0 固定绑定到 DHD0 上,G1 固定绑定到 DHD1 上,即 G0 只能与 VHD0 叠加显示,G1 只能与 VHD1 叠加显示;G3 可动态绑定到 DHD0 或 DHD1,即 G3 或者与 VHD0 叠加显示,或者与 VHD1 叠加显示,G3 默认绑定在 DHD1 上。

Hi3559AV100ES/Hi3559AV100/Hi3519AV100/Hi3516CV500/Hi3516DV300 支持输入源图像是压缩数据(格式为段压缩,256Bytes 为一段),VO 会进行解压显示。

最后

以上就是任性时光最近收集整理的关于海思平台VO部分的介绍(视频输出)以hi3559av100为例的全部内容,更多相关海思平台VO部分内容请搜索靠谱客的其他文章。

发表评论 取消回复