为了避免空翻现象,提高触发器工作的可靠性,希望在每个CLK期间输出端的状态只改变一次,则在电平触发的触发器的基础上设计出脉冲触发的触发器

脉冲触发的触发器

- 1. 电路结构与工作原理

- 1.1 电路结构

- 1.2 工作原理

- 1.3 总结

- 2. 主从JK触发器

- 2.1 电路图

- 2.2 工作原理

- 2.3 特性表

- 2.4 小结

- 脉冲触发的动作特点

- 例题

1. 电路结构与工作原理

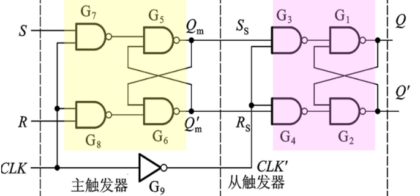

脉冲触发的SR触发器(主从SR触发器)(Master-Slave SR Flip-Flop),脉冲触发的SR触发器是由两个同样的电平触发SR触发器组成。

1.1 电路结构

由G 5 ~G 8 构成主触发器,由G 1 ~G 4 构成从

触发器,它们通过时钟连在一起,

C

L

K

从

=

C

L

K

′

CLK_{ 从 }=CLK'

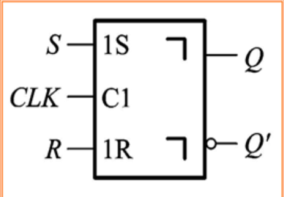

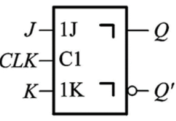

CLK从=CLK′,其图形符号如图5.4.2所示

1.2 工作原理

- 在 C L K = 1 CLK=1 CLK=1时,主触发器按S、R变化,而从触发器保持状态不变

- 在 C L K CLK CLK由1变成0(下降沿),主触发器保持,从触发器随主触发器的状态翻转,故在CLK的一个周期内,触发器的输出状态只可能改变一次

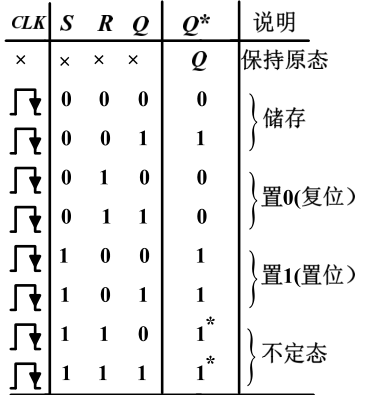

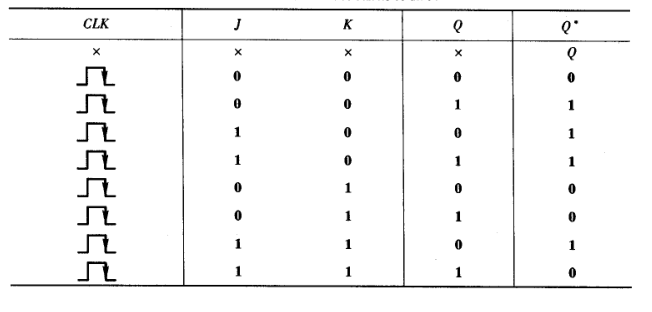

- 主从SR触发器的特性表如表所示

1.3 总结

主从RS触发器克服了同步RS触发器在 C L K = 1 CLK=1 CLK=1期间多次翻转的问题,但在 C L K = 1 CLK=1 CLK=1期间,主触发器的输出仍会随输入的变化而变化,且仍存在不定态,输入信号仍遵守 S R = 0 SR=0 SR=0.

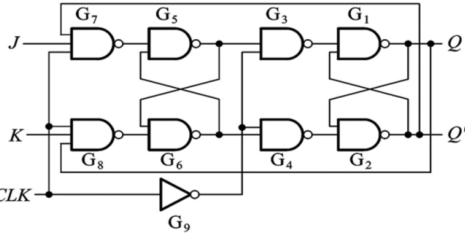

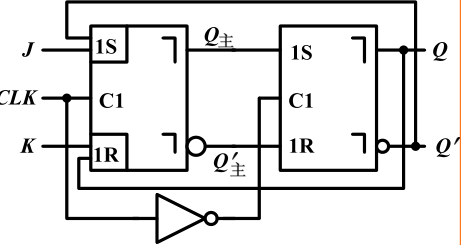

2. 主从JK触发器

为了使主从SR触发器在S=R=1时也有确定的状态,则将输出端 Q和 Q '反馈到输入端【注意Q接到了K,Q’接到了J】,这种触发器称为JK触发器(简称JK触发器)。

实际上这对反馈线通常在制造集成电路内部已接好

2.1 电路图

2.2 工作原理

- 对于 J K = 0 JK=0 JK=0的情况,依旧是10置1,01置0,00保持

- 当 Q = 1 , Q ′ = 0 Q=1,Q'=0 Q=1,Q′=0时,J被封锁,S被永远置0,当K=1时,Q被置0,当K=0时,Q保持1

- 当 Q = 0 , Q ′ = 1 Q=0,Q'=1 Q=0,Q′=1时,J被封锁,R被永远置0,当J=1时,Q被置1,当J=0时,Q保持0

- 对于 J K = 1 JK=1 JK=1时,分情况讨论:

- 当 Q = 1 , Q ′ = 0 Q=1,Q'=0 Q=1,Q′=0时,相当于 S = 0 , R = 1 S=0,R=1 S=0,R=1,置零Q*=0

- 当

Q

=

0

,

Q

′

=

1

Q=0,Q'=1

Q=0,Q′=1时,相当于

S

=

1

,

R

=

0

S=1,R=0

S=1,R=0,置零Q*=1

相当于对输出进行取反

2.3 特性表

2.4 小结

脉冲触发的动作特点

记录时钟周期内第一个脉冲到来时候的变化

- 分两步动作:第一步在CLK=1时,主触发器受输入信号控制,从触发器保持原态;第二步在CLK ‘到达后,从触发器按主触发器状态翻转,故触发器输出状态只能改变一次

- 主从JK触发器在CLK=1期间,主触发器只可能翻转一次,因为受到反馈回来的输出端的影响,故在CLK=1期间若输入发生变化时,要找出CLK’来到前的Q 状态,决定Q*

Q=0时,只允许J=1的信号进入主触发器

Q=1时,只允许K=1的信号进入主触发器

【所以考虑主触发器的情况要看当前的Q】

下面用一道例题说明

例题

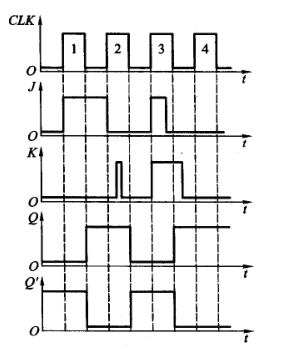

已知主从JK触发器的输入及时钟波形如图所示,试画

出输出端Q和Q’波形

- 第一个下降沿到达之前,输出端Q=0,K被锁定,J开始为0保持不变,后来J变为1,使主触发器的Q=1,所以下降沿到来时,从触发器Q=1

- 第二个下降沿到达之前,Q=1,J端被锁定,因为中途K=1,01置0,主触发器Q=0,后来00保持,所以下降沿到来时主触发器Q=0,所以从触发器Q置零

- 第三个下降沿到来前,Q=0,K端被锁定,先J=1,主触发器Q置1,后来J=0,主触发器Q保持1,所以下降沿到来时,从触发器的Q被置1

- 第四个的时候都为0,00保持不变

上述分析中,在第三个时钟周期,主从JK触发器的Q的变化并不是取决于电路下降沿到来时刻的输入,这样的问题称之为一次变化问题(就是一个时钟周期,主触发器的状态只能改变一次

最后

以上就是潇洒冬日最近收集整理的关于数电5_2——脉冲触发的触发器1. 电路结构与工作原理2. 主从JK触发器的全部内容,更多相关数电5_2——脉冲触发的触发器1.内容请搜索靠谱客的其他文章。

发表评论 取消回复