单口RAM IP练习

RAM在FPGA设计当中应用非常广泛,其种类有单口RAM、伪双口RAM、真双口RAM,但就实际项目开发而言,伪双口RAM应该是使用频率最多的。大家在学习实践的时候,也完全可以多做些对比,这样有更助于消化理解后加以灵活应用。

单口RAM顾名思义只有一个端口,显然这个端口只能在同一时刻进行读操作或者写操作,所以这就使得其在应用开发中具有很大的局限性,因为模块中读RAM数据和写RAM数据,本身是彼此独立的,很多情况下是需要同时去读写RAM的,单口RAM就很难完成这种设计需求。

双口RAM中又分成伪双口RAM和真双口RAM,首先它们都有两个端口,区别仅在于伪双口RAM一个端口只可以读地址中的数据,而另一个端口只可以写地址中的数据;但真双口RAM却不同,它的两个端口都可以去独立读写地址中的数据。

接着大家可以去想想看,显然真双口RAM为用户设计带来了最大限度的灵活性,伪双口RAM次之,单口RAM灵活性最低,但是项目工程中,一切设计都是围绕具体的需求展开,选择合适的就是最好的,并不是IP核灵活性越大就越好用,比如真双口RAM两个端口都可以进行独立的读写地址中数据的操作,那么如果用户在程序设计当中不做任何限制,必然有概率会出现两个端口同时向同一个地址写入数据,一个端口在写入地址中数据而同时另一个端口在读出该地址中数据等等,所以读写冲突可以说几乎是不可避免的。

下面先来介绍单口RAM的使用,单口RAM是三种RAM类型中功能最弱的一种,但是放在一些应用当中也很合适,因为不需要考虑太多问题更不容易出错,只要用户可以确定本模块中不会在同一时钟周期内同时进行读写数据操作即可。这里设计一个模块包含读写位宽均为8位,读写深度是32的单口RAM,先在32个地址空间依次写入0-31,再从32个地址依次读取数据,为了方便在Modelsim下观察,请把单口RAM中的端口输入数据ram_din、输出数据ram_dout、读写地址ram_addr、写使能信号ram_wea全部都例化出来,ram_en则是触发本模块动作的上游模块的使能信号,如表1为单口RAM IP练习的信号列表。

| 信号列表 | ||

| 信号名 | I/O | 位宽 |

| clk | I | 1 |

| rst_n | I | 1 |

| ram_en | I | 1 |

| ram_addr | O | 5 |

| ram_wea | O | 1 |

| ram_din | O | 8 |

| ram_dout | O | 8 |

表1 单口RAM IP练习设计中的信号列表

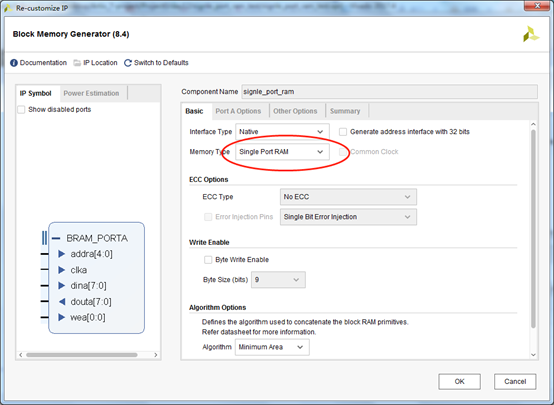

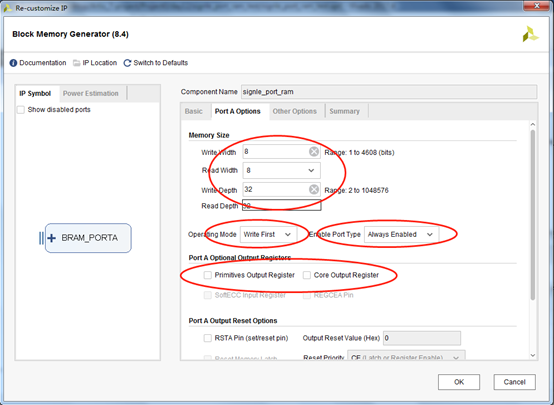

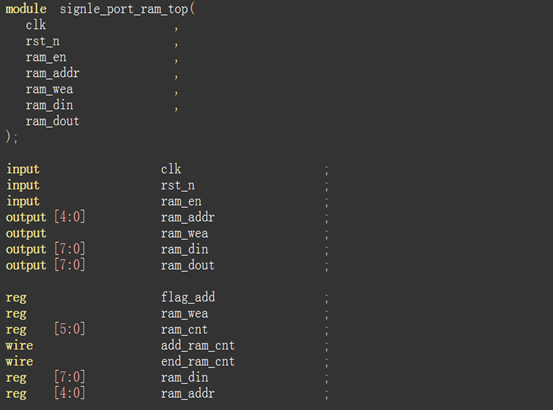

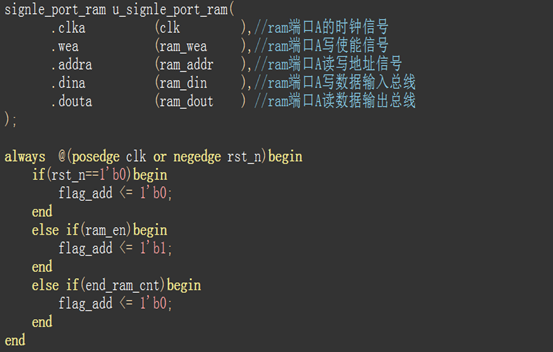

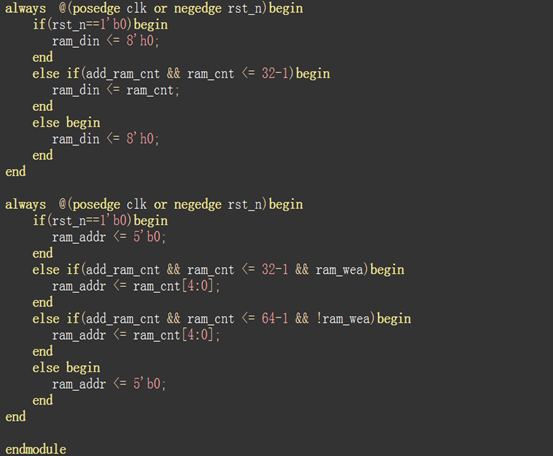

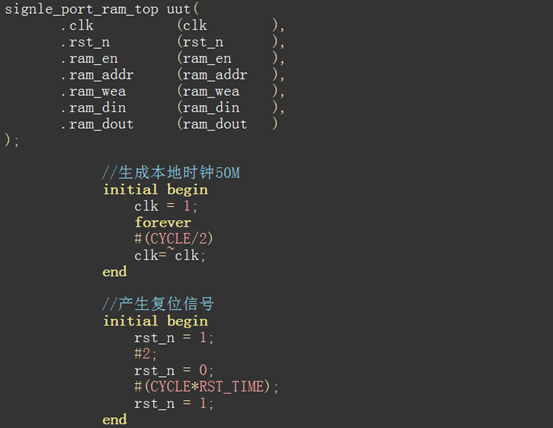

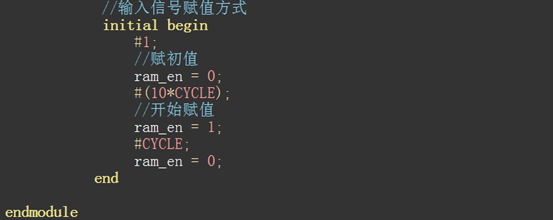

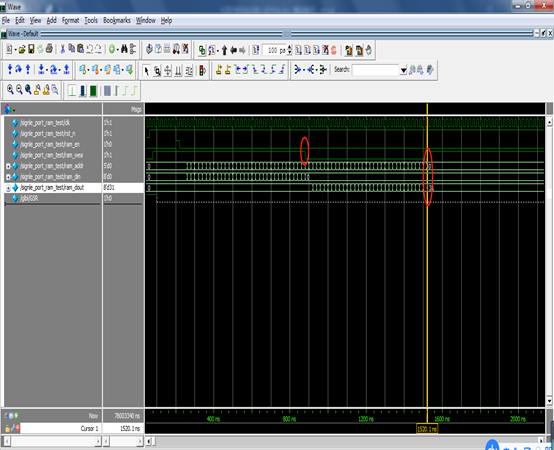

如图1和图2所示分别是:单口RAM IP核的内存类型配置和单口RAM IP核的端口A配置。整个功能模块的设计非常直观,首先定义一个计数器ram_cnt,这个计数器计数了64次,前32次向ram的0-31地址空间写入0-31的数据,后32次读出ram的0-31地址空间读出数据,这时候大家请注意下ram_addr信号量的控制,然后需要把ram_wea信号量在cnt计数到32时候,把其拉低使得单口RAM进入读模式,如图3是单口RAM IP练习的代码设计,仅供参考,练习模块的Testbench测试,非常简单明了,直接给出ram_en触发本模块动作使能信号即可,如图4是单口RAM IP练习的输入信号激励设计,代入Modelsim中即可观察到如图5所示的仿真结果。

图1 单口RAM IP核的内存类型配置

图2 单口RAM IP核的端口A配置

图3 单口RAM IP练习的代码设计

图4 单口RAM IP练习的输入信号激励设计

图5 单口RAM IP核练习的仿真结果

最后

以上就是漂亮白云最近收集整理的关于FPGA之RAM详解,单口RAM的使用单口RAM IP练习的全部内容,更多相关FPGA之RAM详解,单口RAM的使用单口RAM内容请搜索靠谱客的其他文章。

发表评论 取消回复