verilog 模60 8421BCD 计数器

复位信号清零,输出8位8421BCD码,模六十计数。

`timescale 1ns/1ns module BCD_Counter ( input rst_n, //reset input clk, //50MHz clock input output reg cout,//carry output output reg[7:0] cnt ); always@(posedge clk or negedge rst_n) begin if(!rst_n) begin cnt<=1'b0; cout<=1'b0; end else if(cnt<8'h59) if(cnt[3:0]>=4'd9) begin cnt[3:0]<=1'b0; cnt[7:4]<=cnt[7:4]+1'b1; end else begin cnt<=cnt+1'b1; cout<=1'b0; end else begin cnt<=1'b0; cout<=1'b1; end end endmodule

testbench,产生50MHZ 的时钟信号,开始两个时钟周期后复位信号置1.

`timescale 1ns/1ns module BCD_Counter_TB; reg rst_n;//reset reg clk; //50MHz clock input parameter PERIOD=20; //50MHz //generate 50MHz clock initial begin clk=0; forever #(PERIOD/2) clk=~clk; end task task_reset; begin rst_n=0; repeat(2)@(posedge clk) rst_n=1; end endtask wire cout;//carry output wire [7:0] cnt;//data count BCD_Counter u_BCD_Counter ( .rst_n (rst_n), .clk (clk), //output .cnt (cnt), .cout (cout) ); initial begin task_reset; end endmodule

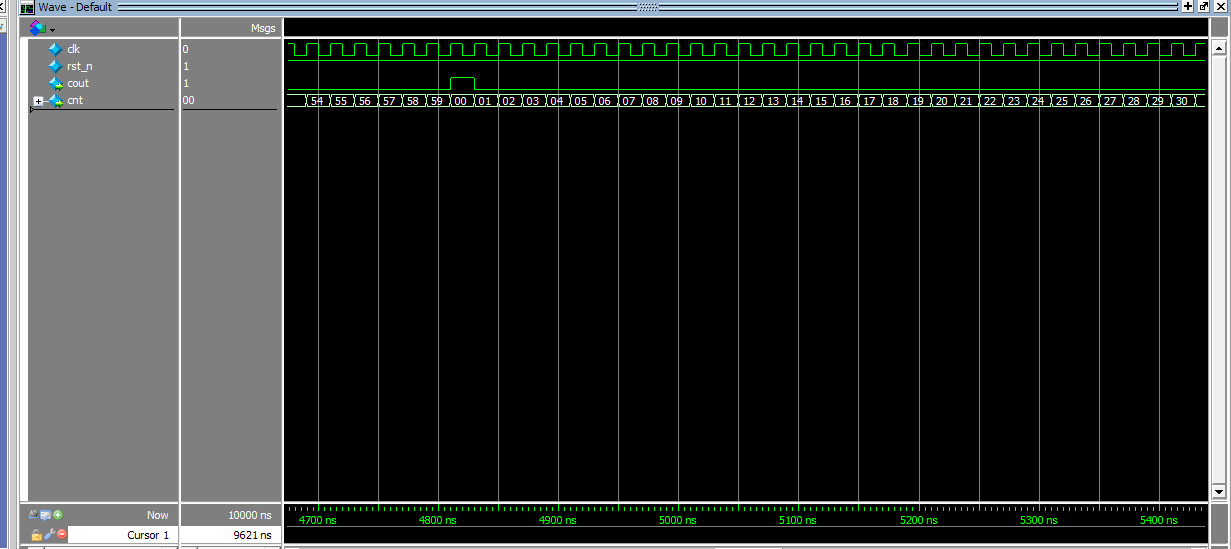

modelisim时序图

转载于:https://www.cnblogs.com/CrazyStranger/p/9669920.html

最后

以上就是火星上绿草最近收集整理的关于verilog 模60 8421BCD 计数器的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复