目前Simulink中已经有时钟分频的现成模块了。分别是下面两个:

Fractional Clock Divider with DSM

Fractional Clock Divider with Accumulator在Mixed-Signal Blockset / PLL / Building Blocks下面。

如果不用现成模块,实际上是可以用上升沿下降沿触发的思路自己搭建一个时钟分频器的。

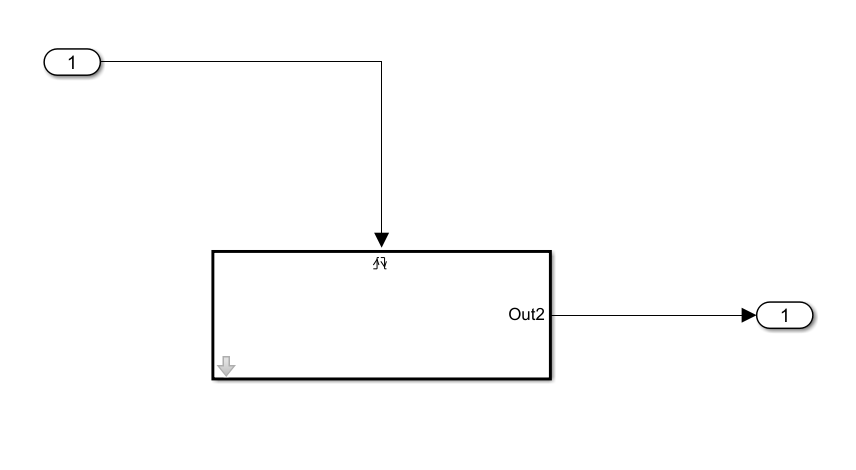

利用Triggered Subsystem的功能,按照硬件语言的思路,按照沿触发一个计数器,到固定的数清零,循环计数,很方便的就能够对一个时钟进行分频。

输入为外部时钟。

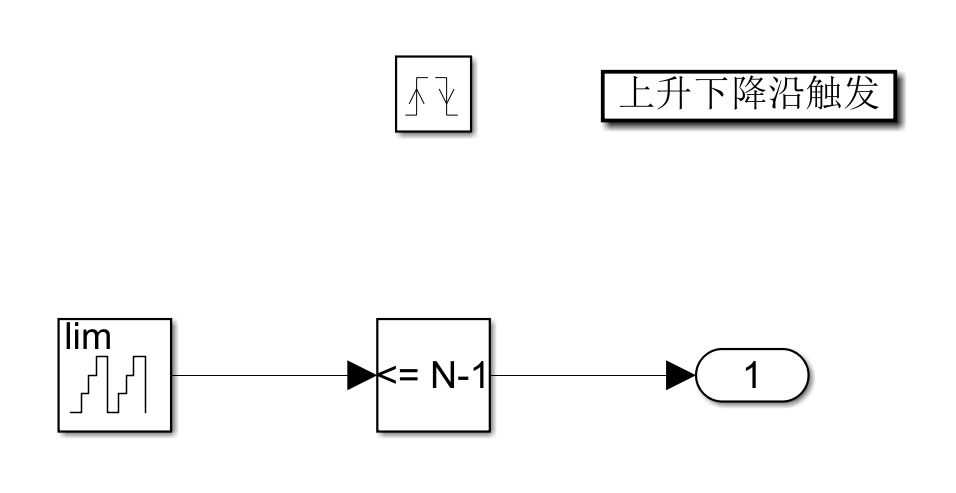

Triggered Subsystem内部有一个计数器和一个比较器。如图:

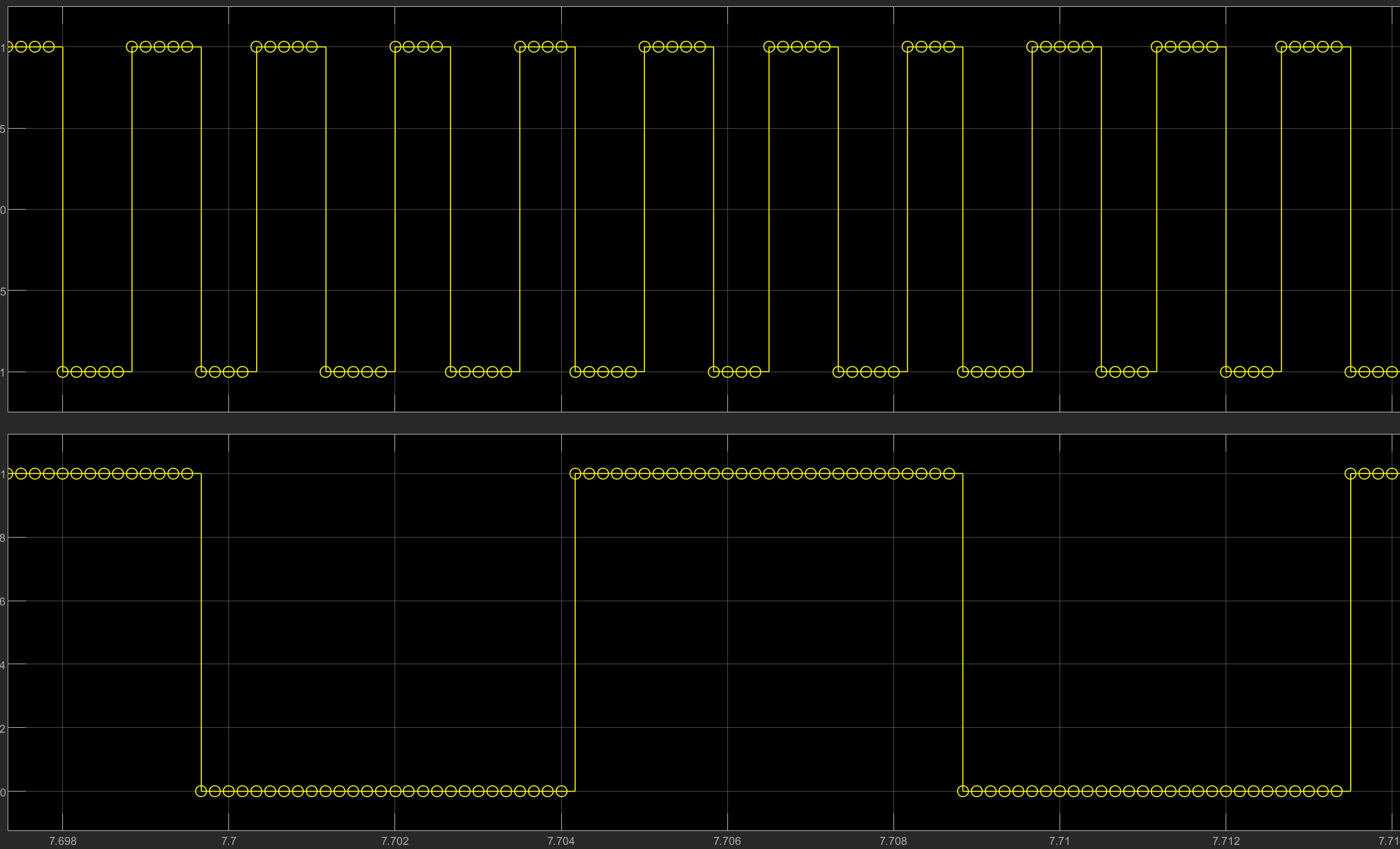

设置为6分频,结果如下:

最后

以上就是默默黑夜最近收集整理的关于Simulink中的时钟分频。的全部内容,更多相关Simulink中内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复