本文记录了笔者对于SR锁存器、D锁存器,和触发器的一些理解。

SR锁存器

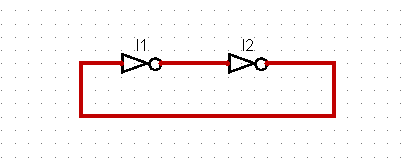

1.交叉耦合反相器:

交叉耦合:I1的输入是I2的输出,反之亦然。

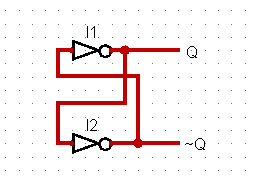

稳态:Q = 0,Q = 1时两种情况都成立,称为双稳态。

具有N种稳态的元件可以表示log2N位的信息。

虽然交叉耦合反相器可以存储1位的信息,但是没有控制状态的输入,所以没有什么实用价值,下介绍SR锁存器。

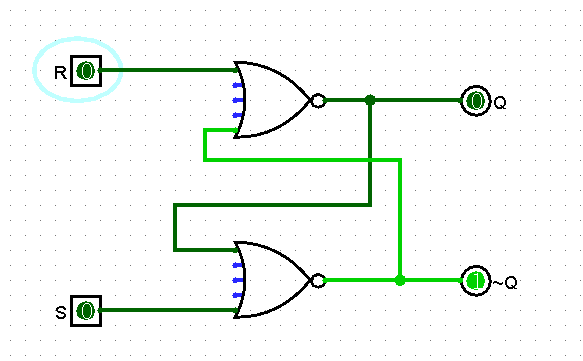

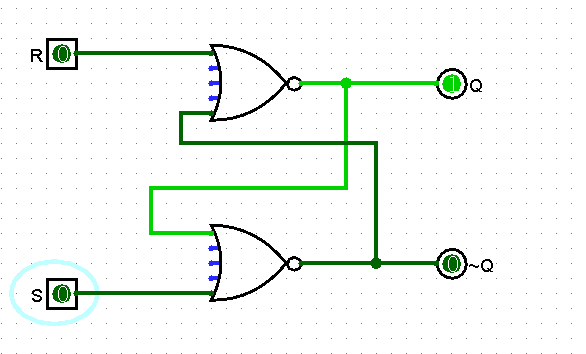

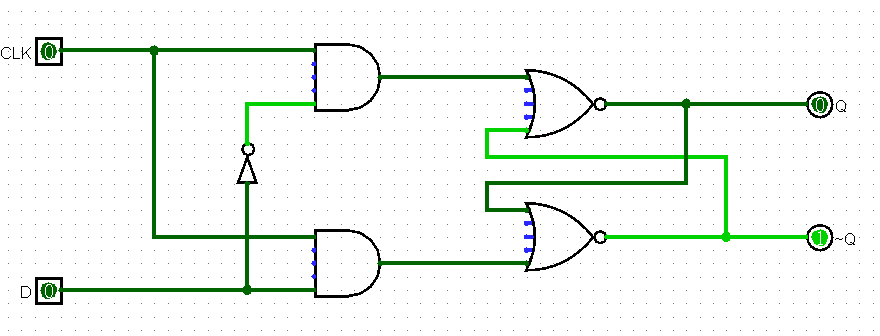

2.SR锁存器

SR锁存器是最简单的时序电路

分析当SR都为0时的情况(上与非门为N1,下与非门为N2):

N1的输入为0 和~Q,结果未知,N2的输入为0和Q,结果未知。

I 当Q = 0 时,N1输入为0和1,N2输入为0和0,符合假设。

II 当Q = 1时,N2输入为0和1,N1输入为0和0,符合假设。

说明当R = S = 0时,电路有记忆功能。

S(置位 Set) 将1位设置为1

R(复位 Reset)将1位设置为0

缺点:

当SR同时有效时,输出不确定

输入SR混淆了时间和内容,我们有时不仅需要确定内容,还需要确定改变的时间

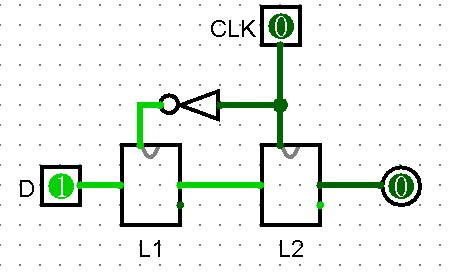

D锁存器

两个输入: 数据输入D和时钟输入CLK

如果CLK = 0,D锁存器阻塞新数据D流向Q,Q的值保持不变

(此时相当于SR锁存器中的S = R = 0)

如果CLK = 1,D锁存器透明,D通过锁存器流向Q,D锁存器不断更新状态

D触发器

由两个背靠背的D锁存器构成, L1为主锁存器,L2为从锁存器。

CLK = 0时,L1透明,数据传入,CLK = 1时,L2转为透明,数据从L1被传递到L2,但L1和L2之间被切断。在时钟从0上升到1之前在时钟变为1之后D值立即被复制到Q

(D触发器在时钟上升沿将D复制到Q,在其他时间保持原来的状态)

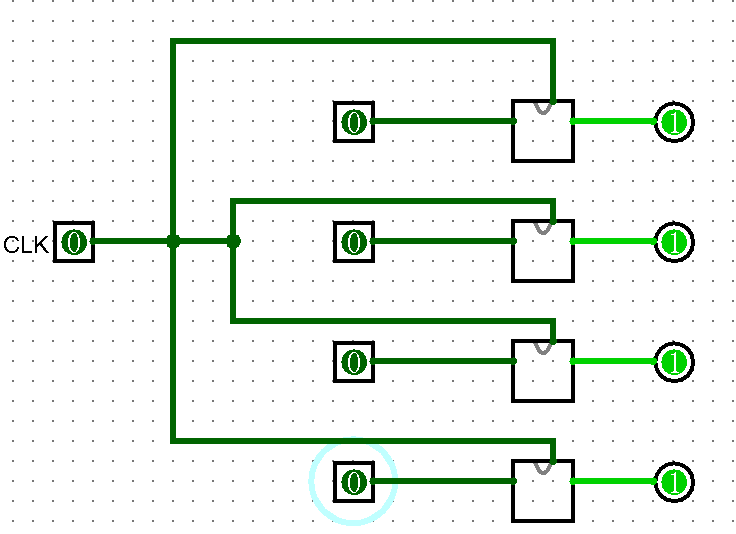

寄存器

一个N位寄存器由共享一个公共CLK输入的一排N个触发器组成

最后

以上就是任性哈密瓜最近收集整理的关于锁存器、触发器与寄存器SR锁存器D锁存器D触发器寄存器的全部内容,更多相关锁存器、触发器与寄存器SR锁存器D锁存器D触发器寄存器内容请搜索靠谱客的其他文章。

发表评论 取消回复