项目场景:

Design a 1-12 counter with the following inputs and outputs:

Reset Synchronous active-high reset that forces the counter to 1

Enable Set high for the counter to run

Clk Positive edge-triggered clock input

Q[3:0] The output of the counter

c_enable, c_load, c_d[3:0] Control signals going to the provided 4-bit counter, so correct operation can be verified.

You have the following components available:

the 4-bit binary counter (count4) below, which has Enable and synchronous parallel-load inputs (load has higher priority than enable). The count4 module is provided to you. Instantiate it in your circuit.

logic gates

module count4(

input clk,

input enable,

input load,

input [3:0] d,

output reg [3:0] Q

);

The c_enable, c_load, and c_d outputs are the signals that go to the internal counter’s enable, load, and d inputs, respectively. Their purpose is to allow these signals to be checked for correctness.

Module Declaration

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

);

问题描述

设计一个1-12的计数器,有以下输入和输出:

Reset同步active-high复位,强制计数器到1

Enable设置high,计数器运行Clk正向边缘触发时钟输入

Q[3:0]计数器的输出

c_enable, c_load, c_d[3:0]控制信号到达提供的4位计数器,因此可以验证正确的操作。

您有以下可用的组件:

下面的4位二进制计数器(count4),它具有Enable和同步并行负载输入(load优先级高于Enable)。count4模块提供给您。在你的电路中实例化它。

module count4(

input clk,

input enable,

input load,

input [3:0] d,

output reg [3:0] Q

);

c_enable、c_load和c_d输出分别是发送到内部计数器的enable、load和d输入的信号。它们的目的是允许检查这些信号的正确性。

原因分析:

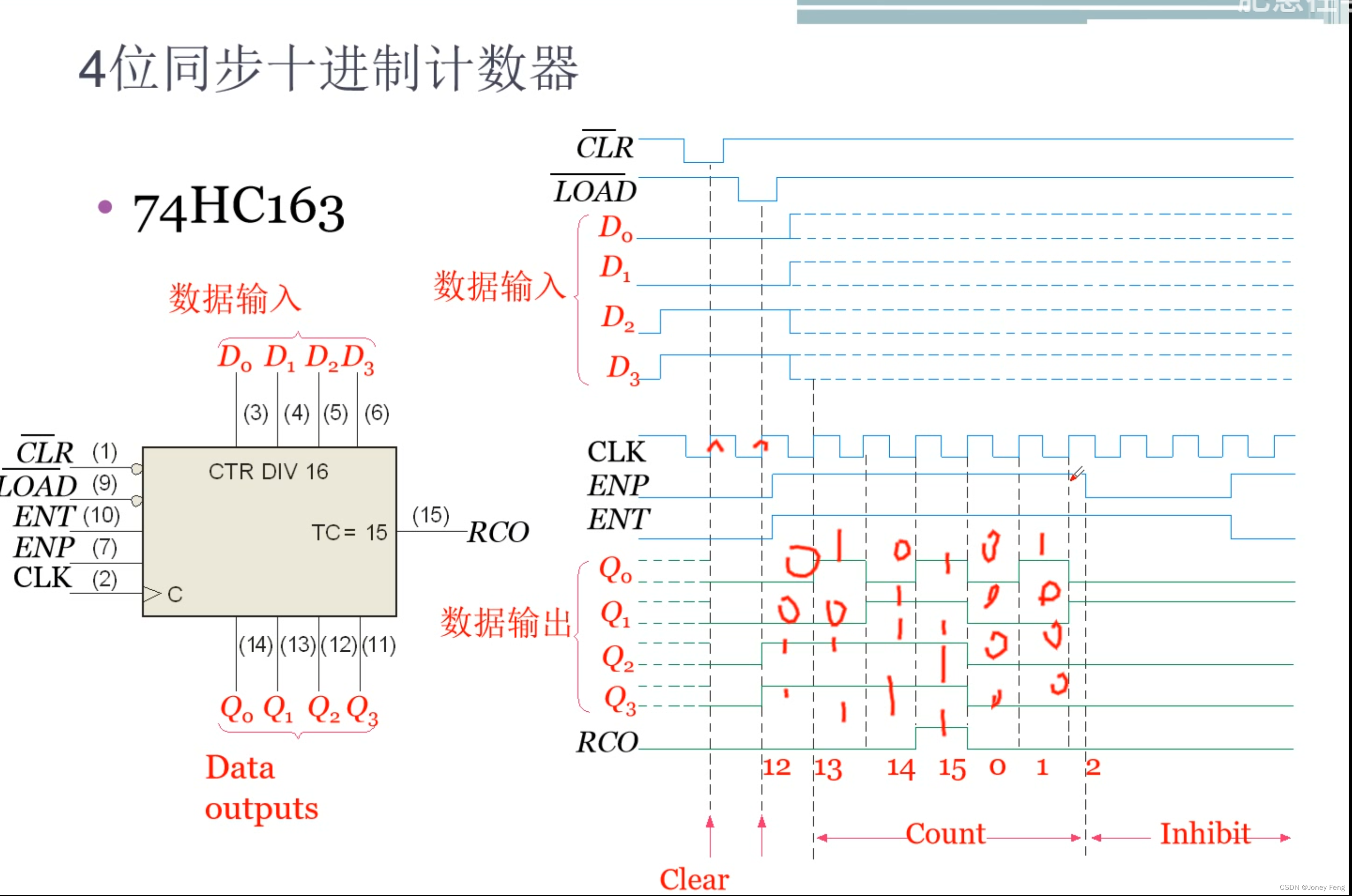

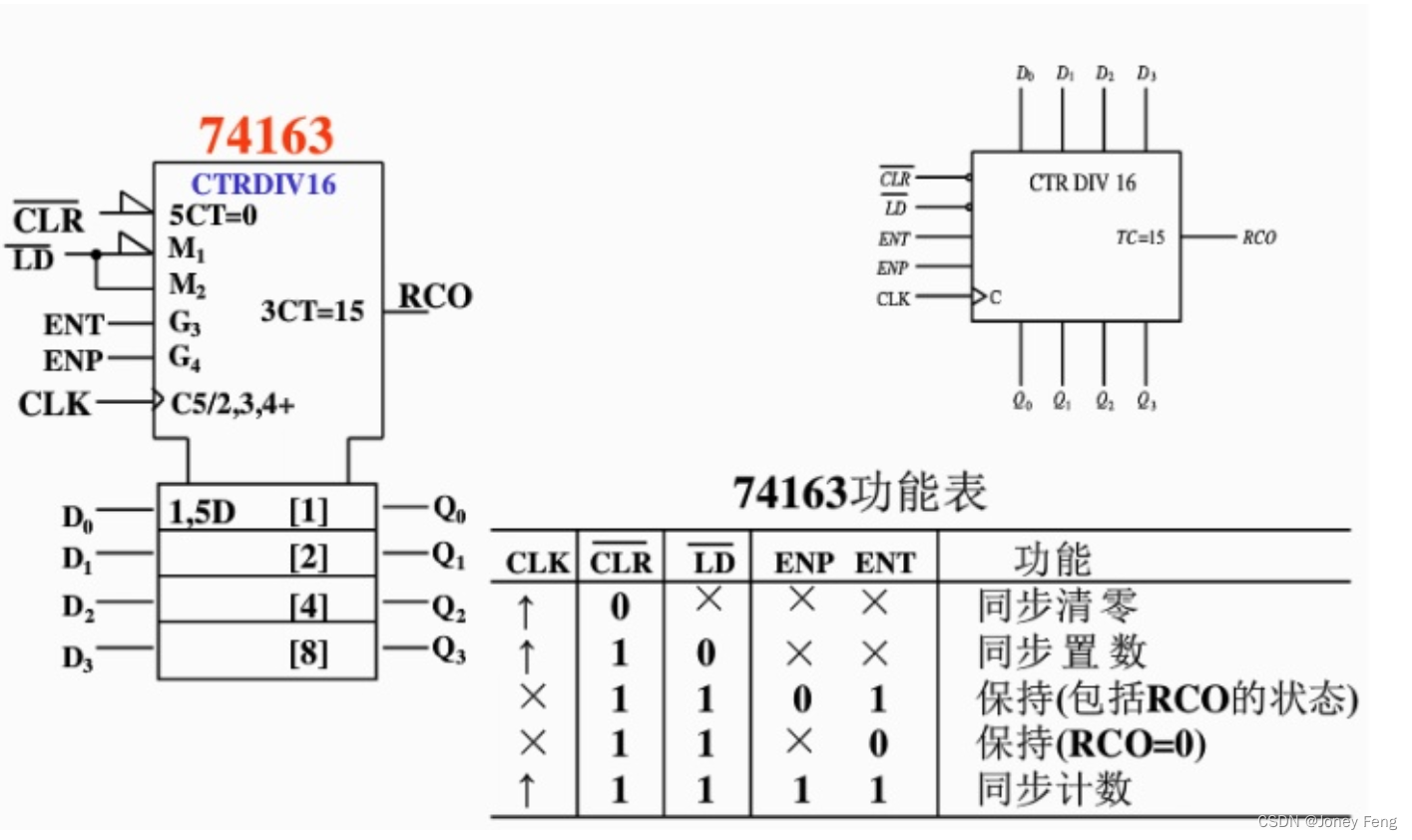

刚开始读题感觉好晕,没有办法来理清整道题的一个思路这可能是我们对4位2进制加法计数器的工作原理不清晰。十进制计数器与4位二进制计数器有些相似,但4位二进制计数器需要计数到1111然后 才能返回到0000,而十进制计数器要求计数到1001 (相当于9)就返回0000。8421BCD码 十进制计数器是一种最常用的十进制计数器。

其实就是根据输入的reset信号和计数的最大值Q_MAX=12来确定load和c_d的值来得到4位2进制加法计数器的输入进而实现1-12的计数器。当计数器计数到最大值或者reset信号置1时,强制计数器到1,也就是load和d的值都置1。计数器模式由load信号和使能信号决定。

解决方案:

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

);

always@(*)

begin

if(reset == 1'b1)

begin

c_load <= 1'b1;

c_d <= 4'd1;

end

else

begin

c_load <= 1'b0;

c_d <= 4'd0;

if((enable == 1'b1) && (Q == 4'd12))

begin

c_load <= 1'b1;

c_d <= 4'd1;

end

end

end

assign c_enable = enable;

count4 count4_inst(

.clk (clk) ,

.enable (enable) ,

.load (c_load) ,

.d (c_d) ,

.Q (Q)

);

endmodule

最后

以上就是整齐嚓茶最近收集整理的关于Exams/ece241 2014 q7a(Counter1-12)项目场景:问题描述原因分析:解决方案:的全部内容,更多相关Exams/ece241内容请搜索靠谱客的其他文章。

发表评论 取消回复