今天给大侠带来的是一周掌握FPGA Verilog HDL 语法,今天开启第六天。

上一篇提到了编译预处理(宏定义 `define、“文件包含”处理`include、时间尺度 `timescale、条件编译命令`ifdef、`else、`endif),经过五天的Verilog HDL基础语法的学习,基本语法差不多都在这里了,最后两天推出思考题(附参考答案),大侠可以自行思考,检测一下自己这一周的语法学习效果,结合实例理解理论语法,会让你理解运用的更加透彻。下面咱们废话就不多说了,一起来看看吧。

思考题实例运用

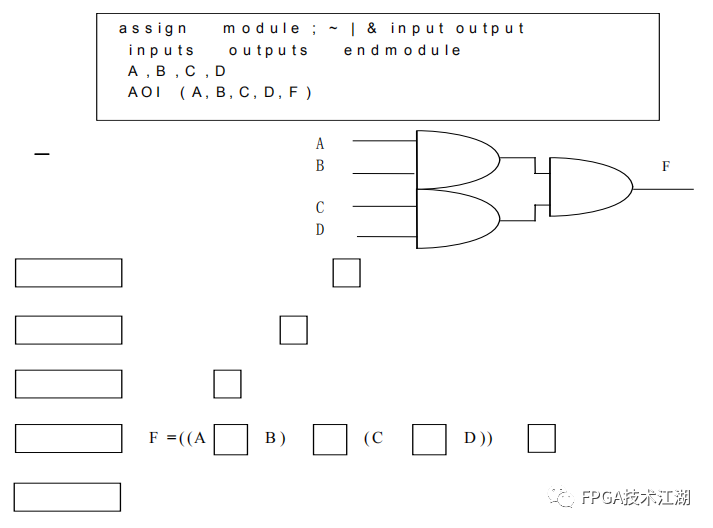

1)以下给出了一个填空练习,请将所给各个选项根据电路图,填入程序中的适当位置。

参考答案:

module AOI(A,B,C,D,F);input A,B,C,D;output F;assign F = ((A&B)&(C&D));endmodule

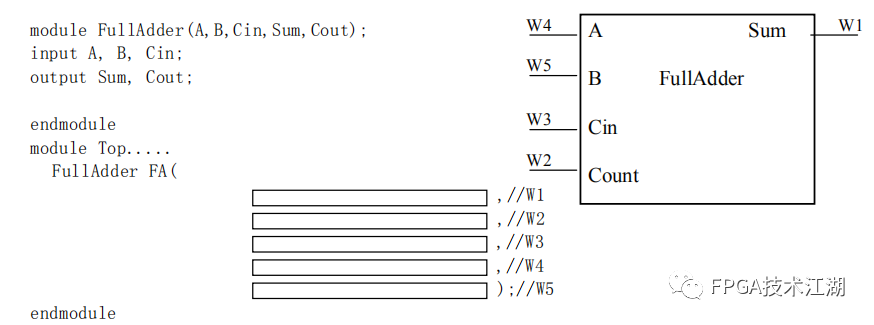

2〕 在这一题中,我们将作有关层次电路的练习,通过这个练习,你将加深对模块间调用时,管脚间连接的理解。假设已有全加器模块FullAdder,若有一个顶层模块调用此全加器,连接线分别为W4,W5,W3,W1和W2。请在调用时正确地填入I/O的对应信号。

参考答案:

moduleTop...FullAdderFA( .Sum(W1), //W1.Cout(W2),//W2.Cin(W3), //W3.A(W4), //W4.B(W5)); //W5endmodule

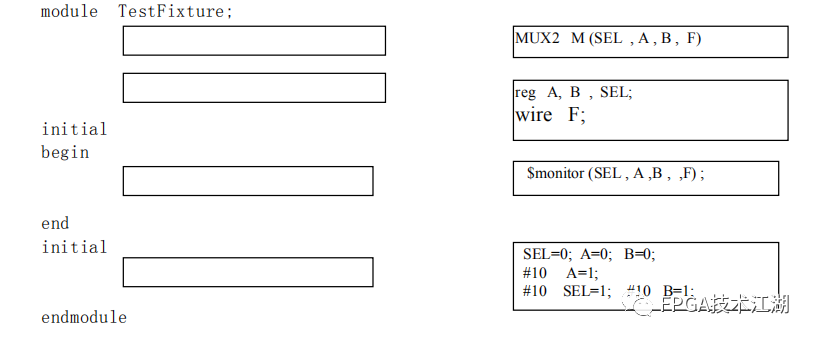

3)下面这道题是一个测试模块,因此没有输入输出端口,请将相应项填入合适的位置。

参考答案:

module TestFixture;reg A,B,SEL;wire F;MUX2M(SEL,A,B,F);initialbeginSEL=0; A=0; B=0;#10 A=1;#10 SEL=1; #10 B=1;endinitial$monitor(SEL,A,B,,F);endmodule

4)指出下面几个信号的最高位和最低位。

reg [1:0] SEL;

input [0:2] IP;

wire [16:23] A;

参考答案:

MSB:SEL[1] MSB:IP[0] MSB:A[16] LSB:SEL[0]

LSB:IP[2] LSB:A[23]

5)P,Q,R都是4bit的输入矢量,下面哪一种表达形式是正确的。

1)input P[3:0],Q,R;

2)input P,Q,R[3:0];

3)input P[3:0],Q[3:0],R[3:0];

4)input [3:0] P,[3:0]Q,[0:3]R;

5)input [3:0] P,Q,R;

参考答案:5)

6)请将下面选项中的正确答案填入空的方括号中。

1. (0:2) 2. (P:0) 3. (Op1:Op2) 4.(7:7) 5. (2:0) 6. (7:0)

reg [7:0] A;reg [2:0] Sum, Op1, Op2;reg P, OneBit;initialbeginSum=Op1+Op2;P=1;A[ ?]=Sum;.....end

标准答案:5

7)请根据以下两条语句,从选项中找出正确答案。

7.1)

reg [7:0] A;

A=2'hFF;

1) 8'b0000_0011

2) 8'h03

3) 8'b1111_1111

4) 8'b11111111

参考答案:1)

7.2)

reg [7:0] B;

B=8'bZ0;

1) 8'0000_00Z0

2) 8'bZZZZ_0000

3) 8'b0000_ZZZ0

4) 8'bZZZZ_ZZZ0

参考答案:4)

8)请指出下面几条语句中变量的类型。

8.1) assign A=B;

8.2) always #1 Count=C+1;

参考答案: A(wire) B(wire/reg) Count(reg) C(wire/reg)

9)指出下面模块中Cin,Cout,C3,C5,的类型。

module FADD(A,B,Cin,Sum,Cout);input A, B, Cin;output Sum, Cout;....endmodule

module Test;...FADDM(C1,C2,C3,C4,C5);...endmodule

参考答案: Cin(wire) Cout(wire/reg) C3(wire/reg) C5(wire)

10〕在下一个程序段中,当ADDRESS的值等于5'b0X000时,问casex执行完后A和B的值是多少。

A=0;B=0;casex(ADDRESS)5'b00???: A=1;5'b01???: B=1;5'b10?00,5'b11?00:beginA=1;B=1;endendcase

参考答案: A=1 and B=0;

11)在下题中,事件A分别在10,20,30发生,而B一直保持X状态,问在50时Count的值是多少。

reg [7:0] Count;initialCount=0;alwaysbegin@(A) Count=Count+1;@(B) Count=Count+1;end

参考答案:Count=1;

(这是因为当A第一次发生时,Count的值由0变为1,然后事件控制 @(B) 阻挡了进程。)

12)在下题中initial块执行完后I,J,A,B的值会是多少。

reg [2:0] A;reg [3:0] B;integer I, J;initialbeginI=0;A=0;I=I-1;J=I;A=A-1;B=A;J=J+1;B=B+1;end

参考答案:

I=-1 (整数可为负数)

J=0

A=7 (A为reg型为非负数,又因为A为3位即为111)

B=8 (在B=A时,B=0111,然后B=B+1,所以B=4’b1000)

13)在下题中,当V的值发生变化且为-1时,执行完always块后 Count的值应是多少?

reg[7:0]V;reg[2:0]Count;always @(V)beginCount=0;while(~V[Count])Count=Count+1;end

参考答案:Count=0;

Day 6 就到这里,最后一天Day 7 继续推出思考题(附参考答案),大侠可以自行思考,检测一下自己这一周的语法学习效果,大侠保重,告辞。

END

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

最后

以上就是清爽鞋垫最近收集整理的关于一周掌握FPGA Verilog HDL语法 day 6的全部内容,更多相关一周掌握FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复