FPGA——数字电路

- 一、数制

- 二、门电路

- 2.1 基本门电路

- 2.2 复合门电路

- 三、组合逻辑电路&时序逻辑电路

- 3.1 输入输出关系

- 3.2 结构特点

- 3.3 储存记忆

- 3.4 常用电路

- 3.5 区别——波形图

- 3.6 区别——verilog语言

一、数制

- 常用的为十进制(d)、二进制(b)、八进制(o)、十六进制(h)

- 常用二进制代码

| 十进制数 | 自然二进制 | BCD_8421码 | 格雷码 |

|---|---|---|---|

| 0 | 0000 | 0000 | 0000 |

| 1 | 0001 | 0001 | 0001 |

| 3 | 0011 | 0011 | 0010 |

| 6 | 0110 | 0110 | 0101 |

| 11 | 1011 | 0001 0001 | 1110 |

| 15 | 1111 | 0001 0101 | 1000 |

格雷码:参照自然二进制码,第一位与自然二进制码相同,之后的每一位与二进制数相应位做异或。

二、门电路

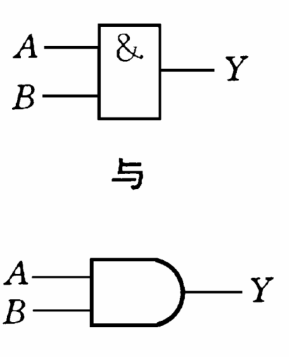

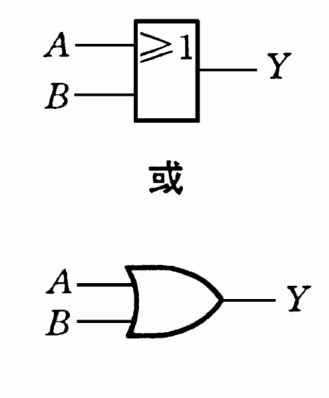

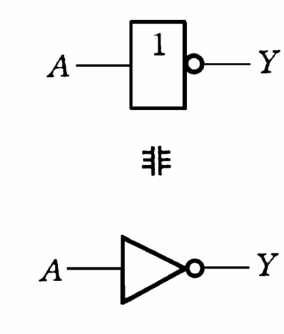

2.1 基本门电路

- 与门(and)

- 或门(or)

- 非门(not)

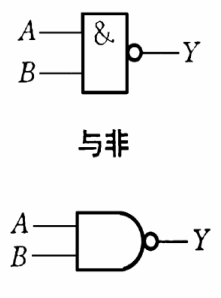

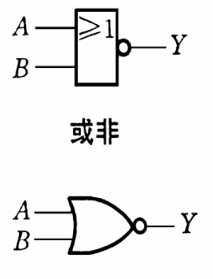

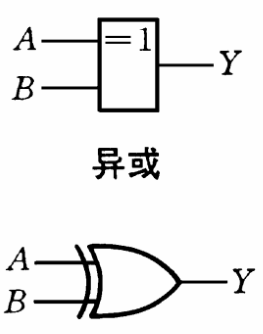

2.2 复合门电路

- 与非门

- 或非门

- 异或门

三、组合逻辑电路&时序逻辑电路

3.1 输入输出关系

- 组合逻辑电路:任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

- 时序逻辑电路:任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

3.2 结构特点

- 组合逻辑电路:只包含门电路。

- 时序逻辑电路:组合逻辑电路+存储电路结合;输出状态必须反馈到组合电路的输入端,与输入信号共同决定组合逻辑的输出。

3.3 储存记忆

- 组合逻辑电路:无。

- 时序逻辑电路:有。

3.4 常用电路

- 组合逻辑电路:编码器、译码器、数据选择器、加法器、数值比较器。

- 时序逻辑电路:寄存器、移位寄存器、计数器。

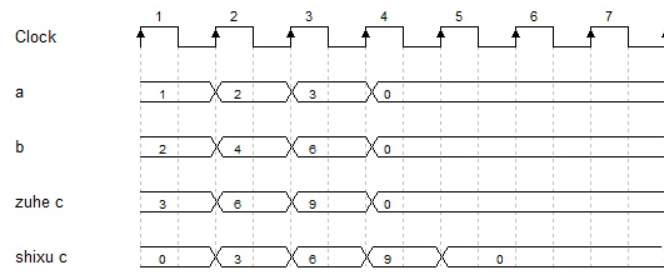

3.5 区别——波形图

- 组合逻辑电路:波形即刻反映变化,与时钟无关。

- 时序逻辑电路:波形不会立刻反映出来,只有在时钟的上升沿发生变化。

- 如图 3.5

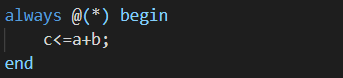

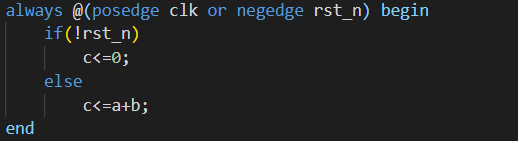

3.6 区别——verilog语言

-

组合逻辑电路:没有上升沿或者是带有" * "号的代码。

-

时序逻辑电路:敏感列表里面带有时钟上升沿。

-

波形图如图 3.5

最后

以上就是大气小鸭子最近收集整理的关于FPGA——数字电路的全部内容,更多相关FPGA——数字电路内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复