目录

实验目的

一、调用ROM IP核

二、生成顶层模块

三、仿真文件的编写

四、进行仿真验证

实验目的

本实验工程目的是实现输出数据位宽为16的正弦波形。

一、调用ROM IP核

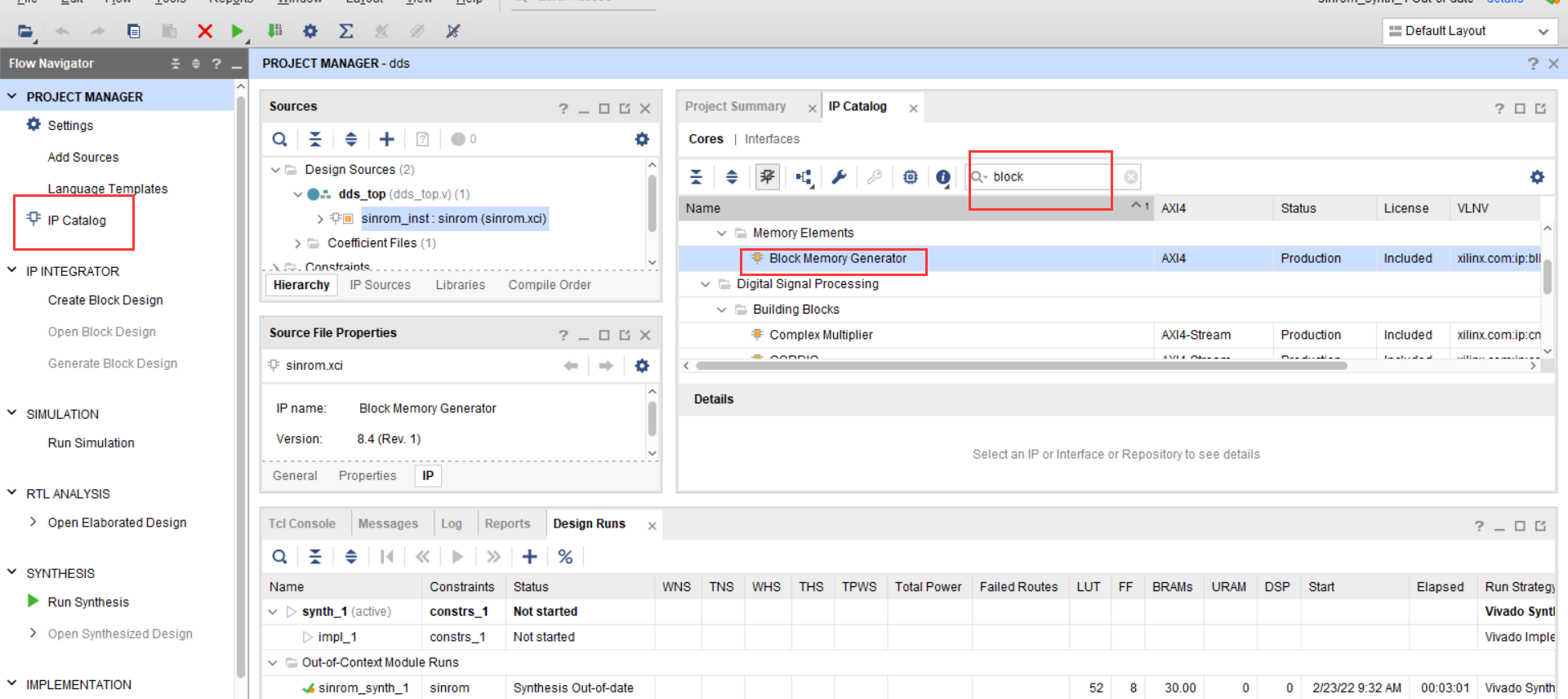

打开vivado,创建实验工程,点击左侧菜单栏的IP Catalog,搜索Block,就可以看到block memory generator,双击打开进行配置。

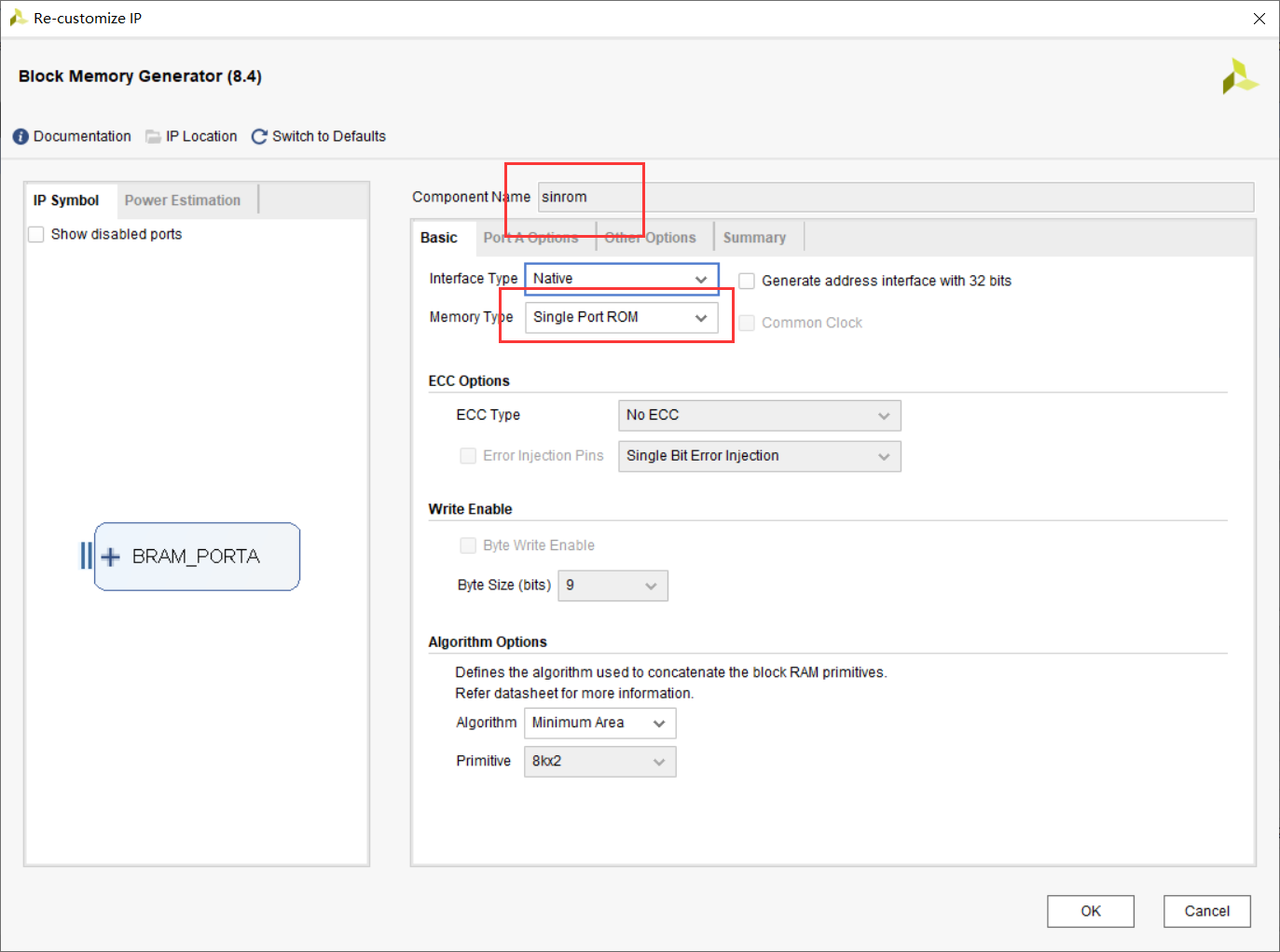

首先在basic选项卡中将memory type配置成单端口的ROM,因为我们会事先将数据存入ROM中,只需要对它的地址空间进行读取即可,同时也可以将这个IP定义成自己想要的名称,方便辨别。其余保持默认。

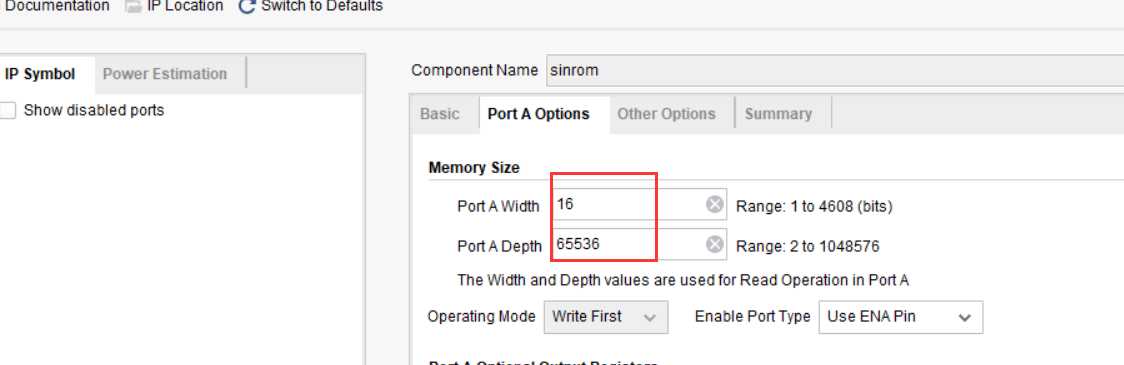

在port A options选项卡中,将数据位宽配置成16,深度配置成65536,也可以根据自己的需求改变参数,但在之后的代码需要进行位宽的更改。其余保持默认。

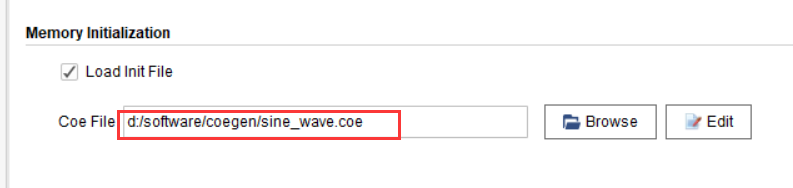

在other option的选项卡中,加载所需要的coe文件,我用的是小梅哥的coe文件生成器,同样的也是将数据位宽配置成16,深度配置成65536.最后将所生成的coe文件加载其中即可。 配置完成点击ok。

二、生成顶层模块

点击sources中的加号键,选择添加设计文件,一路点击确定。

再进行顶层模块的代码编写,这里的代码主要包括对端口的申明以及对ROM IP核的例化。

同时,也定义读取地址的方式,这里定义的步进为1,也就是依次对ROM的地址内的数据进行读取,也可以根据自己的需要进行更改,但是更改的同时也会改变输出波形的频率。

关于DDS的理论知识,可以看下另一篇博客,博客中详细介绍了DDS的原理以及相关参数的含义。

`timescale 1ns / 1ps

module dds_top(

input clk,

input rst,

input ena,

output [15:0] data

);

reg [15:0] addr;

parameter fword = 1;

//addr

always @(posedge clk or posedge rst) begin

if (rst) begin

addr <= 'd0;

end

else if (ena == 1'b1) begin

addr <= addr + fword;

end

else begin

addr <= 'd0;

end

end

//例化sinrom IP

sinrom sinrom_inst (

.clka(clk), // input wire clka

.ena(ena), // input wire ena

.addra(addr), // input wire [15 : 0] addra

.douta(data) // output wire [15 : 0] douta

);

endmodule

三、仿真文件的编写

同第二步的操作,点击加号添加仿真文件,测试代码如下。

`timescale 1ns / 1ps

module tb_sinrom(

);

reg clk;

reg rst;

reg ena;

wire [15:0] data;

initial begin

clk = 1'b0;

end

always #10 clk = ~clk;

initial begin

rst = 1'b1;

ena = 1'b1;

#200

rst = 1'b0;

end

dds_top inst_dds_top (

.clk(clk),

.rst(rst),

.ena(ena),

.data(data)

);

endmodule

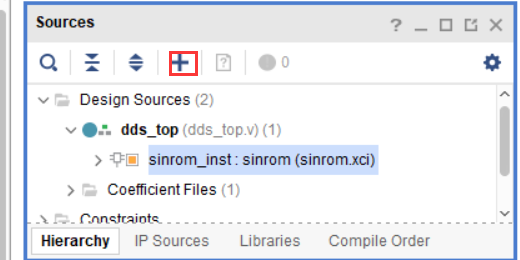

保存就可以看到测试文件已经将顶层和ROM IP核包含了。

四、进行仿真验证

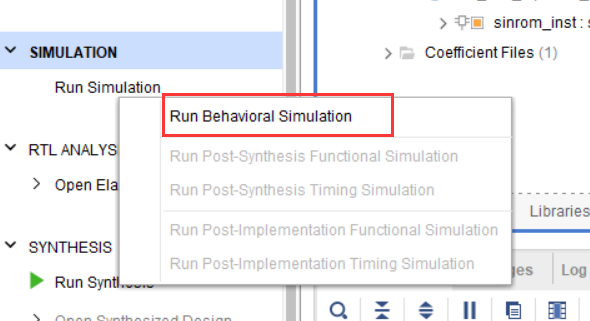

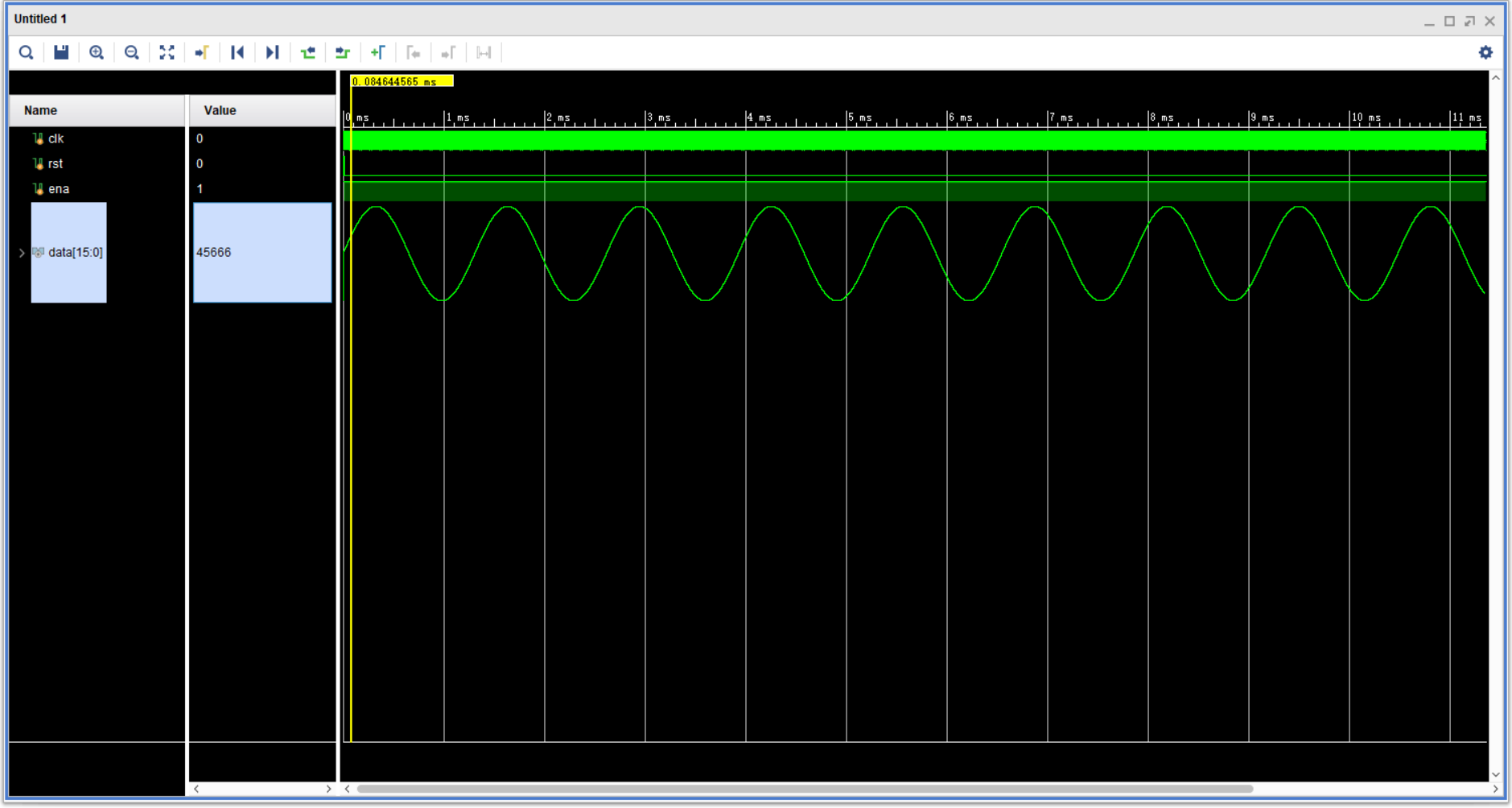

点击左侧菜单栏中的 run simulation,即可看到仿真波形。

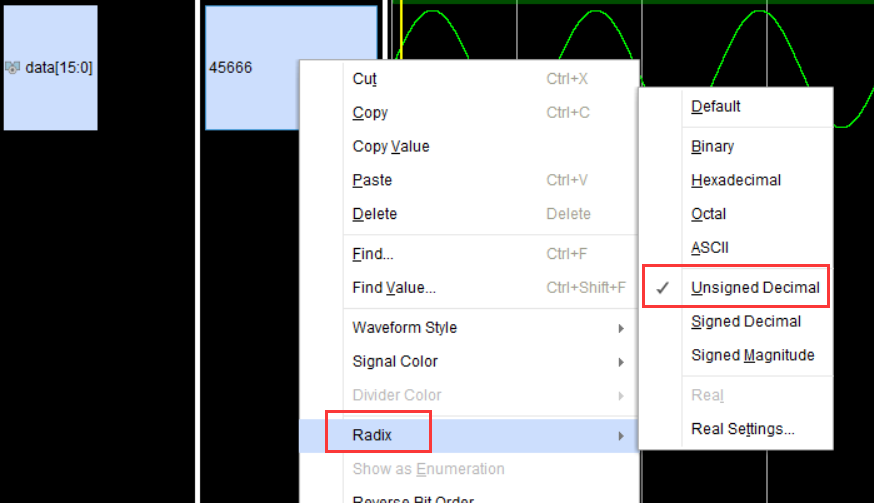

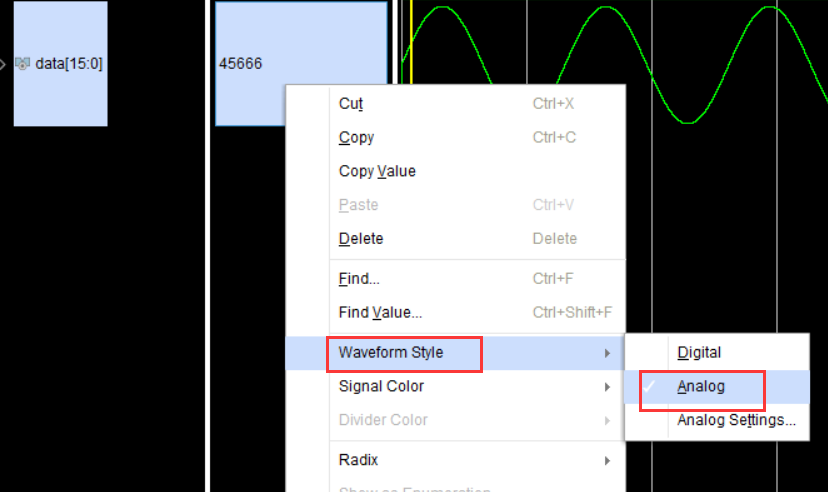

将输出数据data的值设置为无符号的十进制以及波形形式设置为模拟波形,即可看到正弦波,如果只看到一点波形,可以多跑10ms。

下面是之前写的博客,里面介绍DDS的相关原理以及参数设定含义,并实现两路波形的混频操作。

【Vivado DDS IP核】Vivado的DDS IP核使用以及混频操作_m0_61298445的博客-CSDN博客 https://blog.csdn.net/m0_61298445/article/details/122442678?spm=1001.2014.3001.5501

https://blog.csdn.net/m0_61298445/article/details/122442678?spm=1001.2014.3001.5501

最后

以上就是丰富大叔最近收集整理的关于【Xilinx DDS】Vivado代码实现FPGA DDS实验目的一、调用ROM IP核二、生成顶层模块三、仿真文件的编写四、进行仿真验证的全部内容,更多相关【Xilinx内容请搜索靠谱客的其他文章。

发表评论 取消回复