基于FPGA的AM调制与解调以及从中学到的东西(注:解调没搞太清楚,没写)

- 随便说说

- 一、平台

- 二、DDS IP的使用

- 三、FIR滤波(用于后面AM解调)

- 四、AM调制

- 五、整体代码

- 六、仿真波形

- 总结

随便说说

(这次小杨第一次写博客,有问题,见谅!)

前几天没事做就想学习学习信号类的知识,然后就想到了去年电赛折磨我的AM与FM的调制与解调。AM的调制与解调用FPGA来实现还是不是很难,但是我还是看了两位博主的博客(链接在这一段结尾)。本次AM调制与解调的信号都是有DDS输出的,载波为1MHz,调制波为10KHz。

AM调制与解调:(博主:子木呀)

AM调制与解调:(博主:黄子炫)

一、平台

1.软件:Vivado 2018.3(就只会这个。。。。)

2.硬件:EGO1

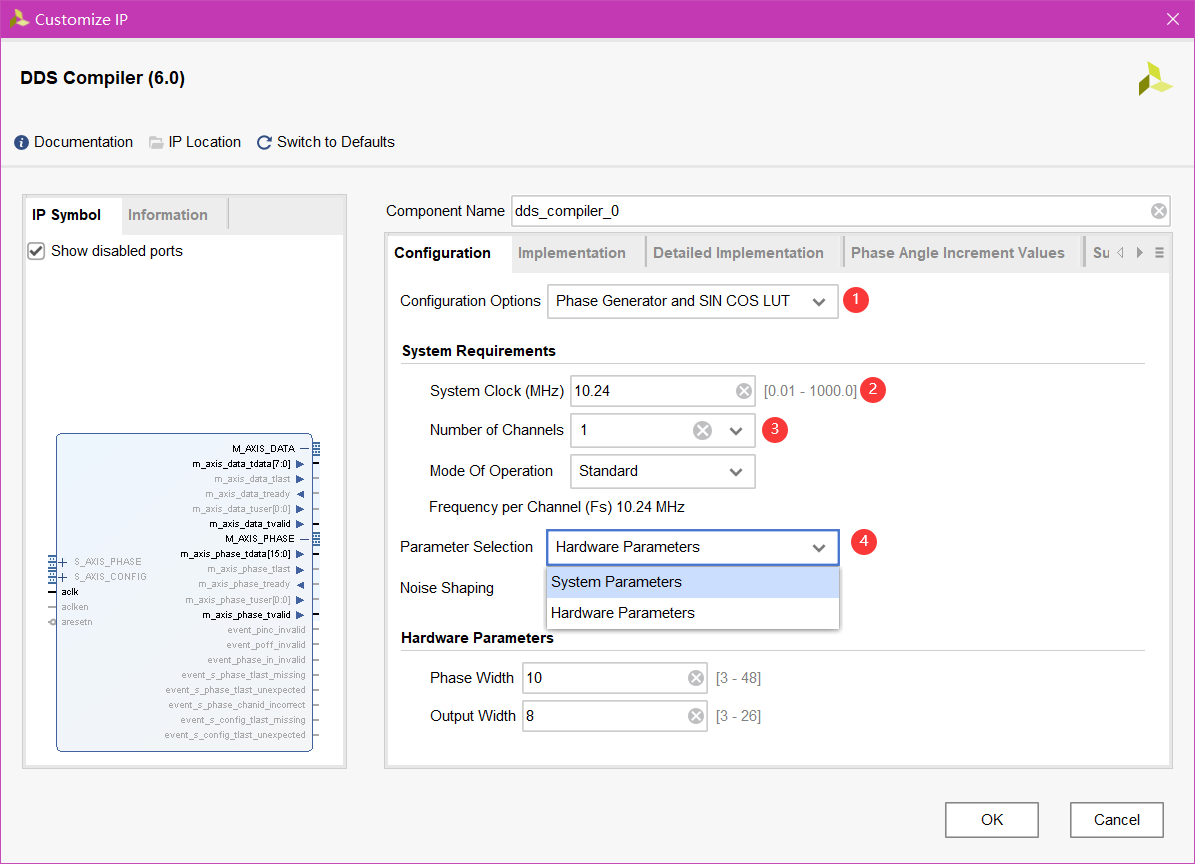

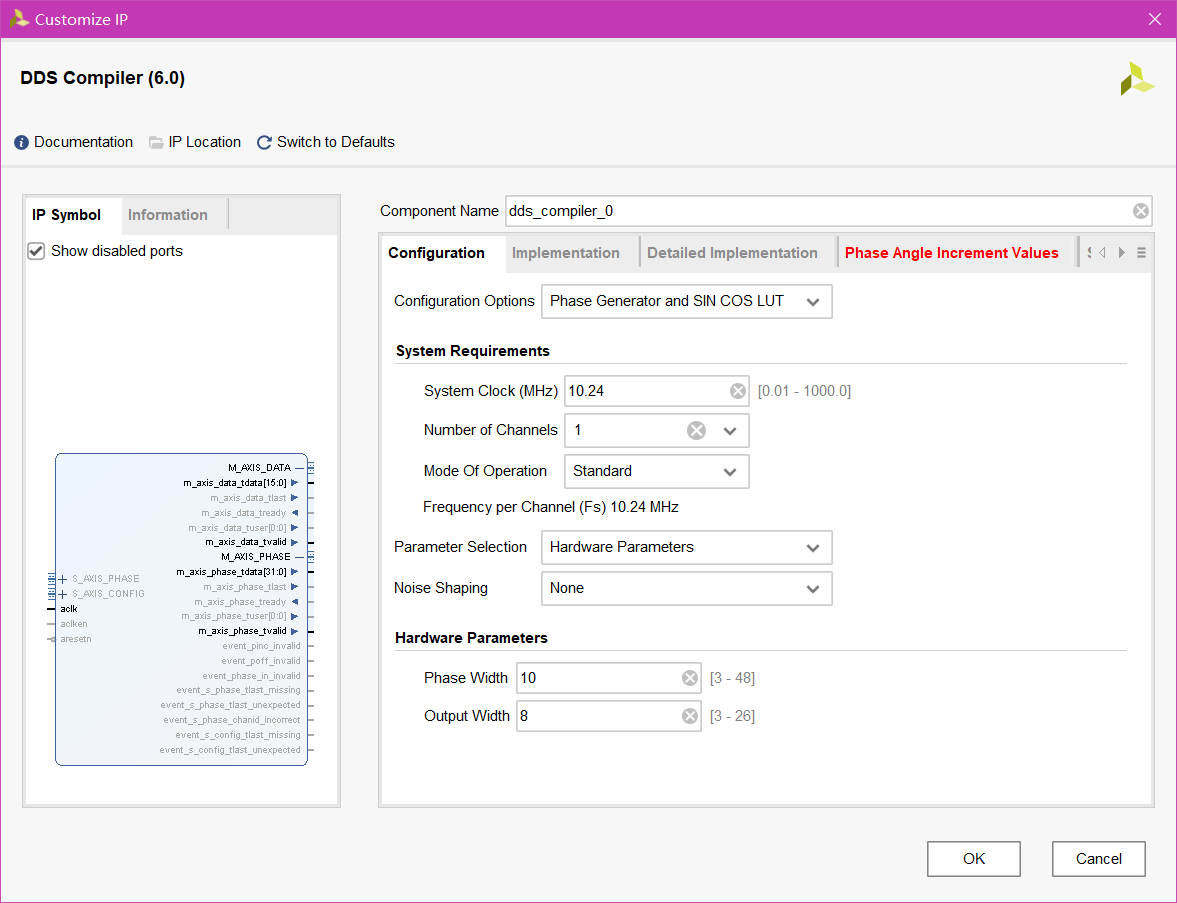

二、DDS IP的使用

(这里加个链接(DDS的配置))

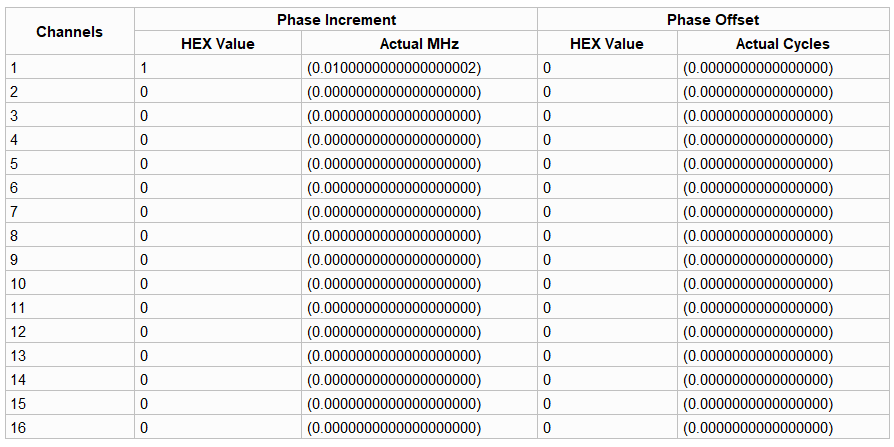

个人能力有限,就只能看懂这四个地方(/手动糊脸/)。

1.Configuration Options(配置选项):配置DDS的类型,下来有三个选项,这里选着“Phase Generator and SIN Cos LUT”。

2.System Clock(配置DDS的输入系统时钟):对应的引脚(看左边的那个RTL,由aclk输入),这里配置10.24MHz(这个值后面会解释)。

3.Number of Channels(通道数):因为只用到一个输出,所以通道数为1。(其实是自己不会多通道的使用。。。。)

4.Parameter Selection(参数选择):这里我把选项下拉出来了。为了后面使用的方便,这里我选择“Hardware Parameters”

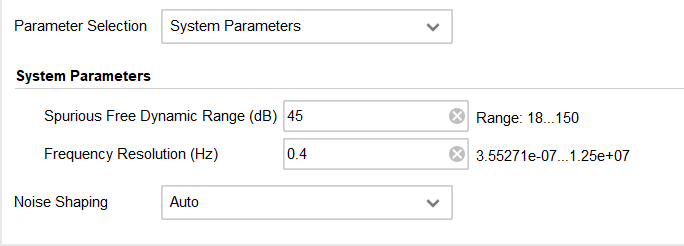

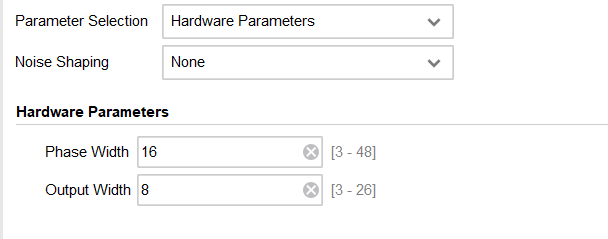

这里我把Hardware Parameters和System Parameters的两个界面给截图出来对比了一下。System Parameters需要去计算频率分辨率,这个计算起来就。。。。(我算不明白)。Hardware Parameters就很方便,它的Phase Width默认值为16,Output Width默认值为8。Phase Width的值会影响到我们的输入频率,我使用的时候配的是10位宽。下面展示Phase Width与输入频率的关系。(为了省事,我把一位博主写的部分搬过来,感谢子木呀!)

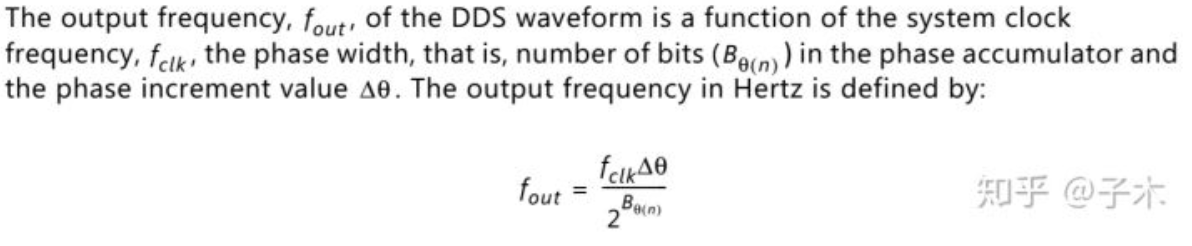

DDS核频率分辨率计算公式如下:

其中Δθ就是我们的频率控制字取值后文用fre_word表示,Bθ(n)是相位累加器位宽后文用B表示,fclk为DDS工作时钟。频率分辨率就是当Δθ=1时的fout。先假如我们需要的信号频率范围:1M-10MHz,分辨率0.01MHz。

其中Δθ就是我们的频率控制字取值后文用fre_word表示,Bθ(n)是相位累加器位宽后文用B表示,fclk为DDS工作时钟。频率分辨率就是当Δθ=1时的fout。先假如我们需要的信号频率范围:1M-10MHz,分辨率0.01MHz。

取Δθ=1,fout=0.01MHz,B=10bit,我们可得DDS工作时fclk=10.24MHz。

这里展示一下Configuration配置完的界面(注意左边的RTL):

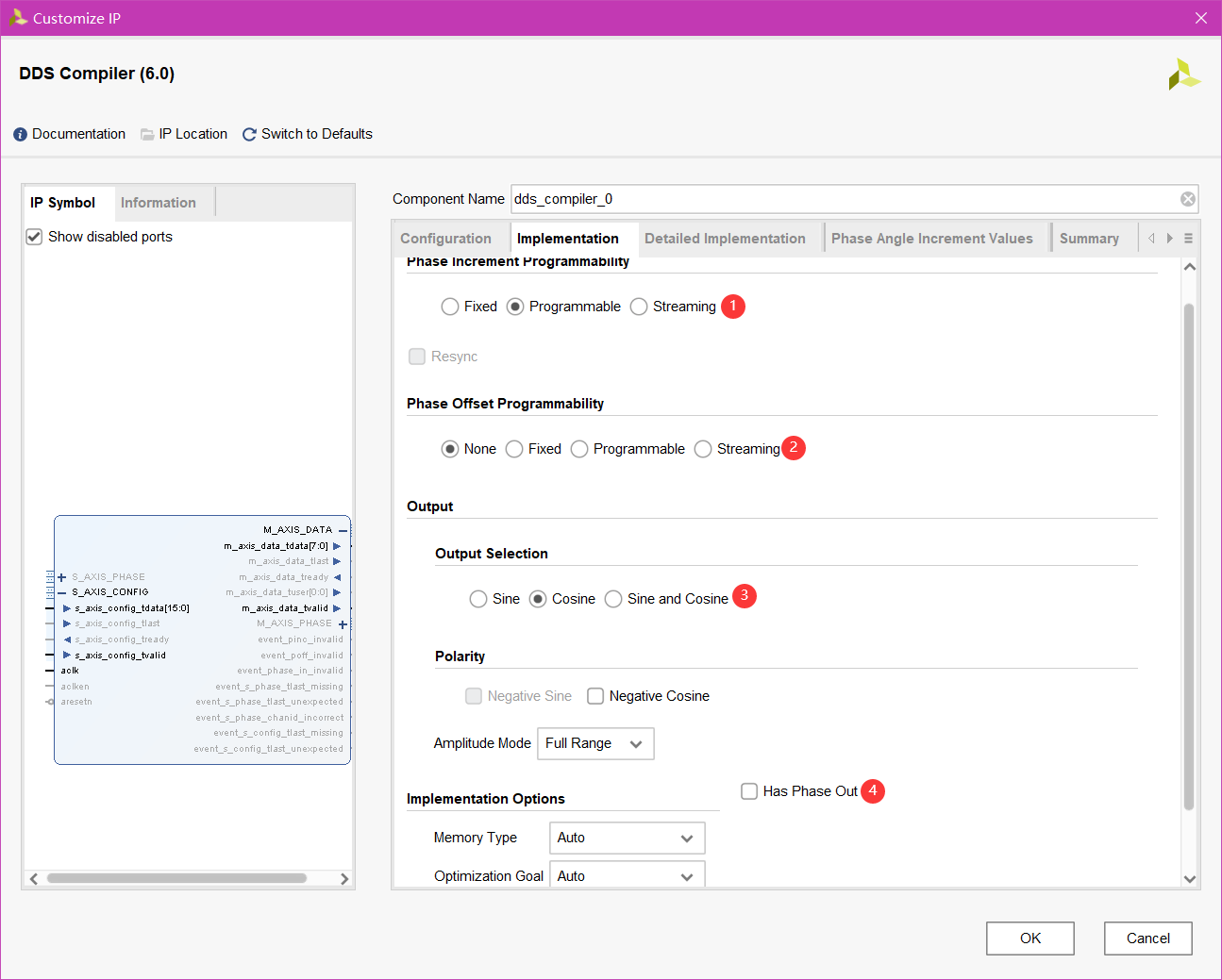

Implementation界面需要配置这四点。

1.选择可编程阶段增量(我觉得就是频率控制字的可编程。。)

2.相位偏移就不需要

3.输出波形为余弦波 [ AM调制公式:P(t)=(A+M_a cos(t_1 ) )×cos(t_2 ) ]

4.不需要相位输出

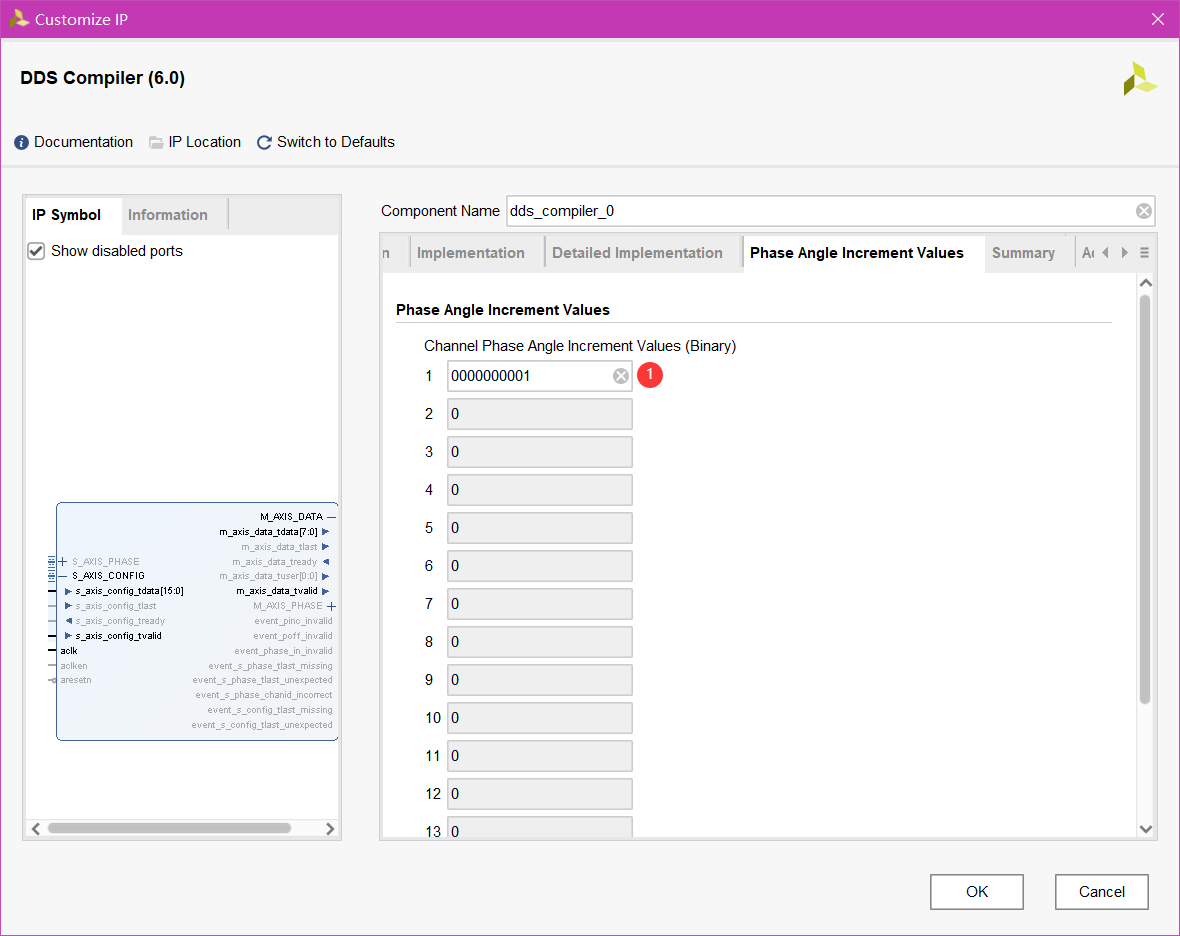

这个地方一开始是报错的,需要我们手动修改。前面我们的Phase Width为10,所以这个地方我们要配置为十位的二进制,这里为0000_0001。当这个界面没有报错的时候,左边的RTL的S_AXIS_CONFIG才会高亮。

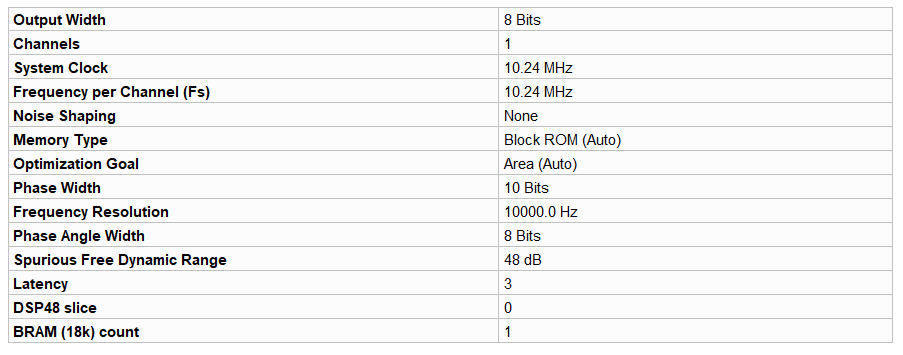

这是两个Summary的结果。

这是两个Summary的结果。

到此,DDS IP的用户界面就配置完了。

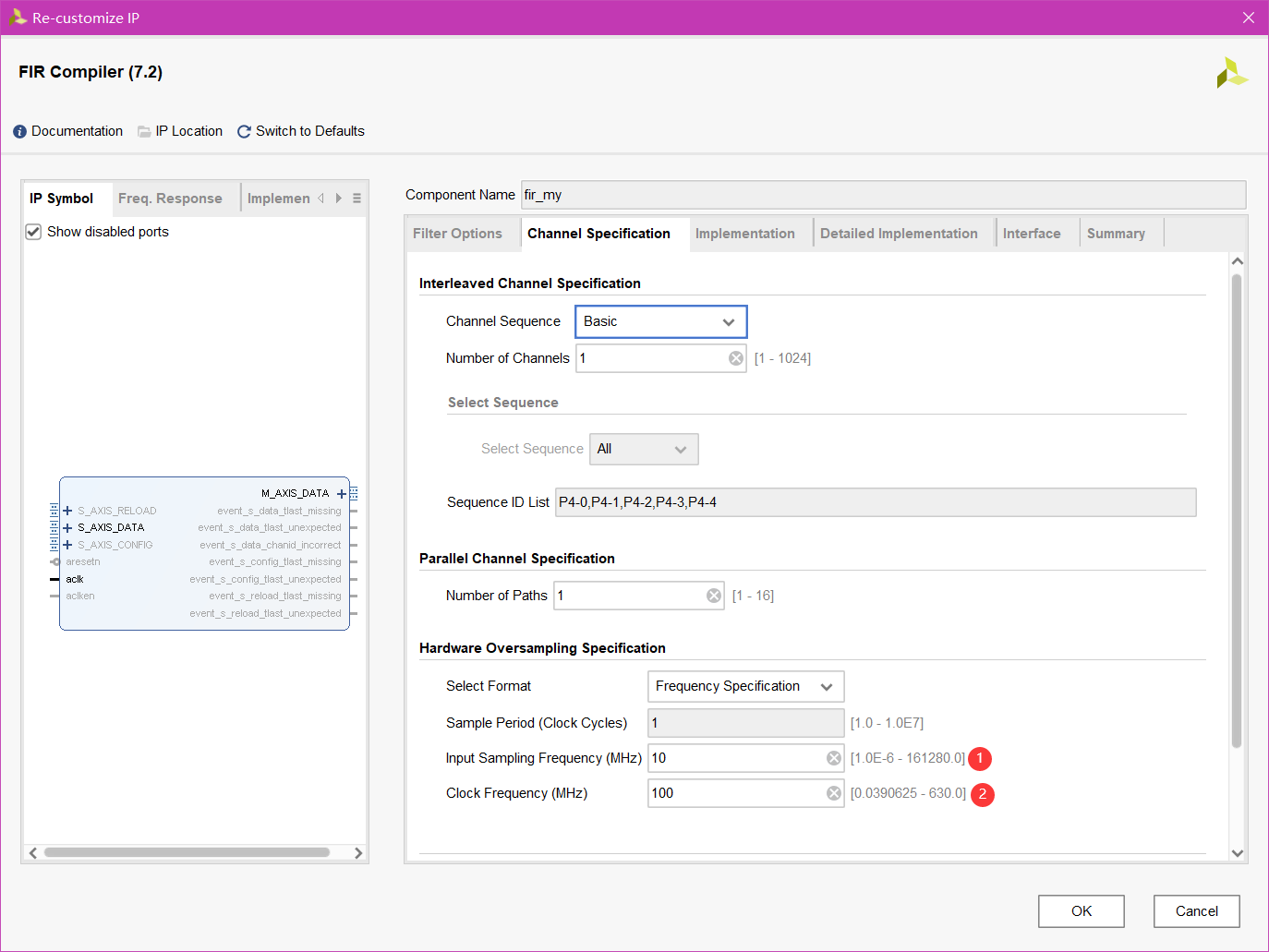

三、FIR滤波(用于后面AM解调)

FIR滤波器参数的生成

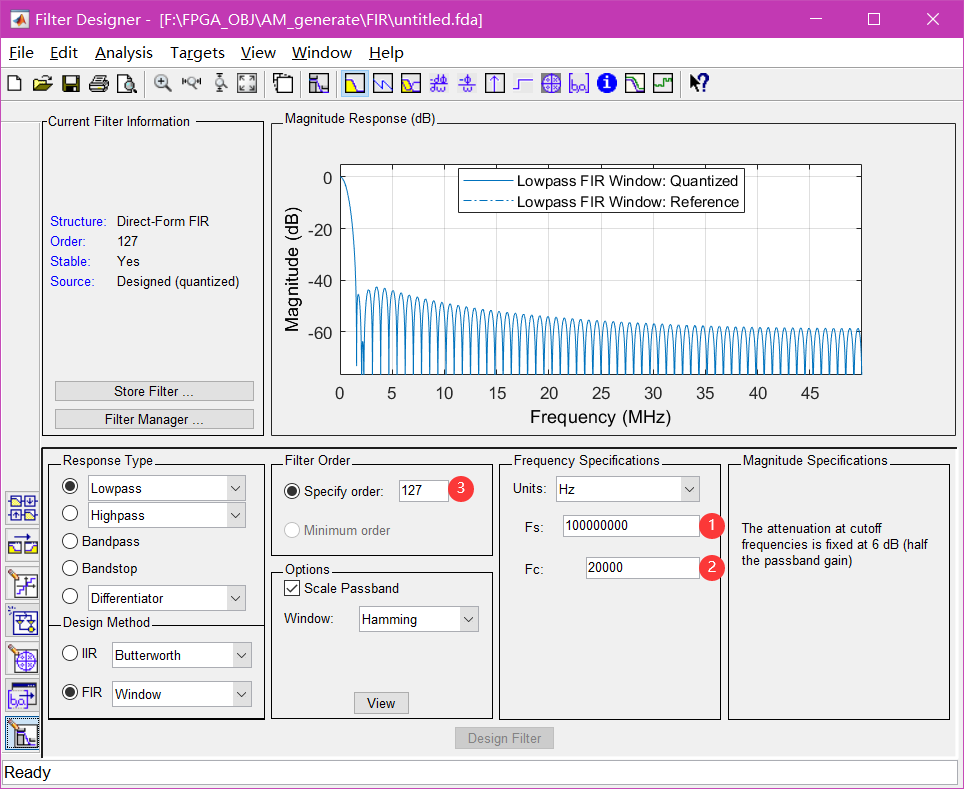

FIR滤波器的参数我用的MATLAB生成的,这里也顺带学习了一下MATLAB的Filter Designer工具。

1.采样频率我用的100MHz(后面发现100MHz程序运行太慢了。。。。),采样定律规定的是大于采样信号的2倍

2.这里截止频率我用的20KHz。调制信号为10KHz,所以大于10KHz就行,

但是如果有杂波,杂波频率在10KHz~1MHz之间的话,截止频率的要求就有点多了

3.滤波阶数为127

最后记得点击Design Filter,要不然那个波形不是这个滤波器的波形。

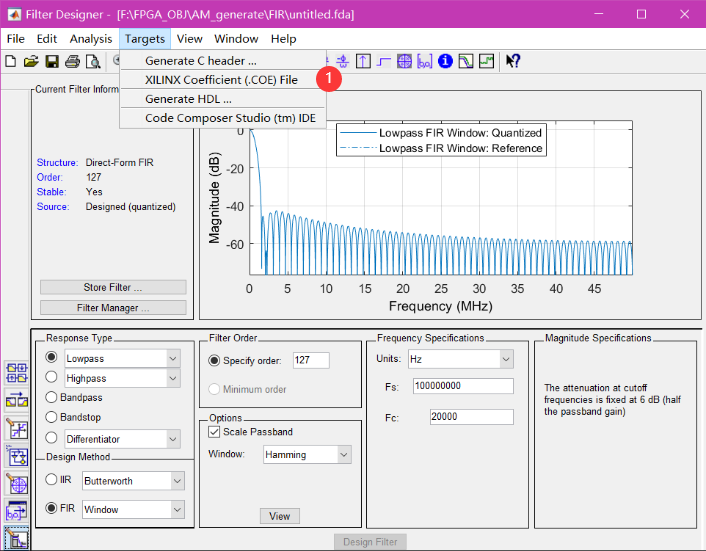

接下来生成.COE文件

FIR IP

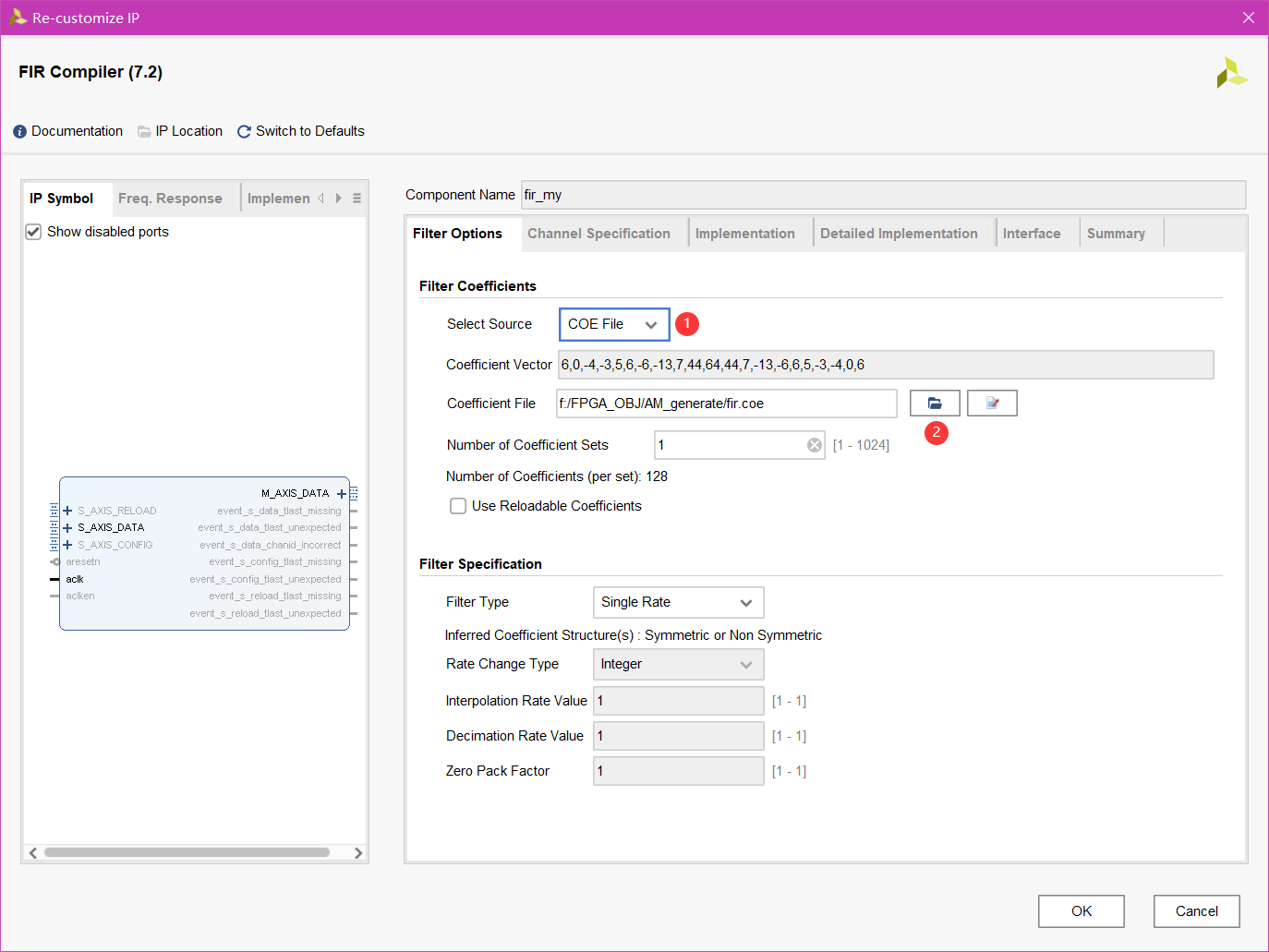

1.选择COE File

1.选择COE File

2.加载刚刚生成的.COE文件

1.输入的采样频率为10MHz(上面的100MHz改了,嘿嘿,10MHz我都嫌慢)

2.系统输入时钟

到此FIR的配置就完了。

四、AM调制

AM调制公式:P(t)=(A + M_a × cos(t_1) ) × cos(t_2)

其中当A=1时,调制深度就是M_a;cos(t_1 )为调制信号,cos(t_2)为载波。

为了好解释代码,上式变为(D + depth_con × cos(t_1) ) × cos(t_2)

代码如下(还是嫖别人代码香,嘿嘿,虽然不道德,但是掌握了知识就是自己的了,再次感谢开篇链接的两位博主):

reg [7:0] D = 127; //AM波直流分量

reg signed[7:0] depth_con;

always@(posedge clk_out) //设置调制深度

begin

case (depth)

0: depth_con <= 0 ; //调制深度为0,直流分量对应值

1: depth_con <= 13; //调制深度为0.1,直流分量对应值

2: depth_con <= 28; //调制深度为0.2,直流分量对应值

3: depth_con <= 45; //调制深度为0.3,直流分量对应值

4: depth_con <= 64; //调制深度为0.4,直流分量对应值

5: depth_con <= 85; //调制深度为0.5,直流分量对应值

6: depth_con <= 110; //调制深度为0.6,直流分量对应值

7: depth_con <= 138; //调制深度为0.7,直流分量对应值

8: depth_con <= 171; //调制深度为0.8,直流分量对应值

9: depth_con <= 209; //调制深度为0.9.,直流分量对应值

10: depth_con <= 255; //调制深度为1,直流分量对应值

endcase

end

wire signed[15:0] modulate_mul8ma;

wire signed[7:0] modulate_mulma;

mult_genx mult_floating_point (

.CLK(clk_out), // input wire CLK

.A(modulate_out), // input wire [7 : 0] A

.B(depth_con), // input wire [7 : 0] B

.P(modulate_mul8ma) // output wire [15 : 0] P

);

assign modulate_mulma = modulate_mul8ma>>8;

reg [7:0] modulate_withdc;

always@(posedge clk_out)

begin

modulate_withdc <= modulate_mulma + D;

end

mult_gen_0 mult_modulation (

.CLK(clk_out), // input wire CLK

.A(modulate_withdc), // input wire [7 : 0] A

.B(carrier_out), // input wire [7 : 0] B

.P(AM_out) // output wire [15 : 0] P

);

因为Verilog语言不能像C语言、python等等其他编程语言一样可以直接用浮点数,我们要做一些必要的处理完成浮点数计算的问题,所以depth = depth_con>>8(depth_con / 256)。但是代码并没有直接做这一步就计算,而是先将载波与depth_con相乘之后在>>8送给modulate_mulma。为了保证输出的数据都是16位宽的,这里modulate_mulma还加了一个127。这里的两个乘法器要注意一下他们输入参数是否有无符号位,否则计算出的已调制波有问题。

到此,调制就完了。

五、整体代码

代码如下(还是嫖别人代码香,嘿嘿,虽然不道德,但是掌握了知识就是自己的了,再次感谢开篇链接的两位博主):

`timescale 1ns / 1ps

module AM_generate_top(

input sysclk

);

wire [15:0] AM_out;

wire [3:0] depth= 9;

wire [15:0] carrier_con = 10;

wire [15:0] modulate_con = 1;

wire [7:0] carrier_out;

wire [7:0] modulate_out;

wire clk_out;

clk_div clk_1024k

(

// Clock out ports

.clk_out1(clk_out), // output clk_out1

// Clock in ports

.clk_in1(sysclk)); // input clk_in1

carrier_dds DDS_carrier(

.aclk(clk_out), // input wire aclk

.s_axis_config_tvalid(1), // input wire s_axis_config_tvalid

.s_axis_config_tdata(carrier_con), // input wire [15 : 0] s_axis_config_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(carrier_out) // output wire [7 : 0] m_axis_data_tdata

);

modulation_dds DDS_modulation(

.aclk(clk_out), // input wire aclk

.s_axis_config_tvalid(1), // input wire s_axis_config_tvalid

.s_axis_config_tdata(modulate_con), // input wire [15 : 0] s_axis_config_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(modulate_out) // output wire [7 : 0] m_axis_data_tdata

);

reg [7:0] A= 127; //AM波直流分量

reg signed[7:0] depth_con;

always@(posedge clk_out) //设置调制深度

begin

case (depth)

0: depth_con <= 0 ; //调制深度为0,直流分量对应值

1: depth_con <= 13; //调制深度为0.1,直流分量对应值

2: depth_con <= 28; //调制深度为0.2,直流分量对应值

3: depth_con <= 45; //调制深度为0.3,直流分量对应值

4: depth_con <= 64; //调制深度为0.4,直流分量对应值

5: depth_con <= 85; //调制深度为0.5,直流分量对应值

6: depth_con <= 110; //调制深度为0.6,直流分量对应值

7: depth_con <= 138; //调制深度为0.7,直流分量对应值

8: depth_con <= 171; //调制深度为0.8,直流分量对应值

9: depth_con <= 209; //调制深度为0.9.,直流分量对应值

10: depth_con <= 255; //调制深度为1,直流分量对应值

endcase

end

(* use_dsp48 = "yes" *) //这个没太大关系

wire signed[15:0] modulate_mul8ma;

wire signed[7:0] modulate_mulma;

mult_genx mult_floating_point ( //调用乘法IP核,就是进行前面说的得到小数的那一部分操作

.CLK(clk_out), // input wire CLK

.A(modulate_out), // input wire [7 : 0] A

.B(depth_con), // input wire [8 : 0] B

.P(modulate_mul8ma) // output wire [15 : 0] P

);

assign modulate_mulma = modulate_mul8ma>>8;

reg [7:0] modulate_withdc;

always@(posedge clk_out)

begin

modulate_withdc <= modulate_mulma + A;

end

mult_gen_0 mult_modulation ( //与载波相乘

.CLK(clk_out), // input wire CLK

.A(modulate_withdc), // input wire [7 : 0] A

.B(carrier_out), // input wire [7 : 0] B

.P(AM_out) // output wire [15 : 0] P

);

reg [15:0] AM_abs;

always @(posedge clk_out) begin

if(AM_out[15] == 1) begin //全波整流

AM_abs <= -{AM_out}; //如果符号位是1,对数据取反

end

else if(AM_out[15] == 0) begin

AM_abs <= AM_out; //如果符号位是0,数据不变

end

end

wire [39:0] demolate_signal;

fir_my fir ( //低通滤波

.aclk(sysclk), // input wire aclk

.s_axis_data_tvalid(1), // input wire s_axis_data_tvalid

.s_axis_data_tready(), // output wire s_axis_data_tready

.s_axis_data_tdata(AM_abs), // input wire [15 : 0] s_axis_data_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(demolate_signal) // output wire [39 : 0] m_axis_data_tdata

);

wire [7:0] demolate_final;

assign demolate_final[7:0] = demolate_signal[35:28]; //截位

endmodule

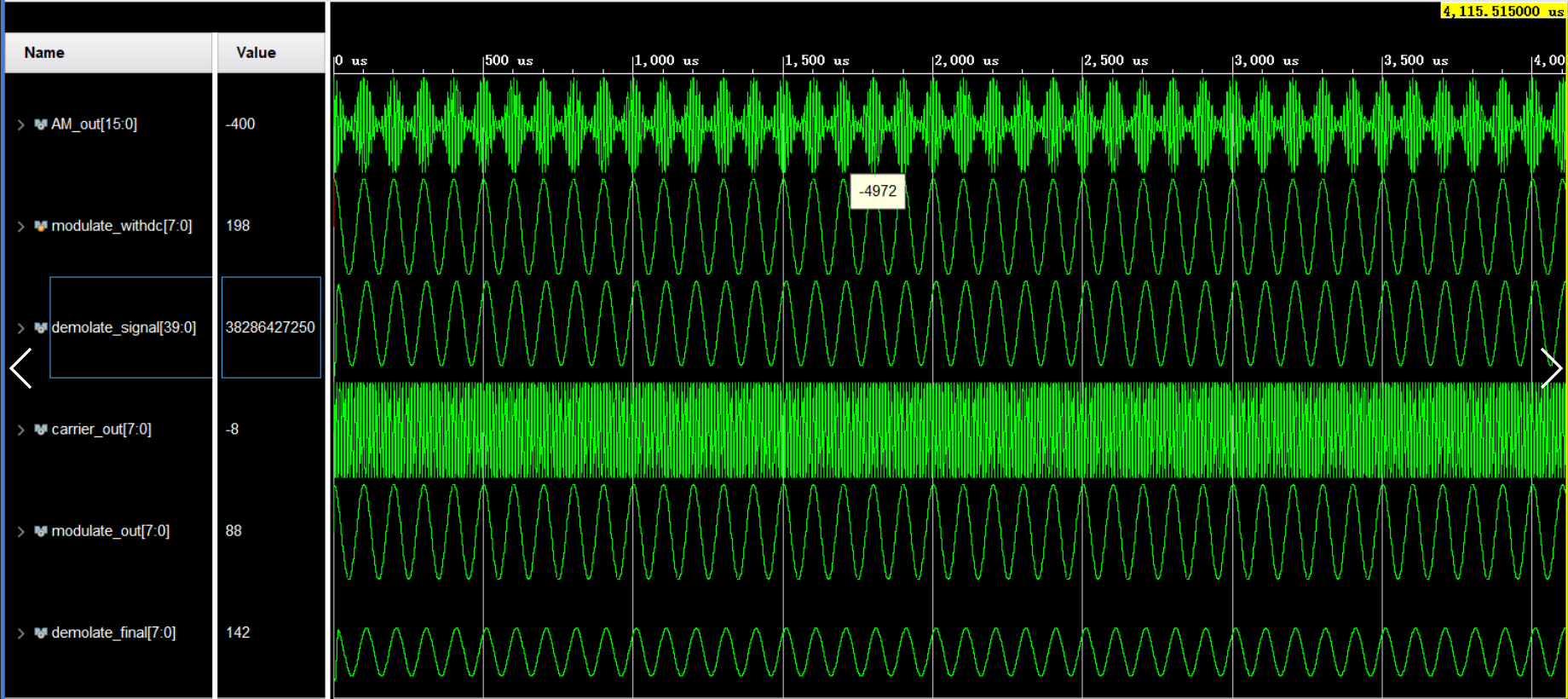

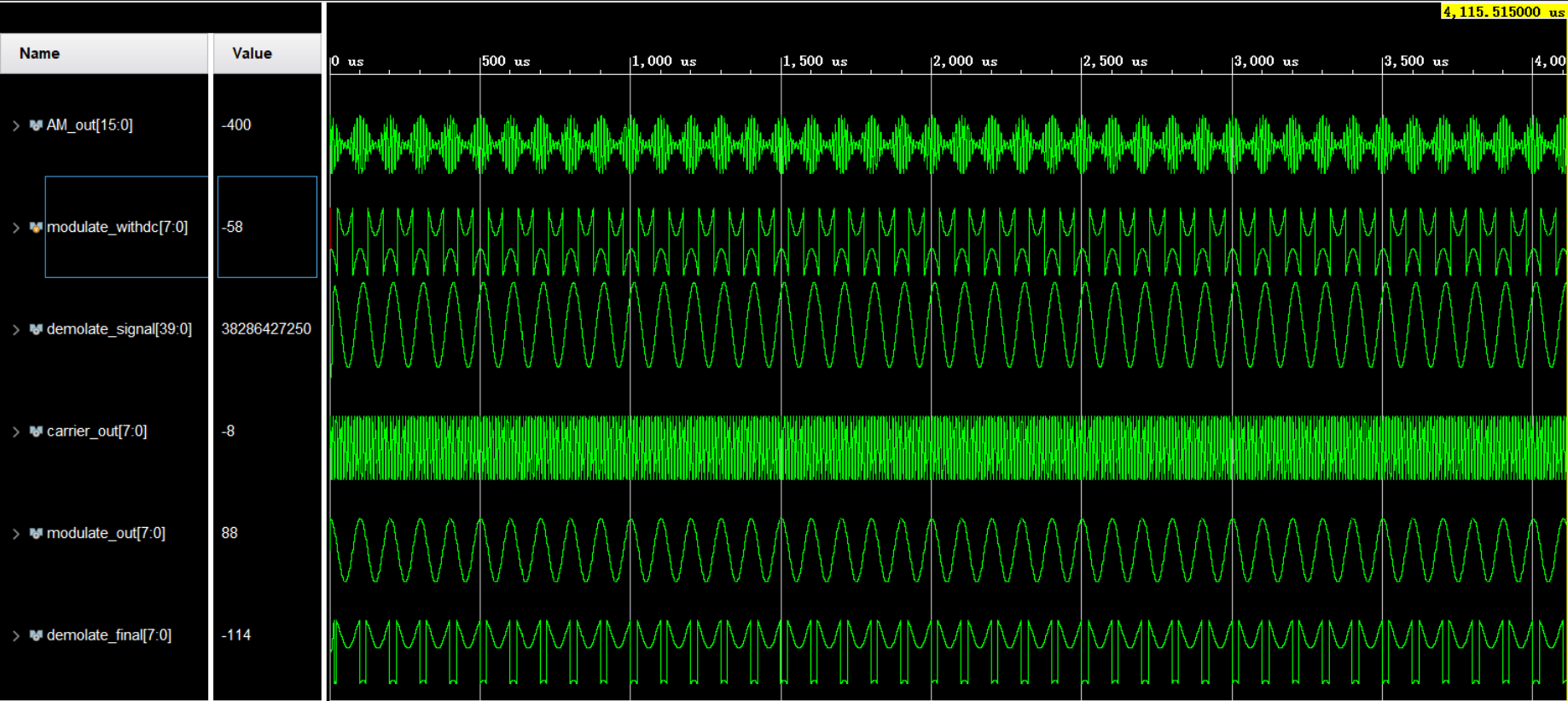

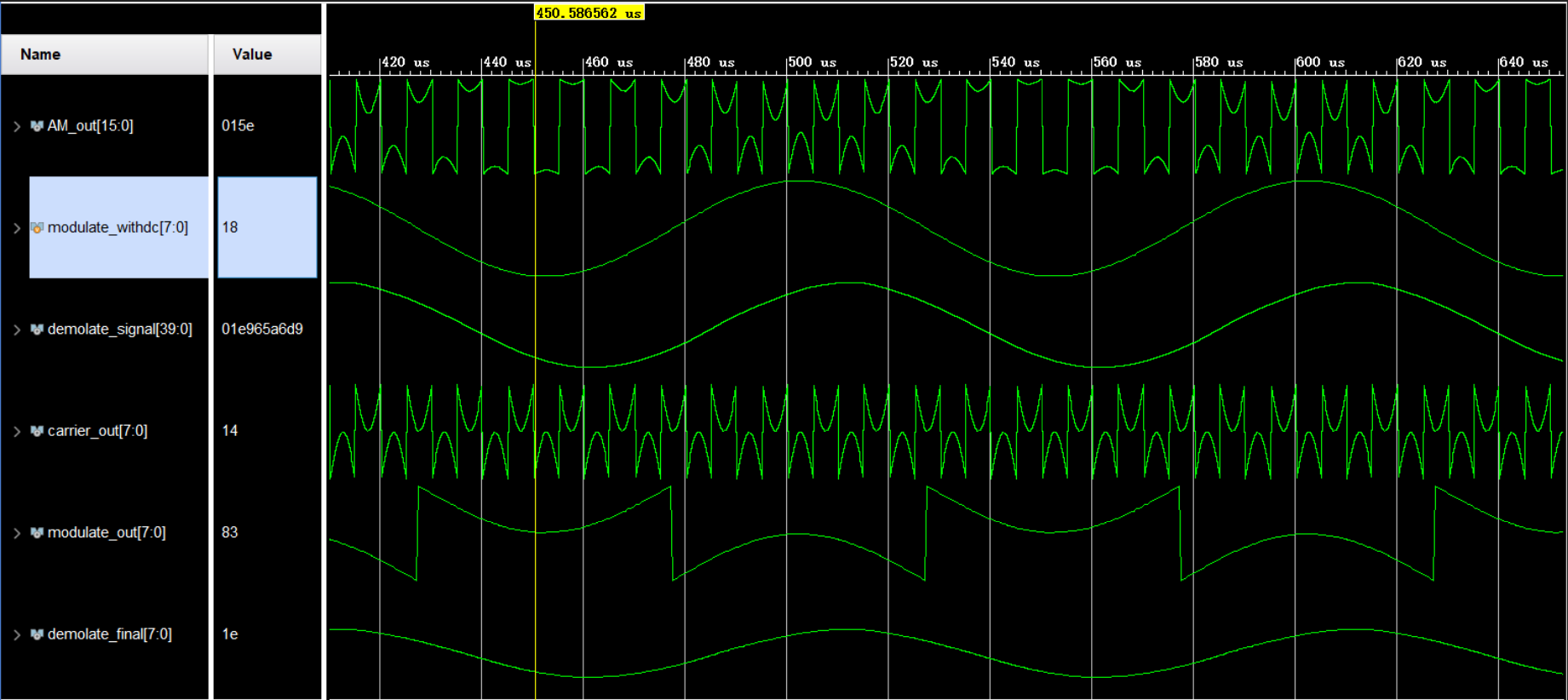

六、仿真波形

这里有两张有意思的:

其实都是没问题的,就是有个小地方没搞对。

其实都是没问题的,就是有个小地方没搞对。

总结

这次AM调制与解调的学习是建立在我没有相关专业基础知识上,所以我最多只能理解到AM调制和解调的算法,但是并没有深入理解到它的内涵。不过在这个过程中学到了如何配置DDS和FIR的IP我觉得也挺值得的,万一明年电赛用到了呢?对吧。看着仿真的波形就得很美妙(特别是那个AM_out),我体会到了FPGA功能的另一种美以及信号处理的乐趣。(个人能力有限,有问题的话请大佬指明出来,我去学习)

(我还是想说一下那个解调:我的理解就是全波整流之后,做低通把那个10KHz的信号给留下来了,不知道是不是这个意思。)

最后

以上就是安详口红最近收集整理的关于FPGA学习积累之AM调制解调(解调部分没搞太明白)随便说说一、平台二、DDS IP的使用三、FIR滤波(用于后面AM解调)四、AM调制五、整体代码六、仿真波形总结的全部内容,更多相关FPGA学习积累之AM调制解调(解调部分没搞太明白)随便说说一、平台二、DDS内容请搜索靠谱客的其他文章。

发表评论 取消回复