参考http://www.cnblogs.com/IClearner/p/6440488.html

一:时钟/时钟树的属性

1:时钟树:

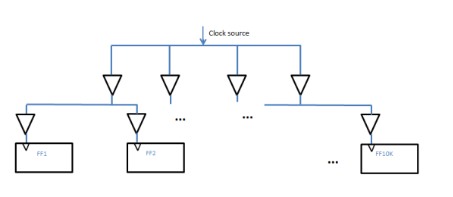

一般的时钟,我们都指的是全局时钟,全局时钟在芯片中的体现形式是时钟树。

时钟树,是个由许多缓冲单元(buffer cell)平衡搭建的时钟网状结构,如下图所示:

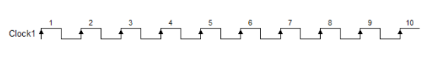

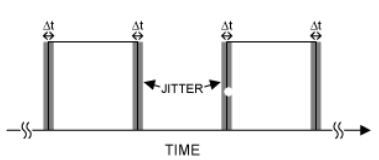

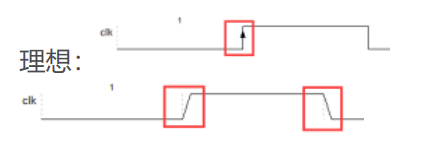

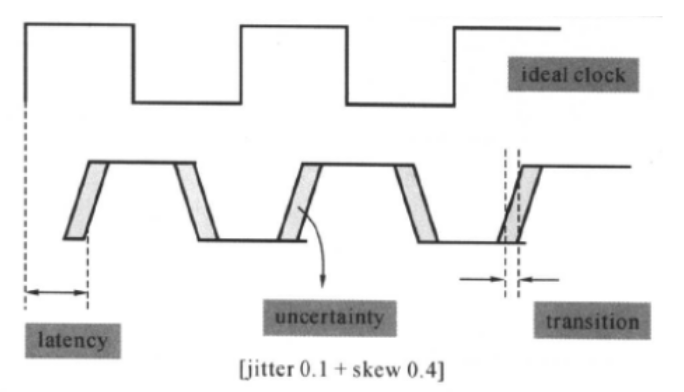

首先不得不说,实际的时钟除了周期/频率、相位、沿、电平属性外,还有其他的属性,也就是:不是下面这样子规规整整的:

为什么呢?那是因为时钟有下面的属性(“实际的buff”):

2:时钟属性

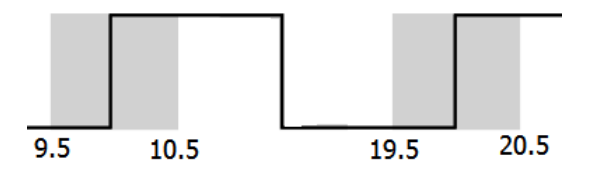

①时钟的偏移(skew):时钟分支信号在到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。时钟的偏移如下图所示:此外,时钟skew与时钟频率并没有直接关系,skew与时钟线的长度及被时钟线驱动的时序单元的负载电容、个数有关。

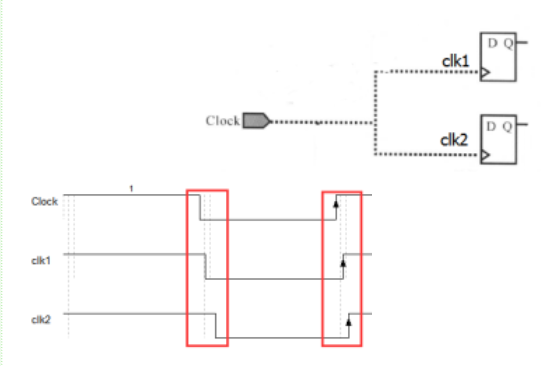

②时钟抖动(jitter):相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动,如下图所示:

时钟的抖动可以分为随机抖动(Random Jitter,简称Rj)和固有抖动(Deterministic jitter):

·随机抖动的来源为热噪声、Shot Noise和Flick Noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动;

·固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。

也就是说:jitter与时钟频率无直接关系。

时钟的偏移和时钟的抖动都影响着时钟网络分枝的延迟差异(相位差异),在Design Compiler里面,我们用时钟的不确定性(uncertainty)来表示这两种情况的影响。

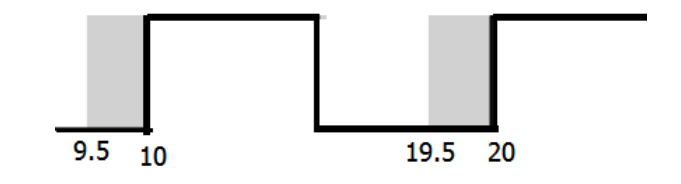

③时钟的转换时间(transition) :时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间,这个时间并不是如左下图所示那样完全没有跳变时钟的,而是像右下图那样,时钟沿的跳变时间就是时钟的转换时间(后面约束的时候会有相关的解释)

时钟的转换时间与与单元的延时时间(也就是器件特性)还有电容负载有关。

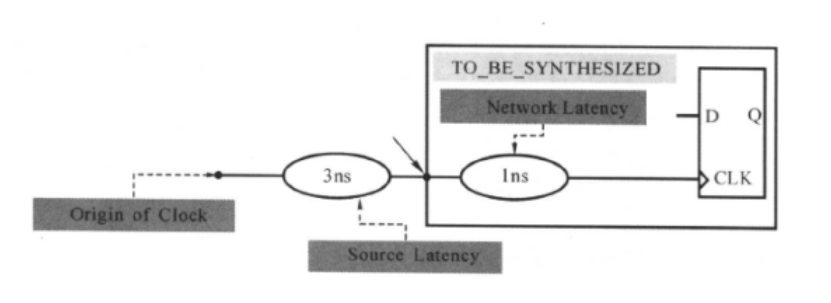

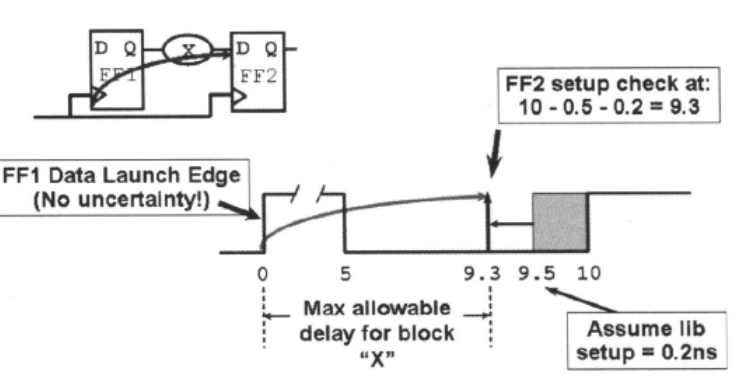

④时钟的延时(latency) :时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency),如下图所示:

时钟源延迟(clock source latency),也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间,上图是3ns。

时钟网络的延迟( clock network latency)是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency),上图是1ns。

二:DC中的时钟约束

我们用下面的命令建立时钟那几个属性模型:

create_cloclk、set_clock_uncertainty、set_clock_latency、set_clock_transition分别进行时钟的周期、偏移、延时、转换约束。

1:时钟偏差的建模

set_clock_uncertainty:对时钟的偏移与抖动进行建模,也就是对时钟的偏差进行建模。

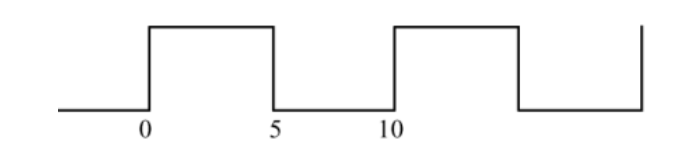

create_clock -period 10 [get_ports CLK]

set_ clock_ uncertainty -setup 0.5 [get_clocks CLK]

理想的时钟

只对建立时间的偏差时钟建模

对建立时间和保持时间都进行偏差建模

在默认的情况下,"set-clock_uncertainty”命令如果不加开关选项“-setup”或“-hold",那么该命令给时钟赋予相同的建立和保持偏差值。

这是一种对偏差建模的方式,也就是对建立时间和保持时间进行建模的方式;除此之外,还可以对时钟的上升沿和下降沿进行偏差建模,比如上升沿的偏差是0.2ns,下降沿的偏差是0.5ns,则有:

set_ clock_ uncertainty -rise 0.2 -fall 0.5 [get_clocks CLK]

一般情况下,我们只约束建立时间,也就是只用第一种方式进行时钟偏差建模。

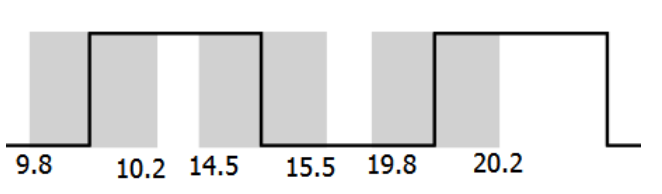

当对建立时间偏差建模之后,这时,时钟周期、时钟偏差和建立时间的关系如下图所示

假设时钟周期是10ns,建立时间偏差是0.5ns,触发器的建立时间是0.2ns,这时候从图中就可以看到,留给寄存器间的路径的裕量就减少了,也就是说,对寄存器间的约束就变得更加严格了,寄存器的翻转延时、组合逻辑延时与线网延时等这些延时的和必须小于9.3ns,否则就违反了FF2的建立时间。这一点是要注意的。

2:时钟转换时间的建模

由于时钟并不是理想的方波,用set_ clock_ transition来模拟时钟的转换(transition)时间。默认的上升转换时间为从电压的20%上升至80%的时间,下降的转换时间为从电压的80%下降至20%的时间。如果set_clock_transition命令中不加开关选项“-setup”或“-hold" ,那么该命令给时钟赋予相同的上升和下降转换时间。一般情况下,我们只约束最大的转换时间,如最大转换时间是0.2ns,那么就加上-max选项:

set_clock_transition -max 0.2 [get_clocks CLK]

3:时钟延迟的建模

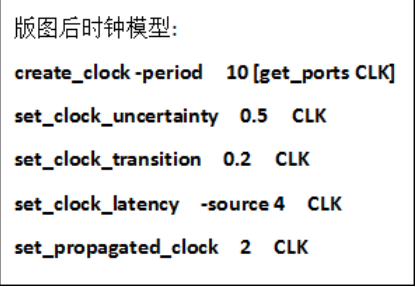

时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency)。我们使用set_clock_latency进行时钟延时的建模。一般情况下,我们把时钟源延迟(source latency)和时钟网络的延迟(network latency)分开来,因为时钟源延时需要建模,是因为DC是真的不知道这延时是多大,但是对于时钟网络的延迟,DC在布局布线前不知道,但是在布局布线后就可以计算出来时钟网络的延时了,因此在布局布线之后进行综合时,就没有必要对时钟网络进行延时,因此就要把这两个延时分开来进行约束。

先说布局布线之前:时钟周期为10ns,时钟源到芯片的时钟端口时间是3ns,时钟端口都内部触发器的时间是1ns,如下图所示,

那么就用下面的命令进行建模:

create_clock -period 10 [get-ports CLK]

set_clock_latency -source 3 [get_clocks CLK]

set_clock_latency 1 [get_clocks CLK]

布局布线之后:就可以计算实际的线网延时,就要使用

set_propagated_clock [ get_clocks CLK]

set_clock_latency 1 [get_clocks CLK]这个命令代替上面的命令。

3:总结

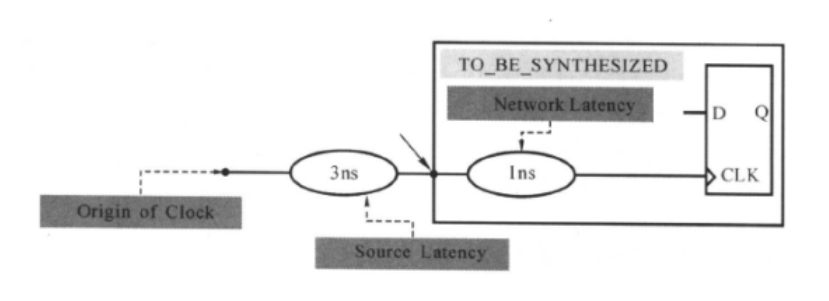

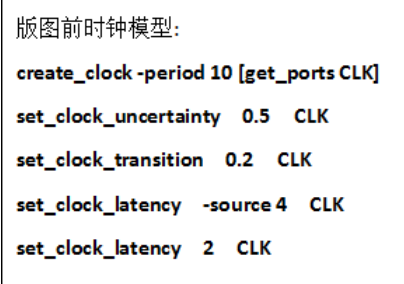

基本的时钟建模就OK了,下面进行总结并给出我们这个例子中使用的约束脚本,理想时钟和实际时钟的对比,如下图所示:

因此总结就是,对实际时钟的建模/约束如下所示:

转载于:https://www.cnblogs.com/xh13dream/p/8687274.html

最后

以上就是斯文大门最近收集整理的关于DC学习(6)基本时序约束之路径2时钟的建模与约束的全部内容,更多相关DC学习(6)基本时序约束之路径2时钟内容请搜索靠谱客的其他文章。

发表评论 取消回复