文章目录

- 组合逻辑电路

- 多路选择器

- 译码器

- 编码器

- 比较器

- 数据扩展器

- 时序逻辑电路

- 锁存器

- SR锁存器

- En锁存器

- D锁存器

- 触发器

组合逻辑电路

特点:是任意时刻的输出仅仅取决于当前时刻的输入,与电路之前的历史状态无关(即无记忆能力)

组合逻辑电路的设计通常包含以下几个步骤:

- 进行逻辑抽象。分析事件的因果关系,确定输入变量和输出变量,列出输入变量和输出变量的逻辑真值表。

- 写出逻辑函数。将真值表转换为对应的逻辑函数式,或者直接画出卡诺图,然后使用第三章中介绍的卡诺图将逻辑函数进行化简。

- 根据化简后的逻辑函数,画出逻辑电路图。

常见的组合逻辑电路:多路选择器、编码器、译码器、移位器、比较器、

多路选择器

最简单的多路选择器(Multiplexer)是1位二选一多路器。

当输入S为高电平时,输入Y的值为输入A1的值;

当输入S为低电平时,输入Y的值为输入A0的值。

四选一多路选择器代码

module MUX4X32 (A0, A1, A2, A3, S, Y);

input [31:0] A0, A1, A2, A3;

input [1:0] S;

output [31:0] Y;

function [31:0] select;

input [31:0] A0, A1, A2, A3;

input [1:0] S;

case (s)

2ˊb00: select = A0;

2ˊb01: select = A1;

2ˊb10: select = A2;

2ˊb11: select = A3;

endcase

endfunction

assign y = select (A0, A1, A2, A3, S);

end module

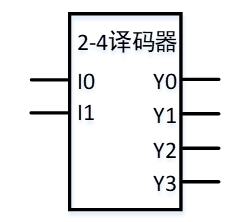

译码器

module DEC2T4 (I0, I1, Y0, Y1, Y2, Y3);

input I0, I1;

output Y0, Y1, Y2, Y3;

not i0 (I0_n, I0);

not i1 (I1_n, I1);

nor i2 (Y0, I0, I1);

nor i3 (Y1, I0, I1_n);

nor i4 (Y2, I0_n, I1);

nor i5 (Y3, I0_n, I1_n);

endmodule

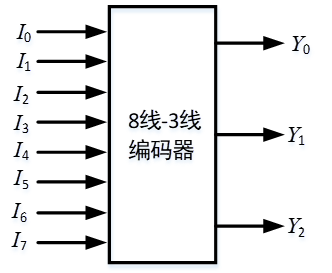

编码器

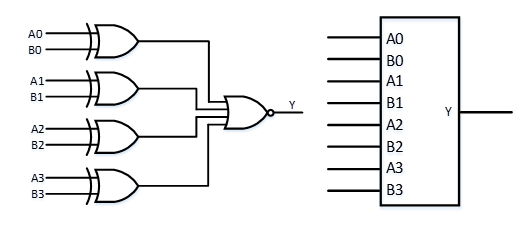

比较器

把比较输入信号之间是否相等的电路叫做比较器(Comparator):如果两个输入向量相等,则输出高电平,否则输出低电平

module CPT4 (A, B, Y);

input [3:0] A, B;

output Y;

xor i0 (D0, A[0], B[0]);

xor i1 (D1, A[1], B[1]);

xor i2 (D2, A[2], B[2]);

xor i3 (D3, A[3], B[3]);

nor i4 (Y, D0, D1, D2, D3);

endmodule

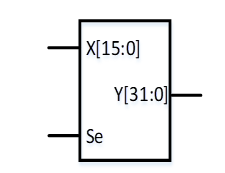

数据扩展器

对数据进行符号扩展或零扩展

module EXT16T32 (X, Se, Y);

input [15:0] X;

input B;

output Y;

wire [31:0] E0, E1;

wire [15:0] e = {16{X[15]}};

parameter z = 16ˊb0;

assign E0 = {z, X};

assign E1 = {e, X};

MUX2X32 i(E0, E1, Se, Y);

endmodule

时序逻辑电路

组合逻辑电路的特点是任意时刻的输出仅仅取决于当前时刻的输入,与电路之前的历史状态无关;

而时序逻辑电路的 输出不仅取决于当前的输入,还取决于电路的历史状态。 因此我们需要一种元件能保存电路的状态信息。如果一个元件带有内部存储功能,它就包含状态,也称之为状态单元(State Element)。

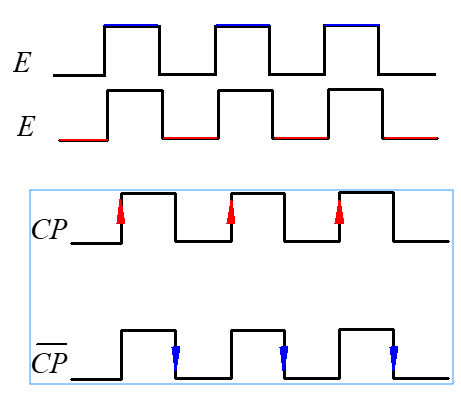

- 锁存器:锁存器在E的高(低)电平期间对信号敏感

- 触发器:触发器在CP的上升沿(下降沿)对信号敏感

共同点:具有0 和1两个稳定状态,一旦状态被确定,就能自行保持。一个锁存器或触发器能存储一位二进制码。

不同点:

- 锁存器—对脉冲电平敏感的存储电路,在特定输入脉冲电平作用下改变状态。

- 触发器—对脉冲边沿敏感的存储电路,在时钟脉冲的上升沿或下降沿的变化瞬间改变状态。

常见的时序逻辑元件:锁存器、

锁存器

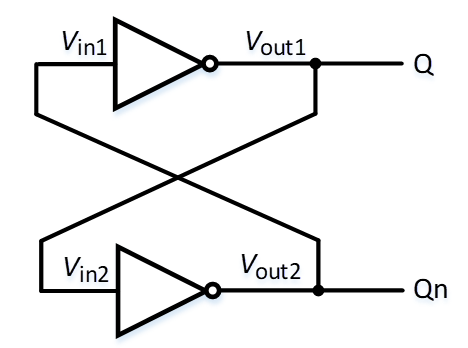

最简单的时序电路由一对反相器形成一个双稳态元件,如图所示。该元件具有两个稳定状态,只要一接上电源,它就随机出现两种状态中的一种,并永久保持这一状态。

若Q为高电平输出,则Vin2为高电平输入,Qn输出低电平,同时Vin1也为低电平输入,又使得Q继续保持高电平输出;

若Q为低电平输出,则Vin2为低电平输入,Qn输出高电平,同时Vin1也为高电平输入,又使得Q继续保持低电平输出;

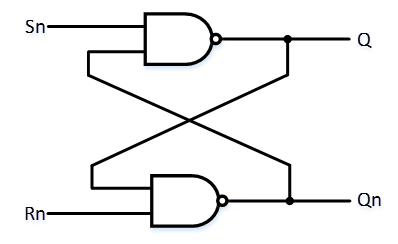

SR锁存器

上述双稳态元件虽然可以持续保存电路的状态信息,但是缺点是不能根据我们的需求去修改存储的信息。因此我们还需要其他的元件来实现我们的需求。

- 当Sn为输入高电平,Rn为输入低电平时,Qn输出为高电平,Q输出为低电平;

- 当Sn为输入低电平,Rn为输入高电平时,Q输出为高电平,Qn输出为低电平;

- 当Sn为输入低电平,Rn为输入低电平时,Q输出为高电平,Qn输出为高电平;

- 当Sn为输入高电平,Rn为输入高电平时,此时电路的特性就像一个双稳态元件,但是电路的输出只能维持Q和Qn处于输出相反电平的逻辑状态。

| Sn | Rn | Q | Qn |

|---|---|---|---|

| 1 | 1 | 维持不变 | 维持不变 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 |

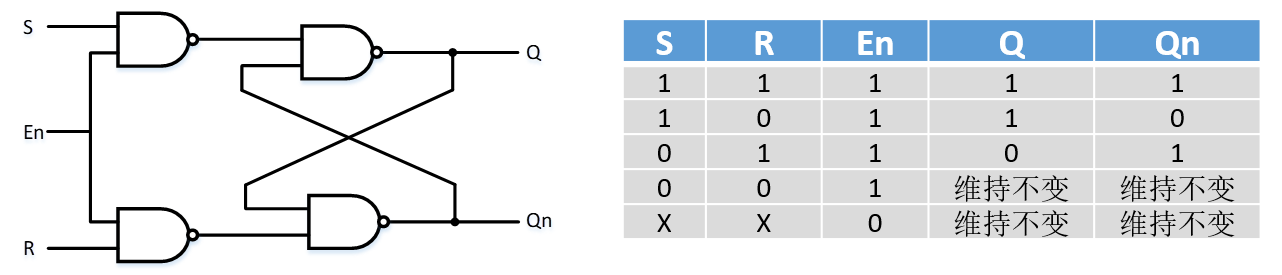

En锁存器

由于Sn-Rn锁存器对两个输入端的电平信号是一直敏感的,我们需要在Sn-Rn锁存器的基础上增加一个输入使能端En,使得输出只在使能端En为输入高电平时才对输入端的电平敏感。

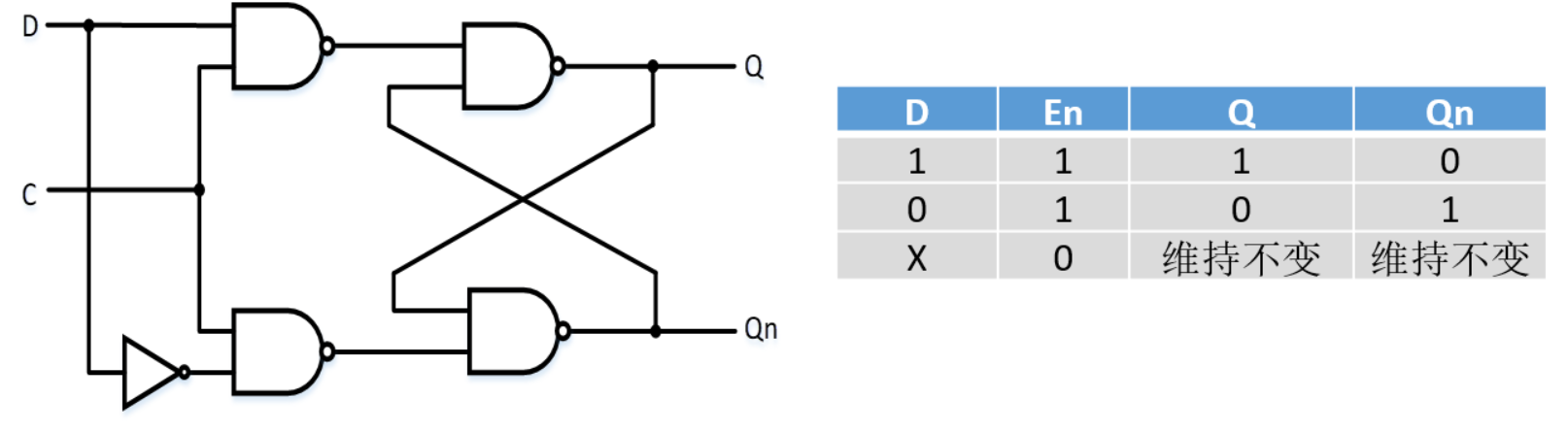

D锁存器

可在带输入使能端的Sn-Rn锁存器的基础上略作修改,使得修改后的元件能够保存一个二进制位的状态信息。我们把这种修改后的锁存器叫做D锁存器(D Latch)。

module D_Latch (D, En, Q, Qn);

input D, En;

output Q, Qn;

wire Sn, Rn, Dn;

not i0 (Dn, D);

nand i1 (Sn, D, En);

nand i2 (Rn, En, Dn);

nand i3 (Q, Sn, Qn);

nand i4 (Qn, Q, Rn);

//这两行代码实现的是Sn-Rn锁存器

endmodule

触发器

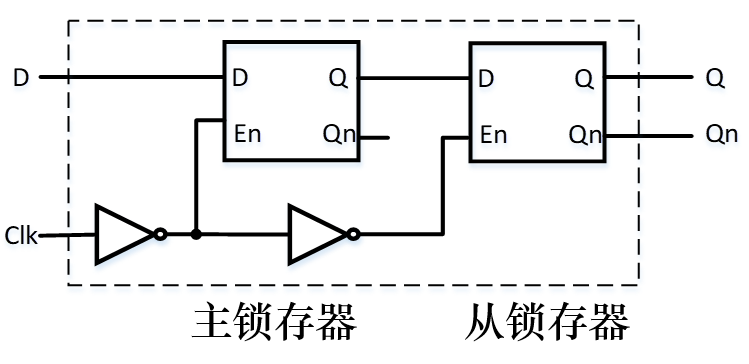

D锁存器已经能够保存一个二进制位的状态信息,并且能够在输入使能端为高电平时改变其存储的信息,即通过输入使能端的电平信号去控制D锁存器的开闭。

不过,在计算机芯片内部,我们往往需要通过输入的时钟边沿信号(时钟的上升沿或下降沿)去控制D锁存器的开闭,把这种用时钟边沿控制D锁存器中存储内容的元件叫做D触发器。

用两个D锁存器和两个非门构成了一个上升沿触发式D触发器

当Clk输入端为低电平时,主锁存器的En端为高电平输入,为打开状态;从锁存器的En端为低电平输入,为关闭状态。因此D触发器的输出端Q和Qn维持之前的状态信息。换句话说,此时D触发器中存储的信息是由从锁存器提供的。

当Clk输入端从低电平变为高电平时,主锁存器的En端从输入高电平变为低电平,即变为关闭状态,其输出端Q保持En端电平降低前的D端输入的电平信息;从锁存器的En端从输入低电平变为高电平,即变为打开状态,其输出Q端与其输入D端的电平信号一致。换句话说,D触发器在时钟信号的上升沿采样D端输入信号并保存在其主锁存器中。

当Clk输入端从高电平变为低电平时,主锁存器的En端从输入低电平变为高电平,即变为打开状态,其输出端Q`开始接收D端的输入电平并保持一致;从锁存器的En端从输入高电平变为低电平,即变为关闭状态,其输出端Q保持En端电平降低前的D端输入的电平信息。换句话说,D触发器在时钟信号的下降沿将其存储的信息从主锁存器移到从锁存器

最后

以上就是繁荣外套最近收集整理的关于组合逻辑电路 & 时序逻辑电路组合逻辑电路时序逻辑电路的全部内容,更多相关组合逻辑电路内容请搜索靠谱客的其他文章。

发表评论 取消回复