电位触发

- 在约定钟控信号电平(CP=1或CP=0)期间内,输入激励信号的变化 都会引起触发器状态的改变;

- 在约定钟控信号电平(CP=0或CP=1)期间外,无论输入激励信号如 何变化,触发器状态保持不变。

也就是说当且仅当约定期间内才引起变化.但根据电平持续时间的不同,一个电平区间内可能会有多次.这就引出了空翻的问题.

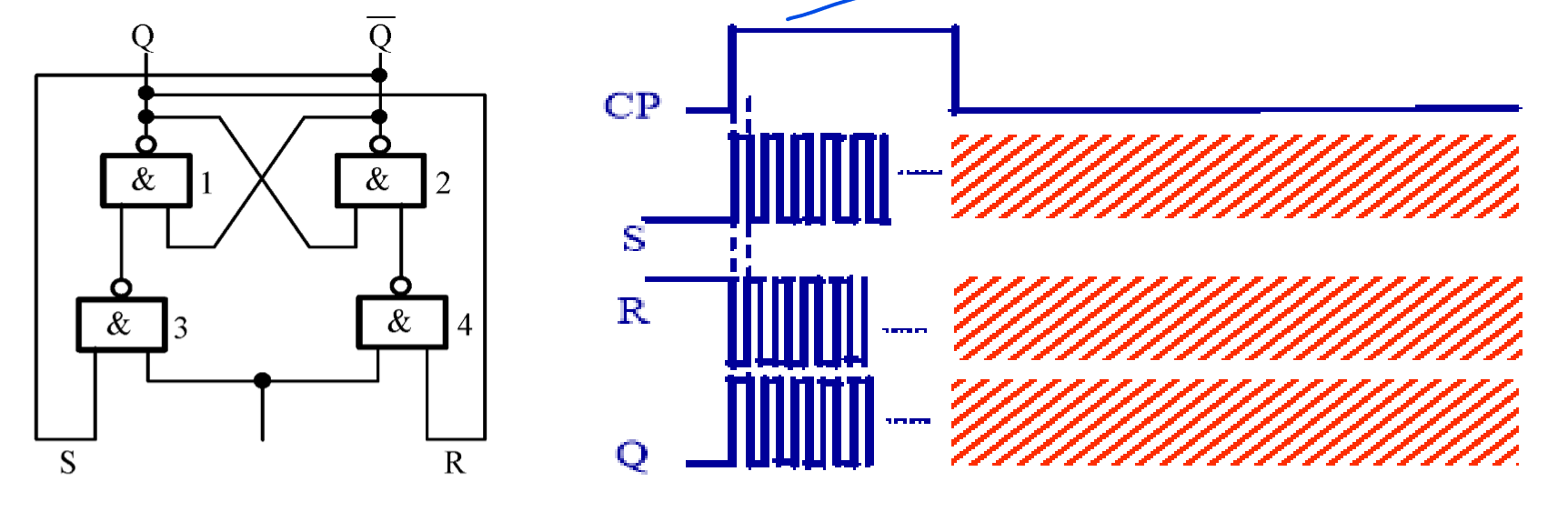

空翻:钟控RS的空翻现象

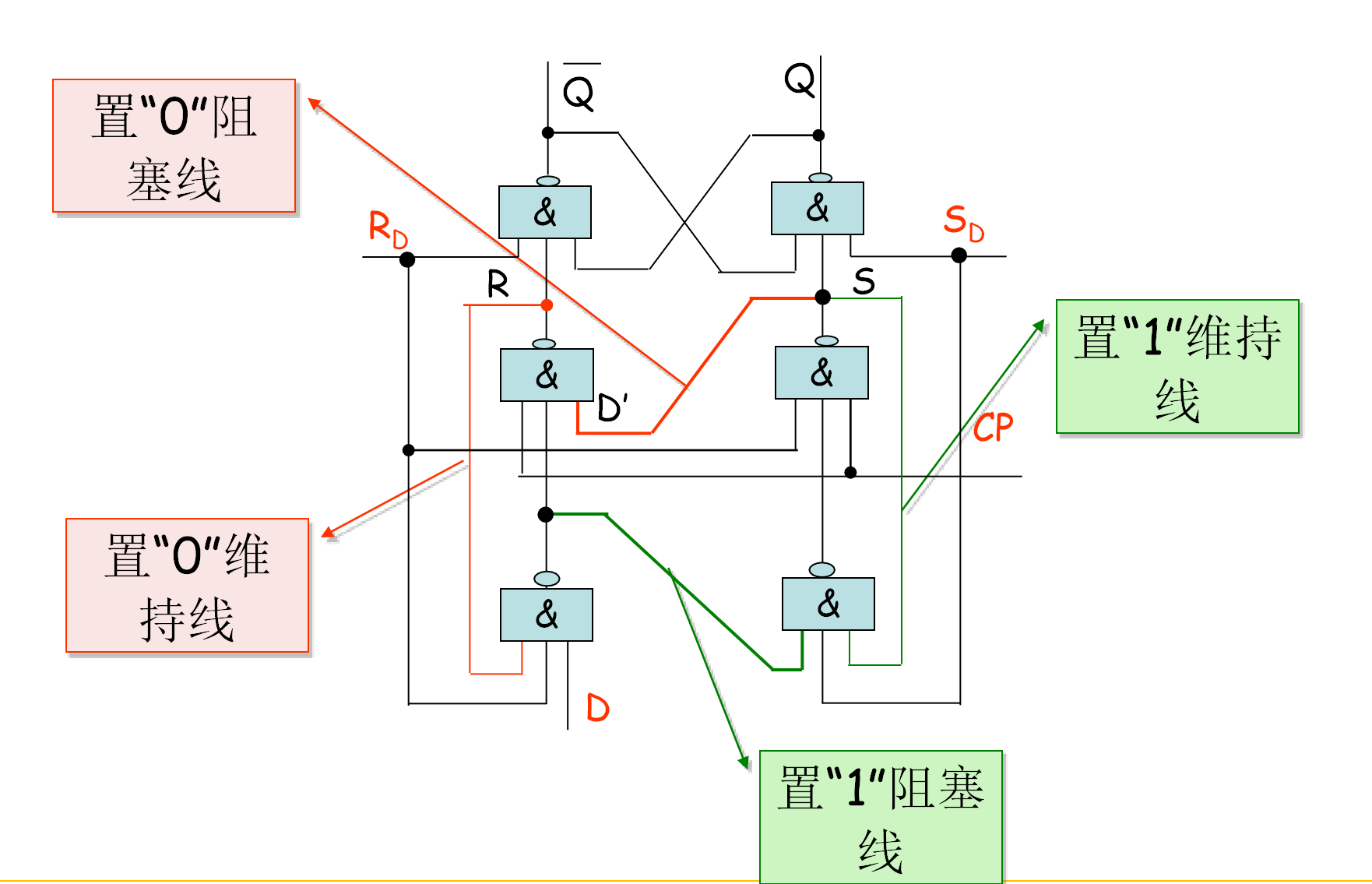

左图是钟控RS的电路图.当RS=1时开始工作(接受触发信号).

当一个时钟开放区间内有多次输入时,会使触发器的抗干扰能力下降.并且限制了触发器的使用范围(由于存在空翻现象,同步触发器无法完成计数、移位寄存等功能),也就是说时序上和时钟无法同步.

为解决这种问题引入了主从结构.

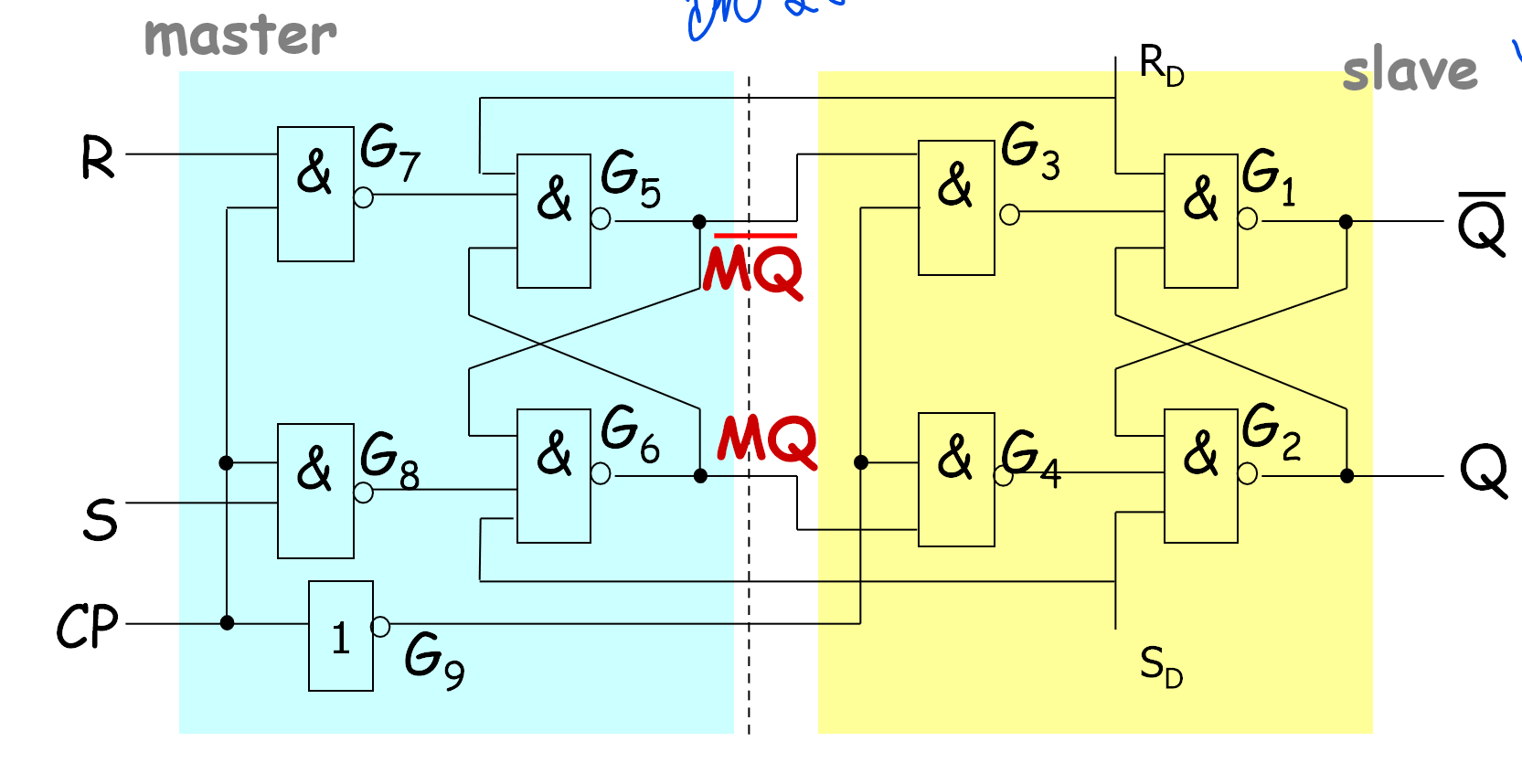

主从结构

主从触发器的工作机制

主从触发器的工作机制

“前沿采样,后沿定局”.

- 时钟脉冲上升沿开始,主触发器按其功能正常工作,从触发器被封锁

- 时钟脉冲下降沿开始,主触发器被锁定,其输出影响从触发器状态改变

注意,主从触发器的主体结构是一样的(RS),但是CP信号是完全相反.

CP上升沿,主触发器接收信号,从触发器闭锁.此时主触发器接收信号.

CP下降沿,从触发器接收,主触发器无输入(内部保持)

也就是说,在CP=0时从触发器保证只有一种输入(即CP=1区间的最后一组信号输入),从而避免了空翻的出现.

同时,RS-RS的结构也保证从触发器的两个输入始终相异,避免了1-1无效输入.(注意:输入的是

S

ˉ

,

R

ˉ

bar{S},bar{R}

Sˉ,Rˉ)(如果要保持,只用断掉时钟信号就行了.)

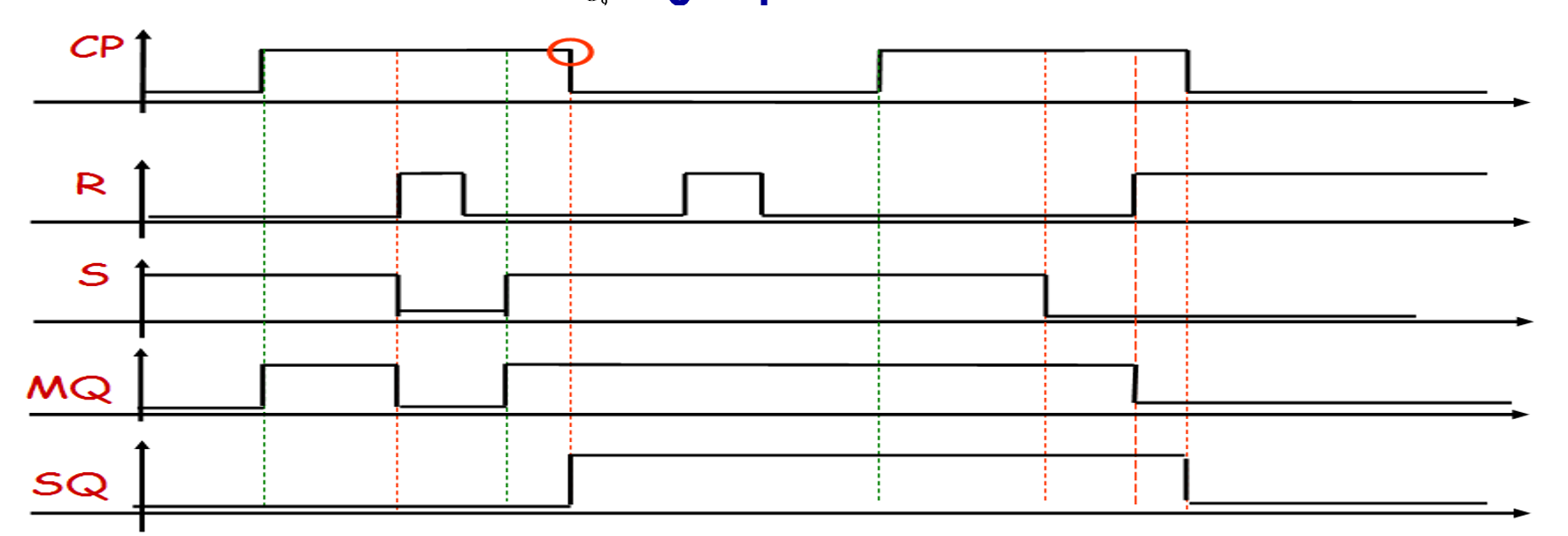

以下是主从RS触发器的信号图.

主从JK等触发器原理大致相同.就是两个相同触发器叠加但是钟控信号相反.

主从JK等触发器原理大致相同.就是两个相同触发器叠加但是钟控信号相反.

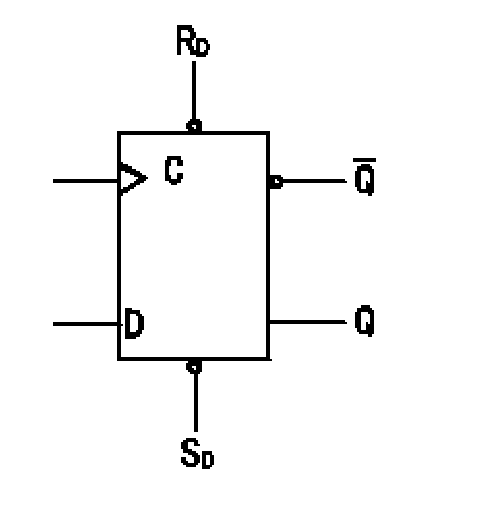

上面是主从D触发器的封装.SD是直接置1电路,RD是直接置0电路.(异步触发)

上面是主从D触发器的封装.SD是直接置1电路,RD是直接置0电路.(异步触发)

维持阻塞结构的D触发器

!

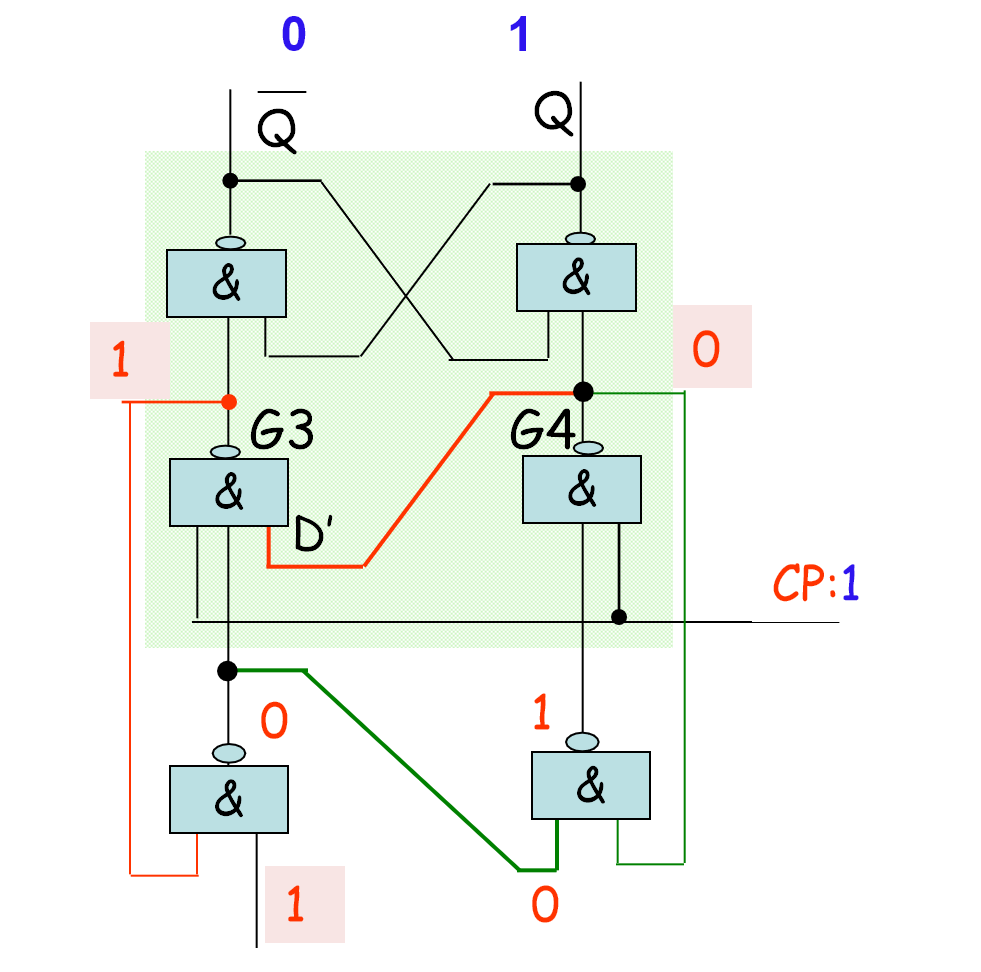

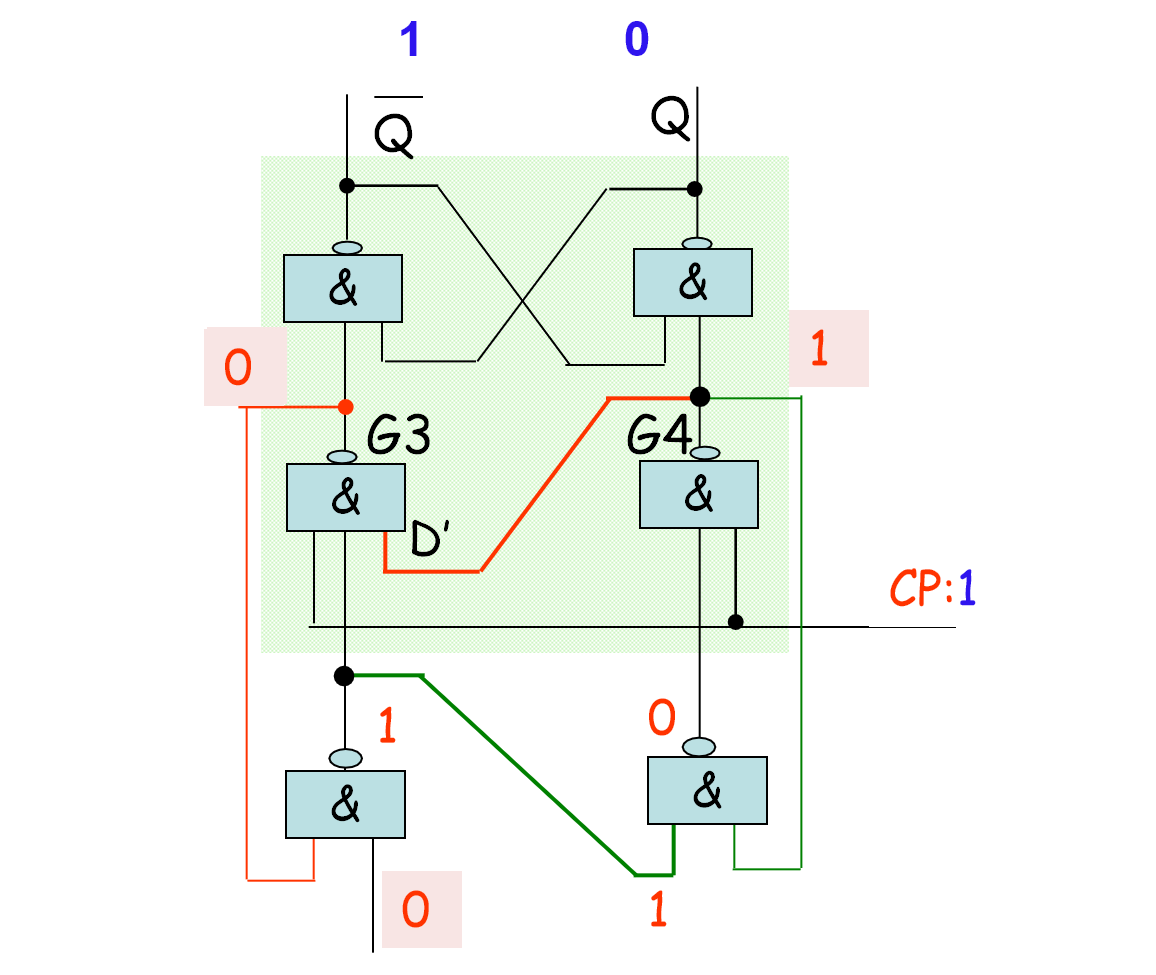

上图是阻塞D触发器.

- cp=0时输出端无变化.

- CP 从0 -> 1 跳变的时刻,将D端的1 置于Q输出端

- CP 从0 -> 1 跳变的时刻,将D端的0 置于Q输出端

分别的图示如下:

最后

以上就是稳重超短裙最近收集整理的关于电位触发,空翻,主从触发器的全部内容,更多相关电位触发内容请搜索靠谱客的其他文章。

发表评论 取消回复