D latch和D 触发器

文章目录

- D latch和D 触发器

- D latch(电平触发)

- D触发器(边缘触发)

- 建立时间保持时间分析

D latch(电平触发)

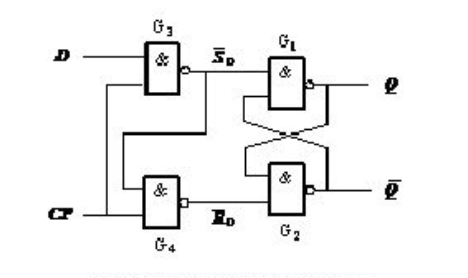

如下图所示,用四个与非门搭建一个经典的锁存器电路。G1,G2形成双稳态电路;G3,G4控制数据输出状态。

在CP=1时,G3,G4相当于非门的功能,处于透明的状态,将输入进行输出。

在CP=0时,G3,G4相当于恒输出1,相当于关闭外界输入,此时处于不透明状态,将数据进行锁存。

D触发器(边缘触发)

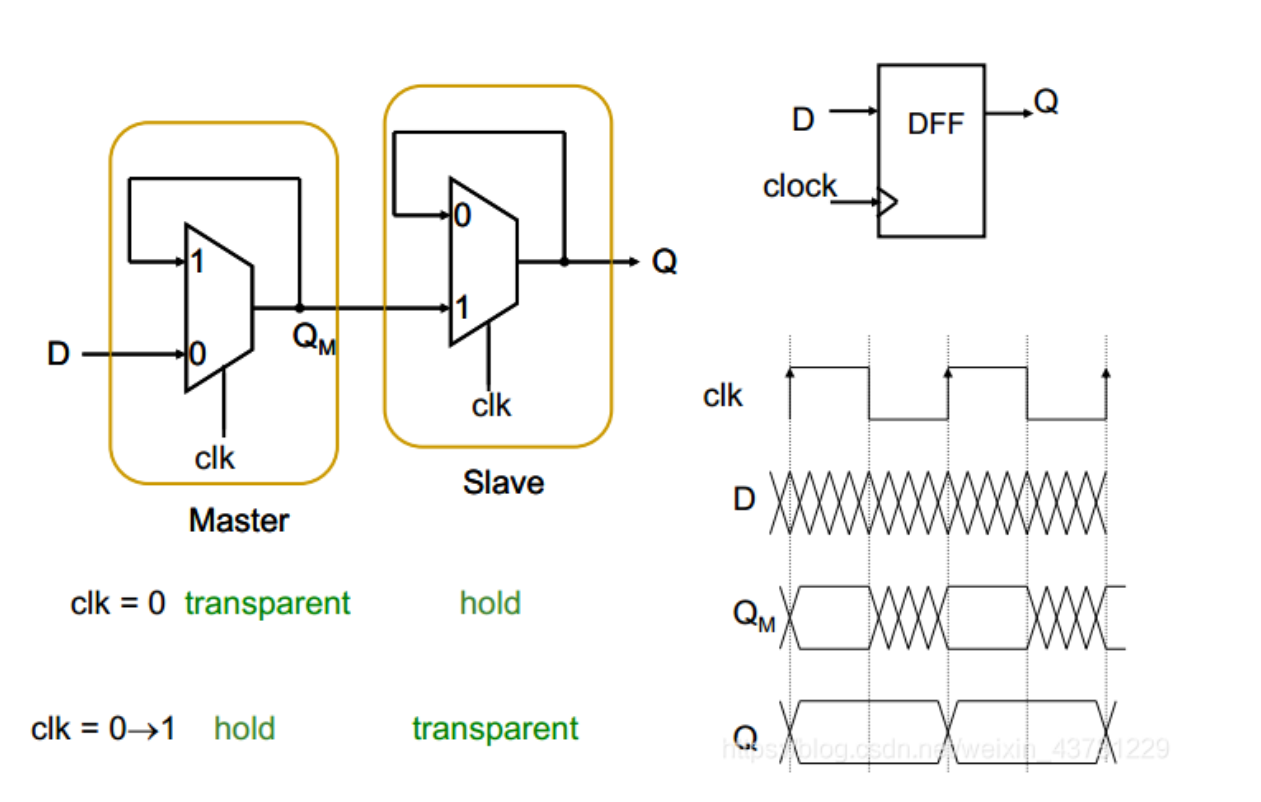

下面是一个典型的主从(master-slave)D触发器,由两个Dlatch组成,第一个称为主latch,第二个称为从latch,主从latch的有效电平不同,下图的主latch时高电平锁存,低电平透明,相反的从latch高电平透明,低电平锁存。

具体电路可以通过传输门进行实现,也可以使用上面的Dlatch构成。

建立时间保持时间分析

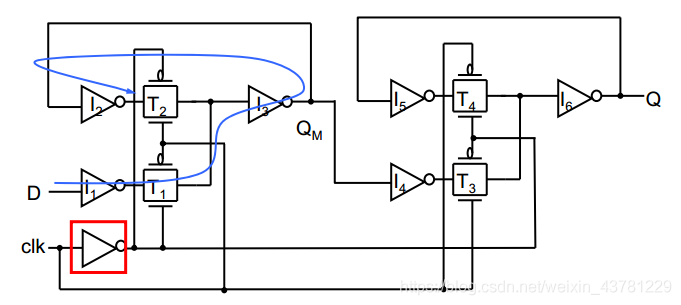

针对建立时间进行分析。T2打开之前,数据需要提前到达T2,也就是经过I1,T1,I3,I2的时间需要满足建立时间要求。即Tsetup = 3Tinv+3Tx。

数据保持时间始终满足。

最后

以上就是碧蓝发箍最近收集整理的关于D latch和D 触发器的全部内容,更多相关D内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复