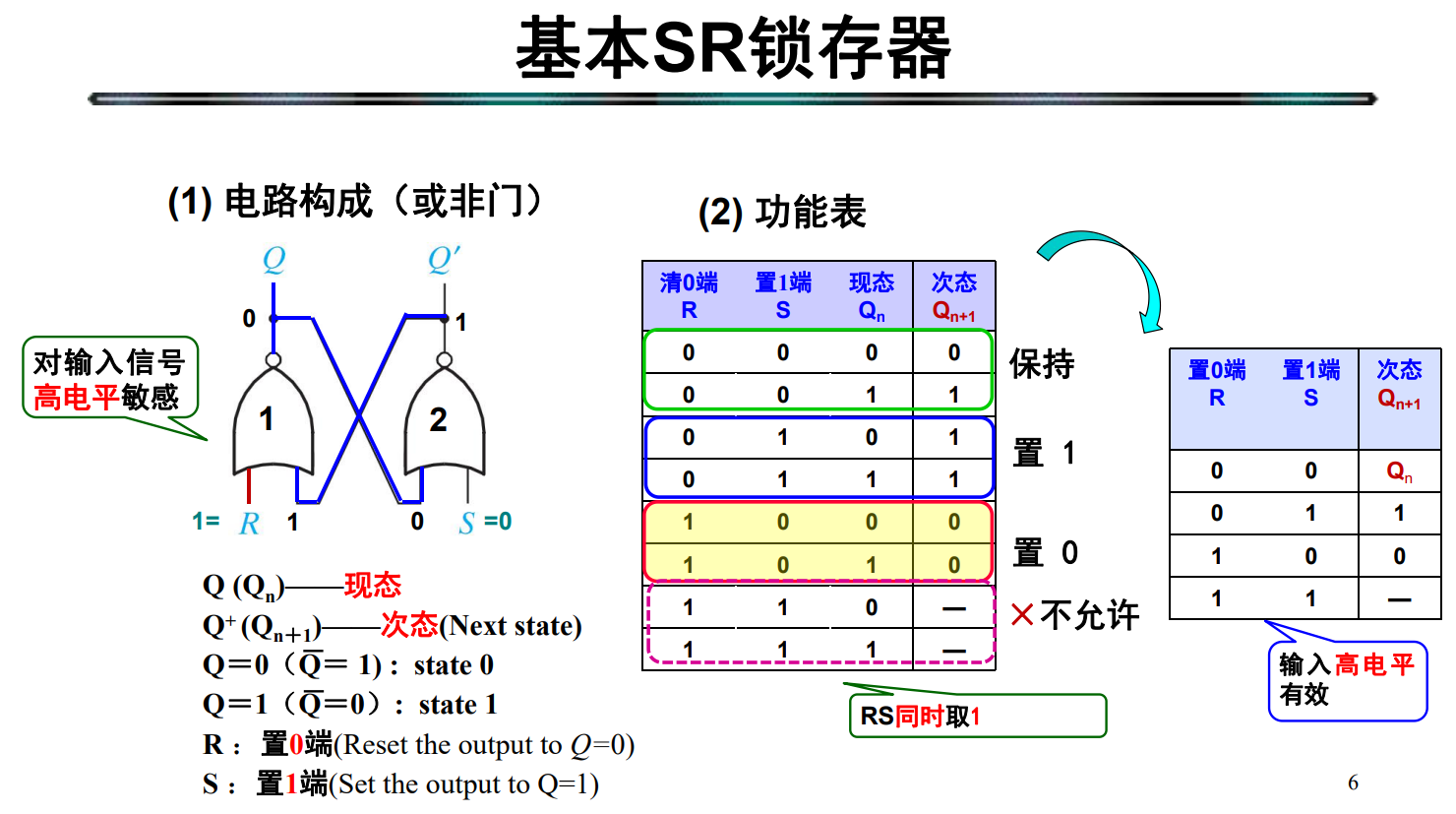

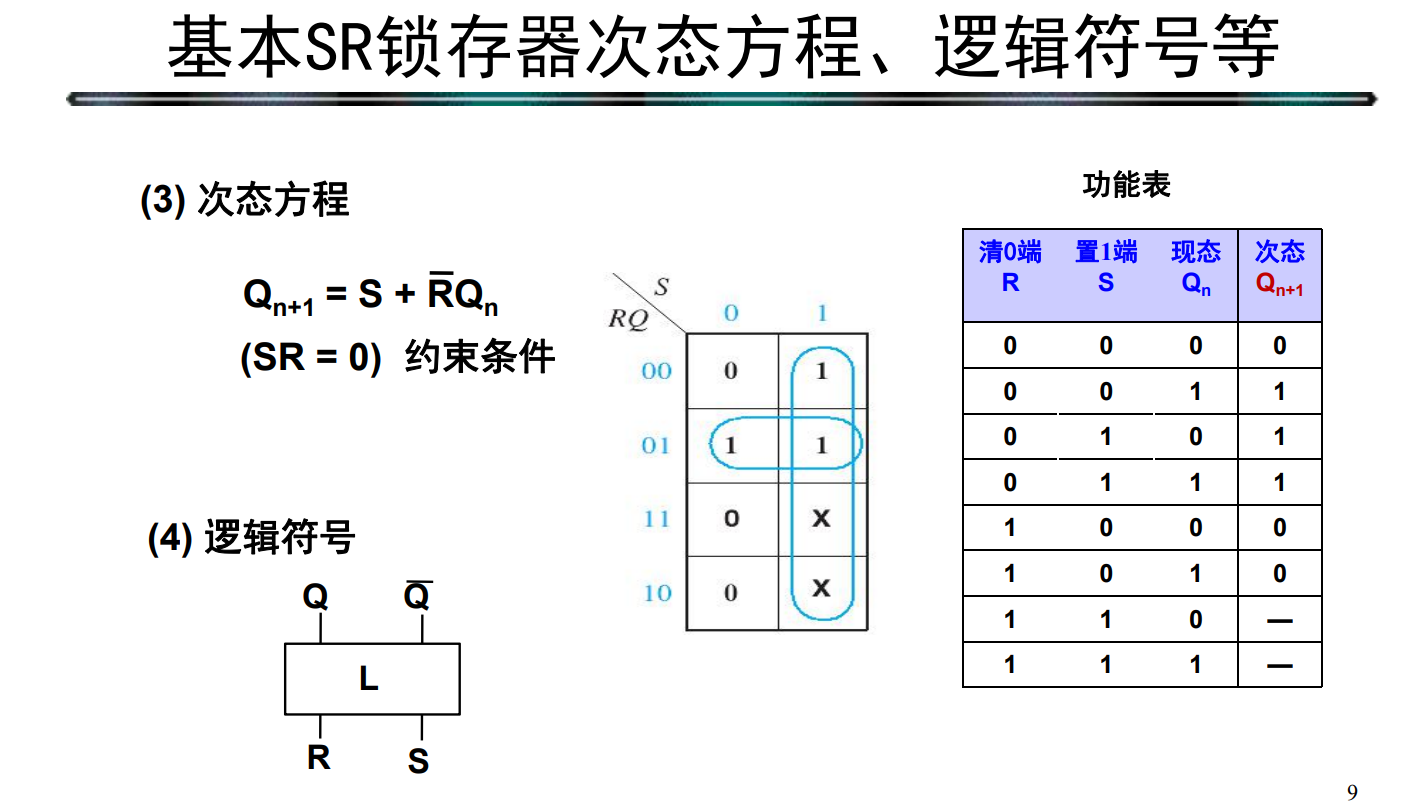

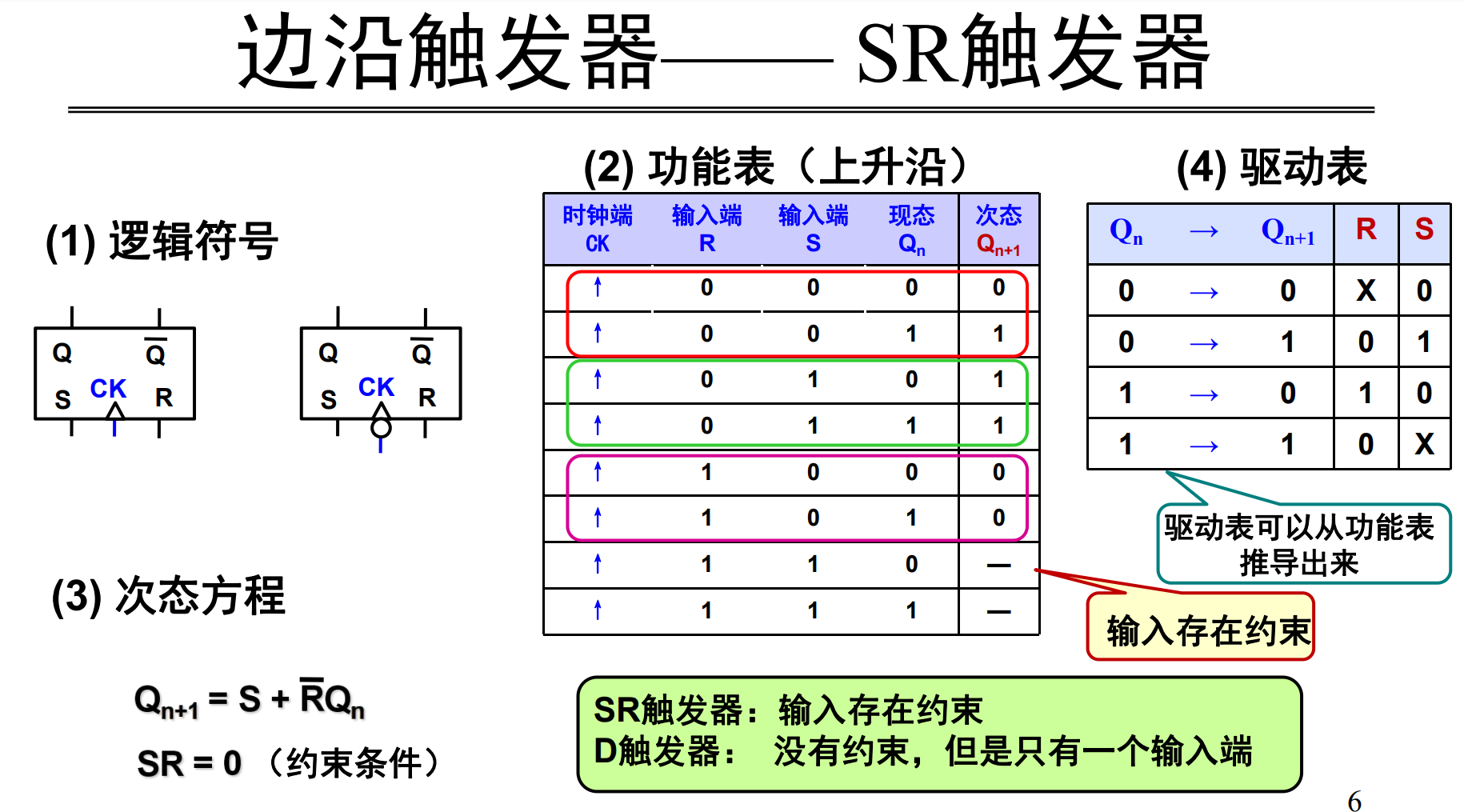

记住:JK触发器J置一,K置0;SR触发器也是S置一,R置0,只是一开始ppt的图R在左边。具体是要看字母的。

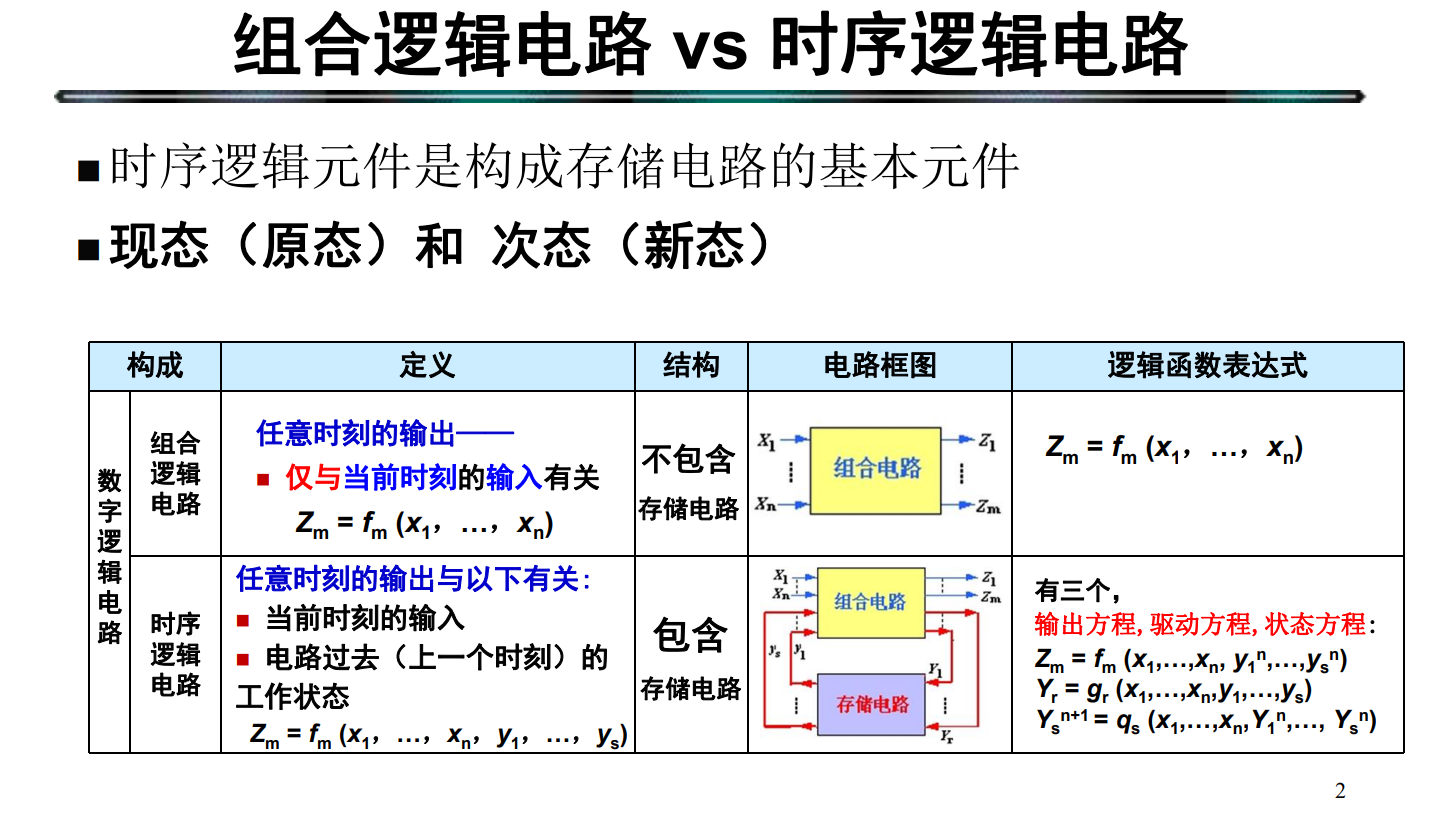

可见,关键的区别在于有没有储存器。

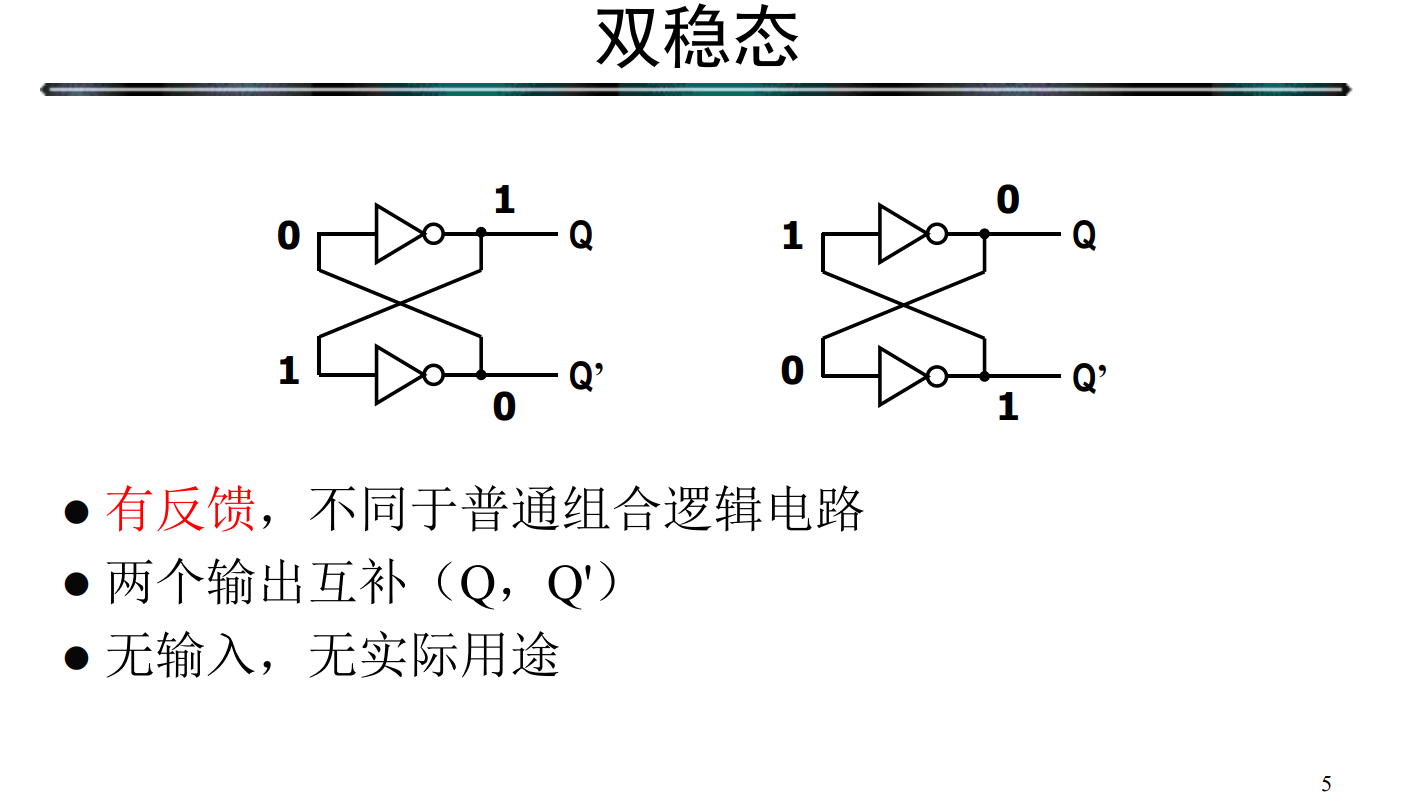

这是怎么做到的呢?:

R置0,S置1.状态看Q端,不是Q'

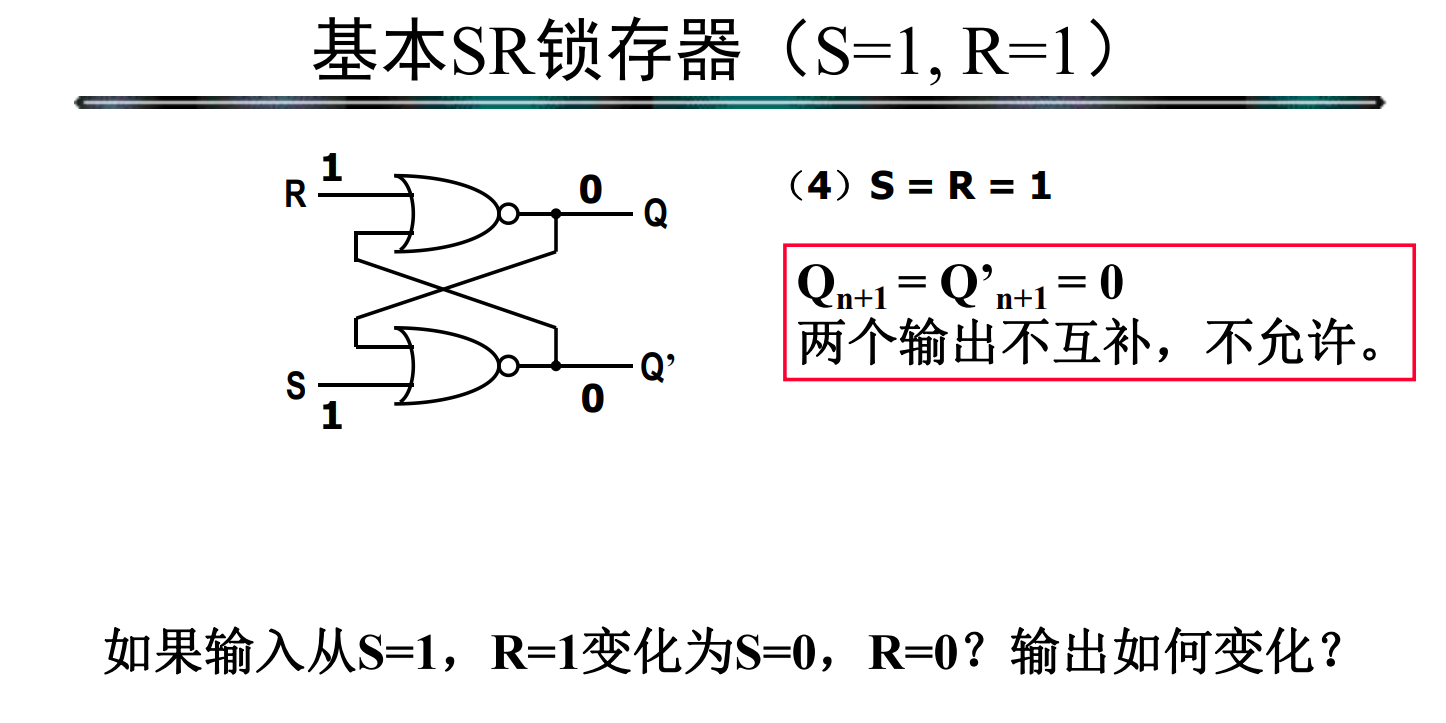

你可能会想:如果RS都是1怎么办?:

当然这种一般是不予许的。

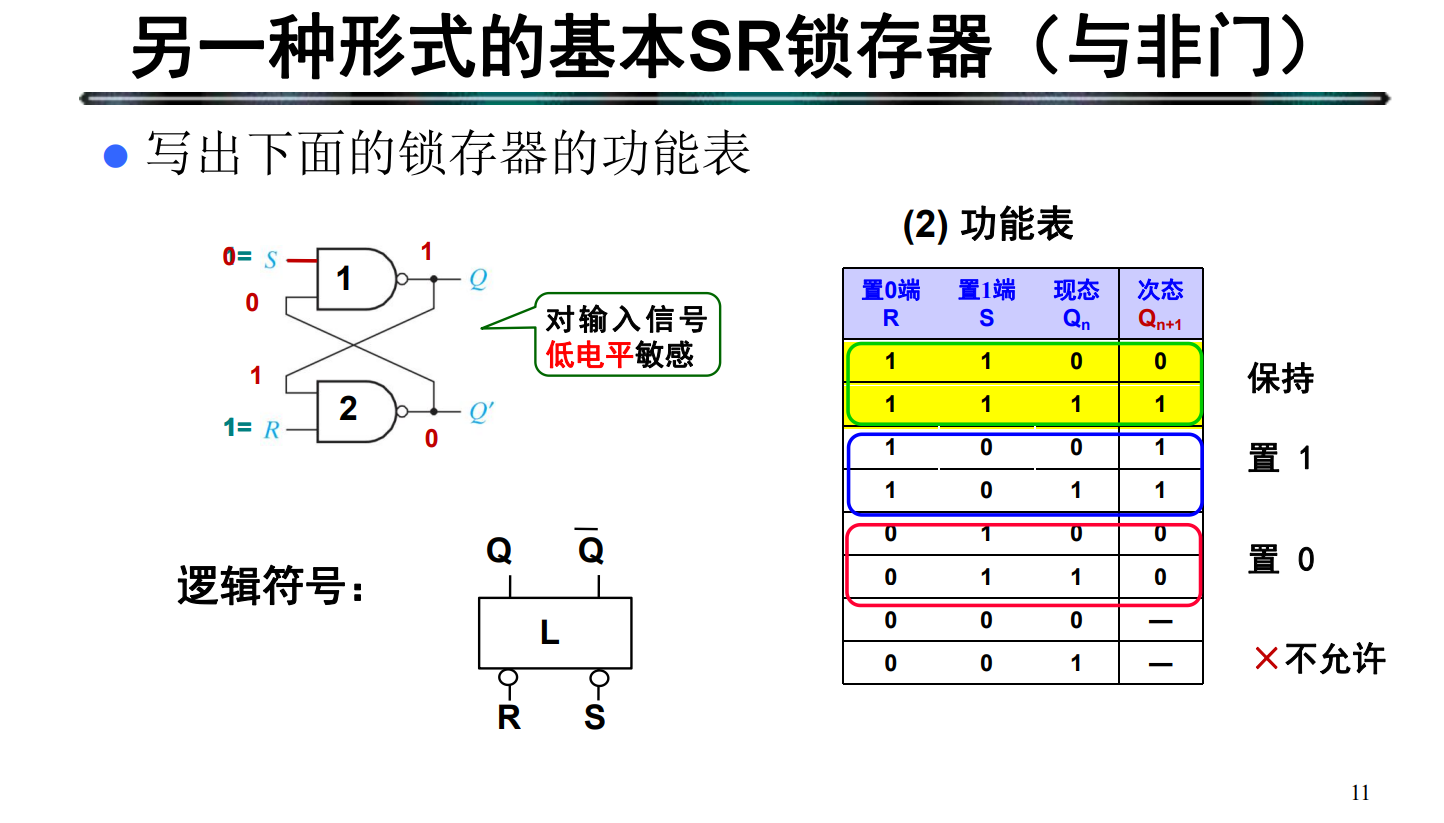

当然,这个地方一直是高电平有效,会不会浪费电?我来个低电平有效的:

R依旧是置0端,S依旧是置1端,不过现在是0作为改变的信号了。从逻辑符号看,就好像是从头到尾就只有输入翻了一下,其他的都没有变。

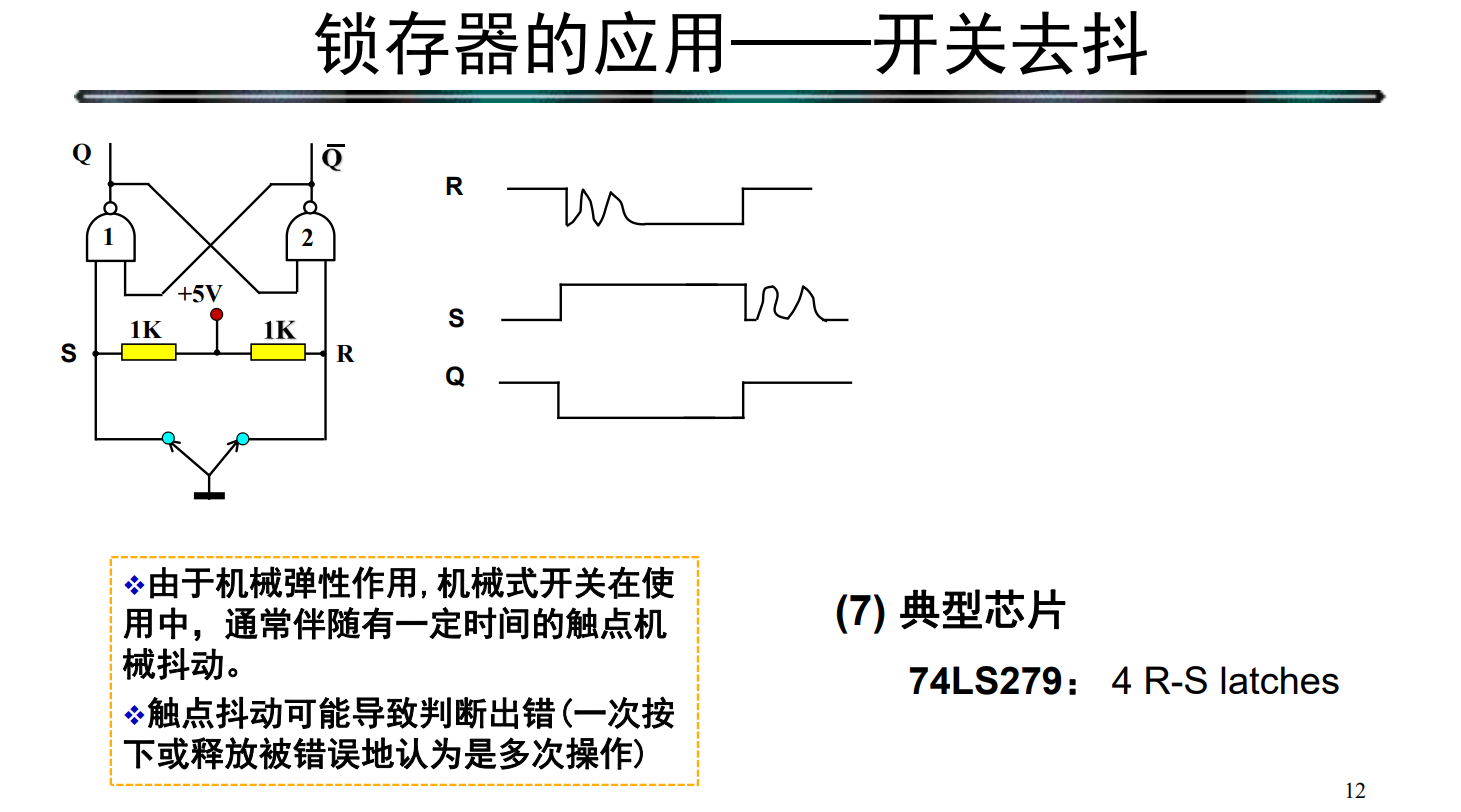

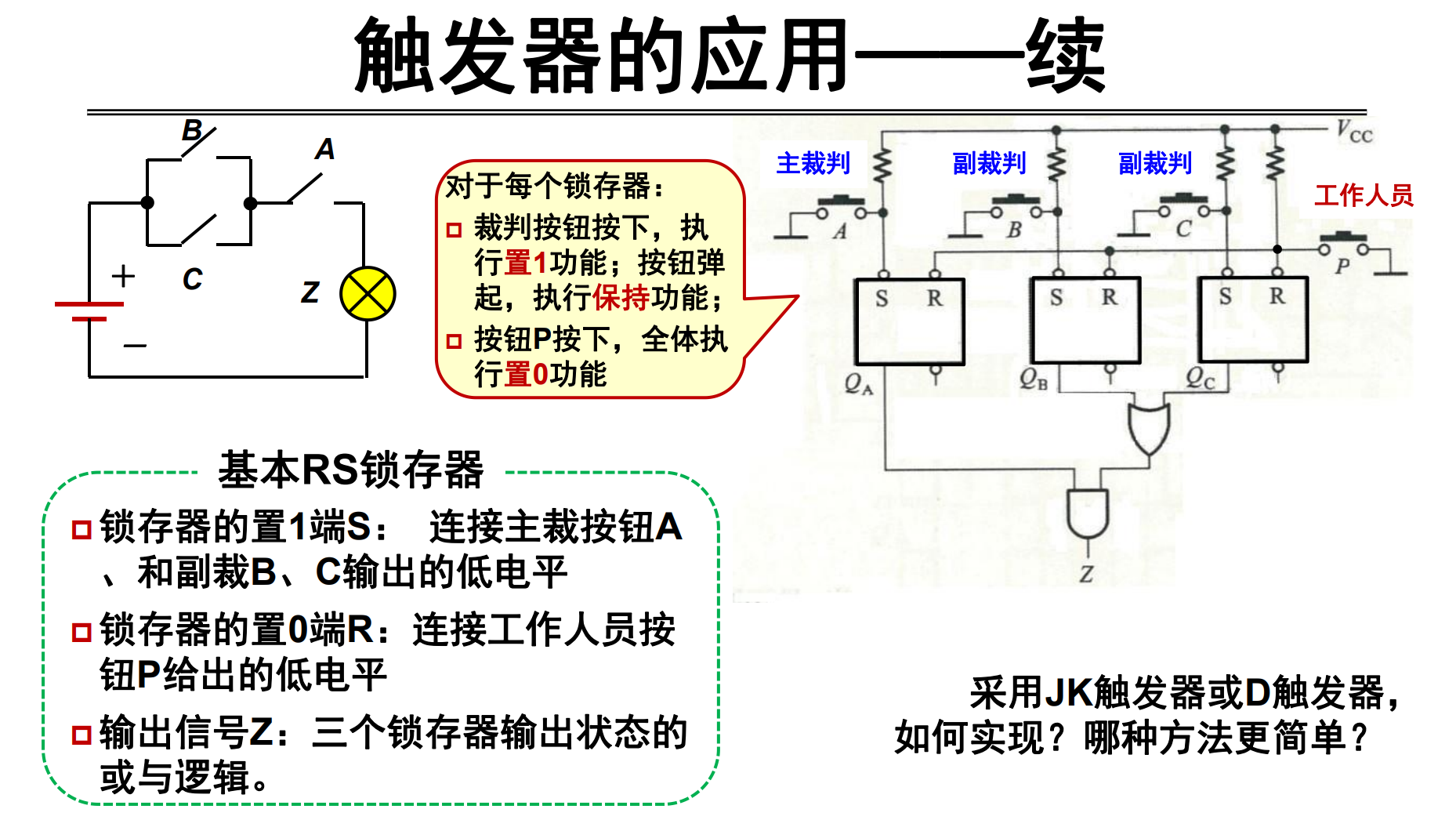

锁存器可以干嘛呢?:

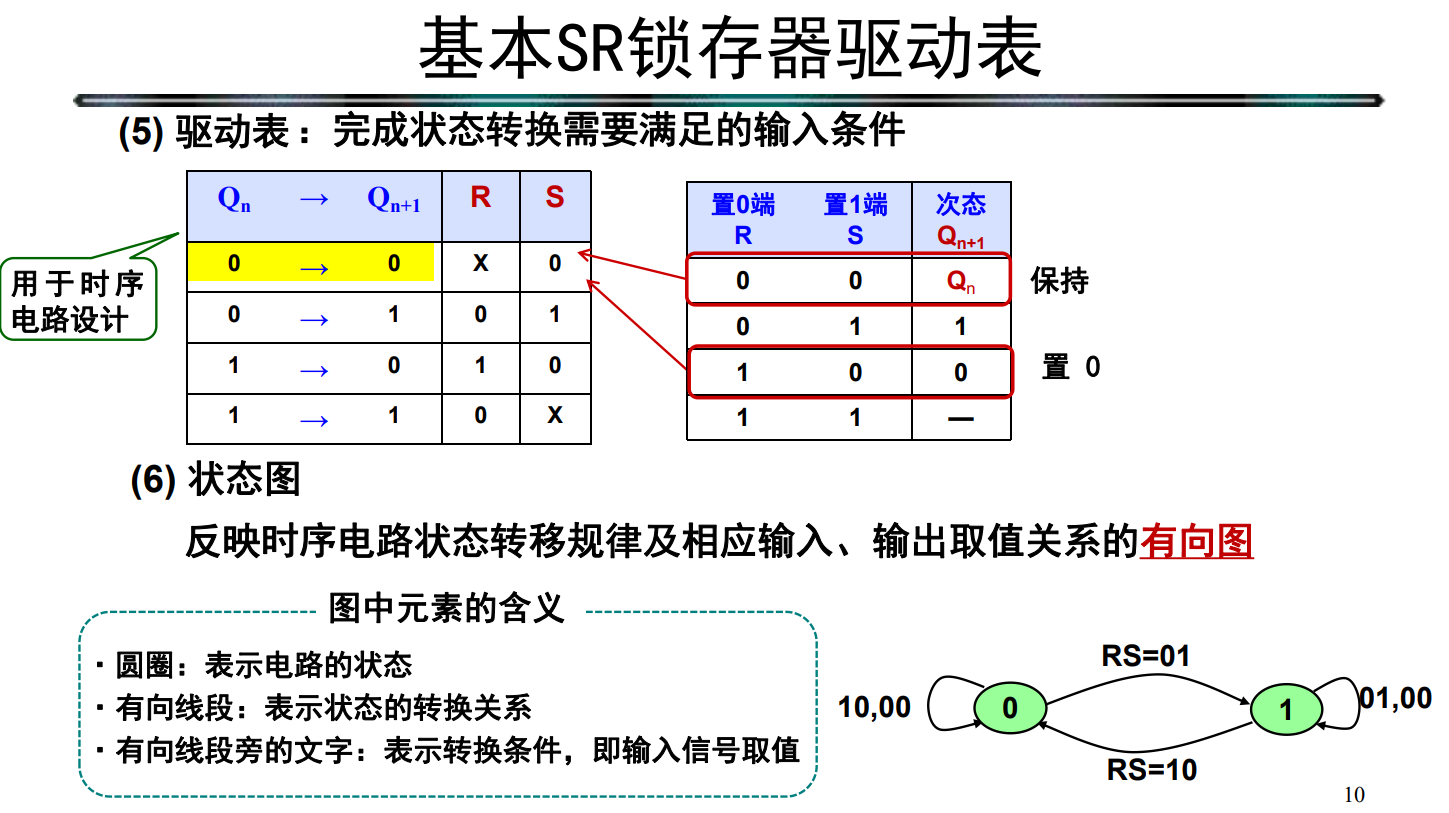

用了锁存器就没有这个烦恼了。我即使按了多次R,最后也只是置一次0.

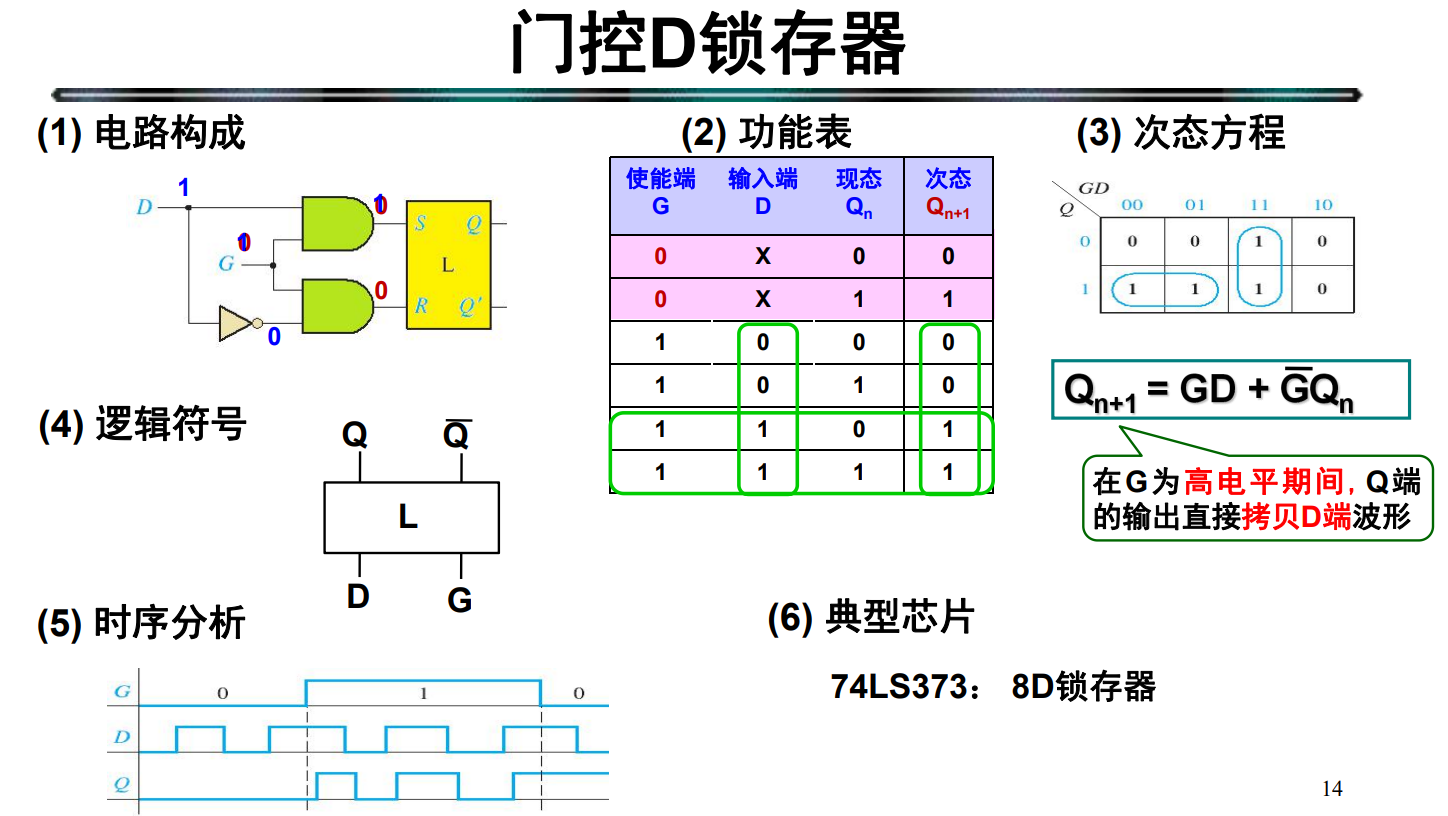

还有一种锁存器:

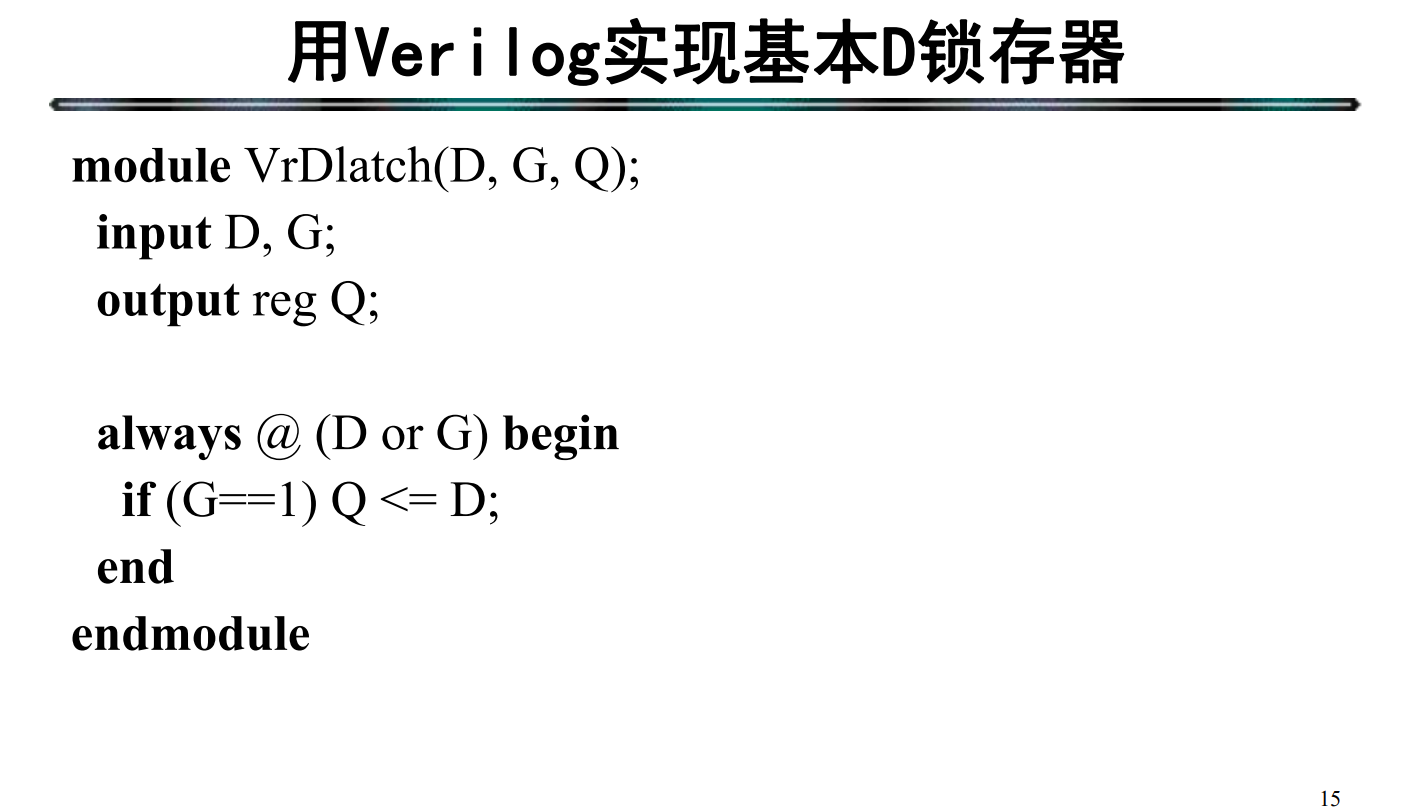

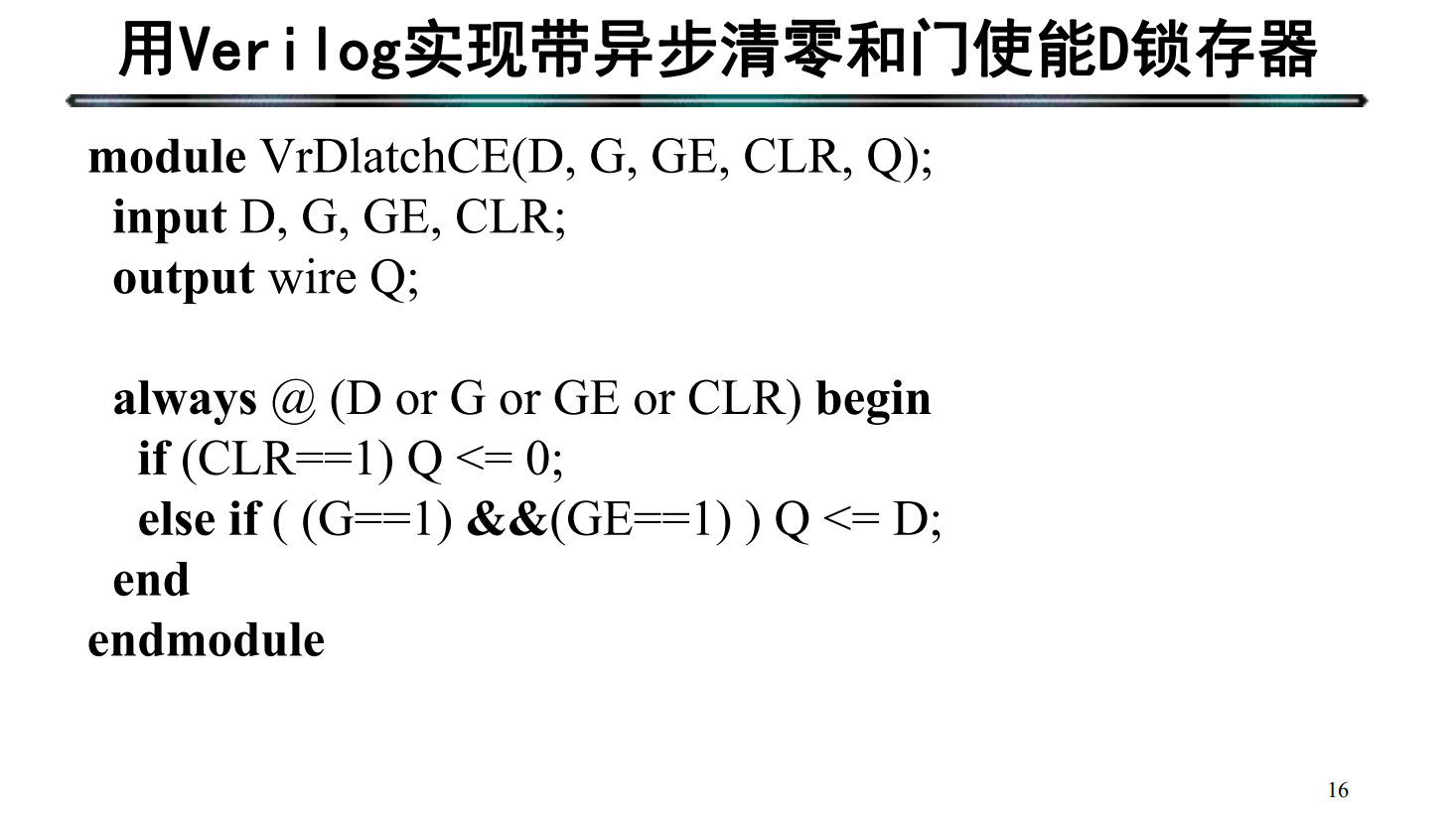

可以看到,这个电路就是最后部分就是锁存器,开头的部分用D来控制S是1还是R是1.D是1时S是1,置1.D是0时R是1,置0.这样我们就可以使用一个按钮控制R S了。(可以看到,G=0相当于原版的00,G=1后就是一个简单开关,后面会用这种器件)

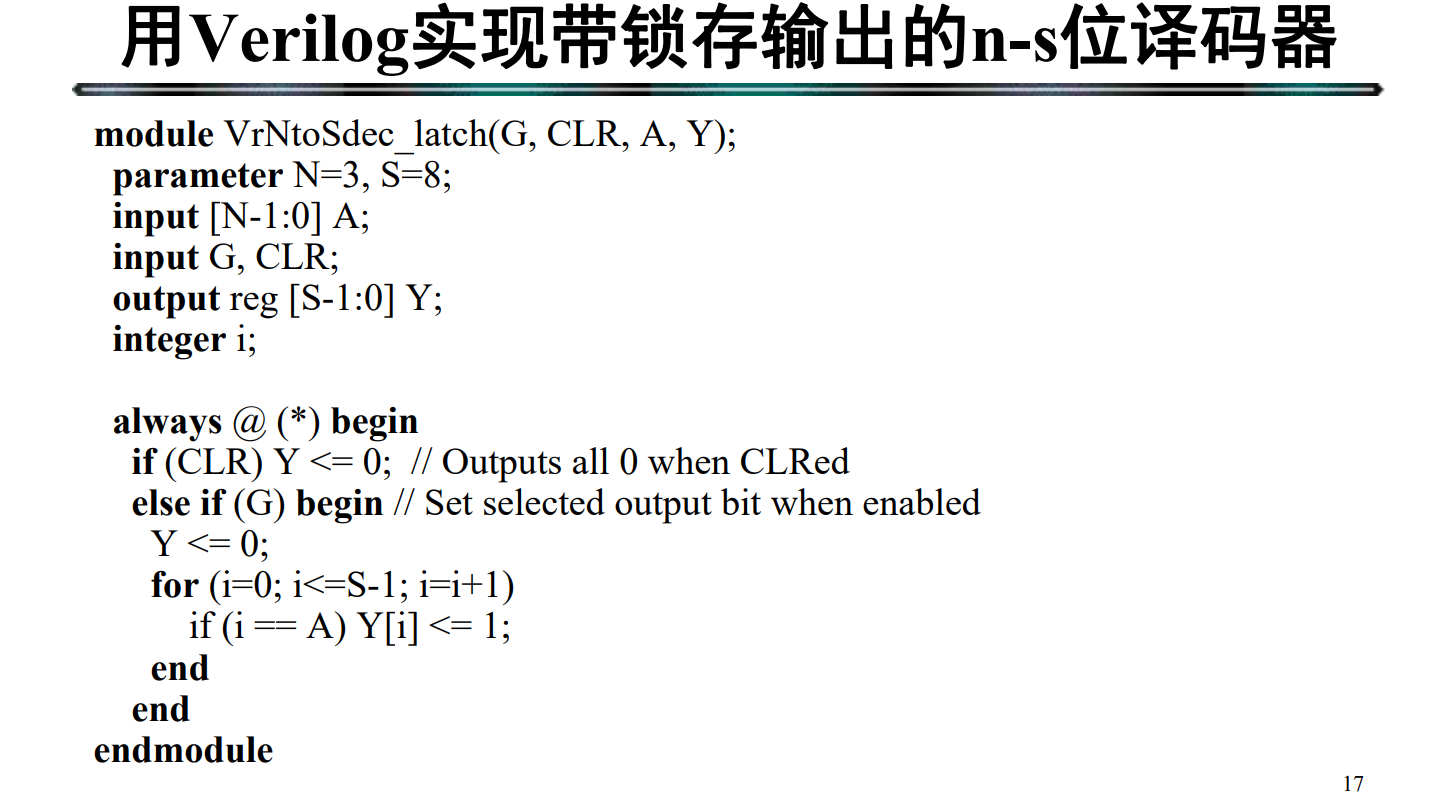

和别的没大区别,就是输出变成了锁存器。

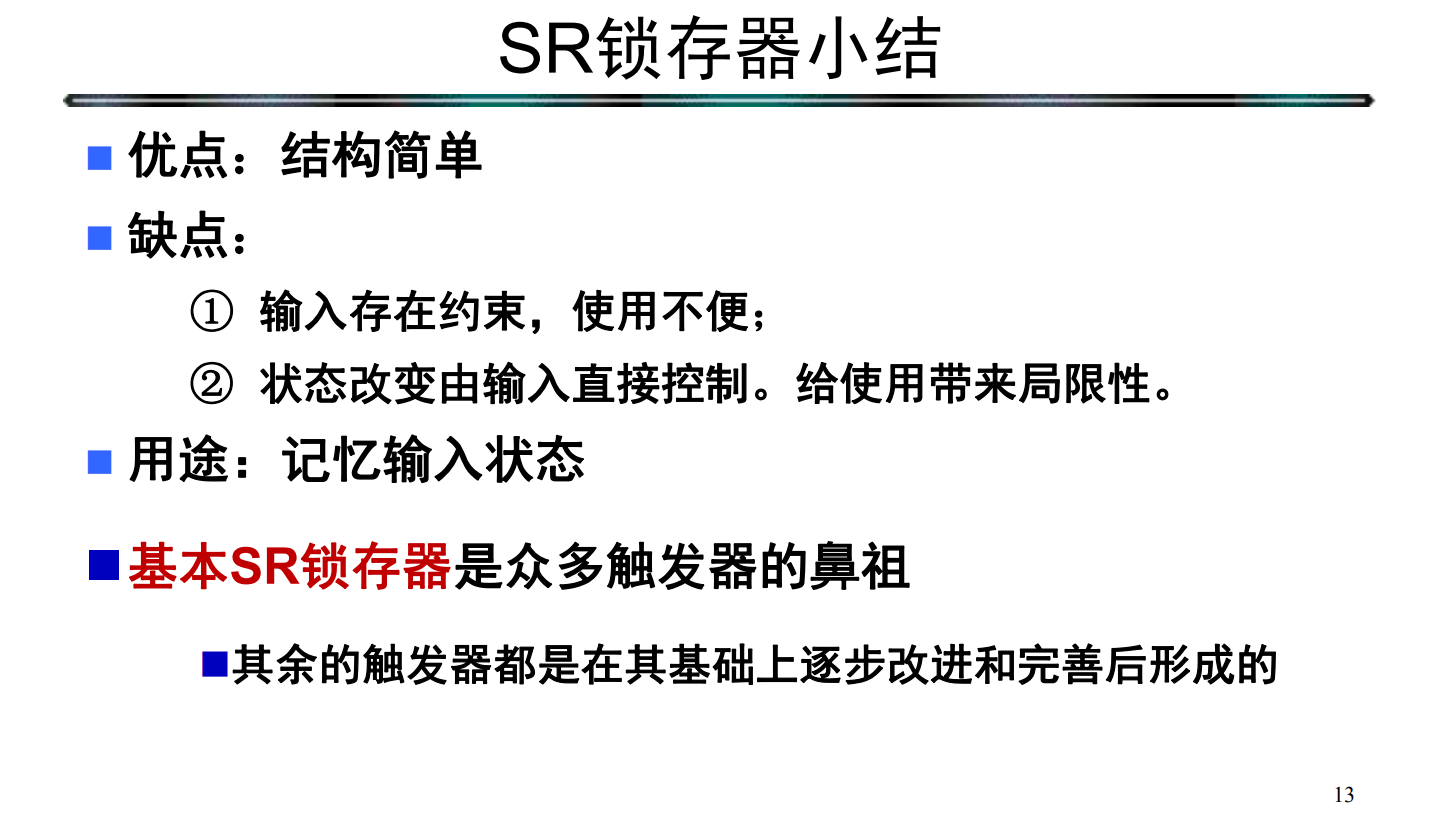

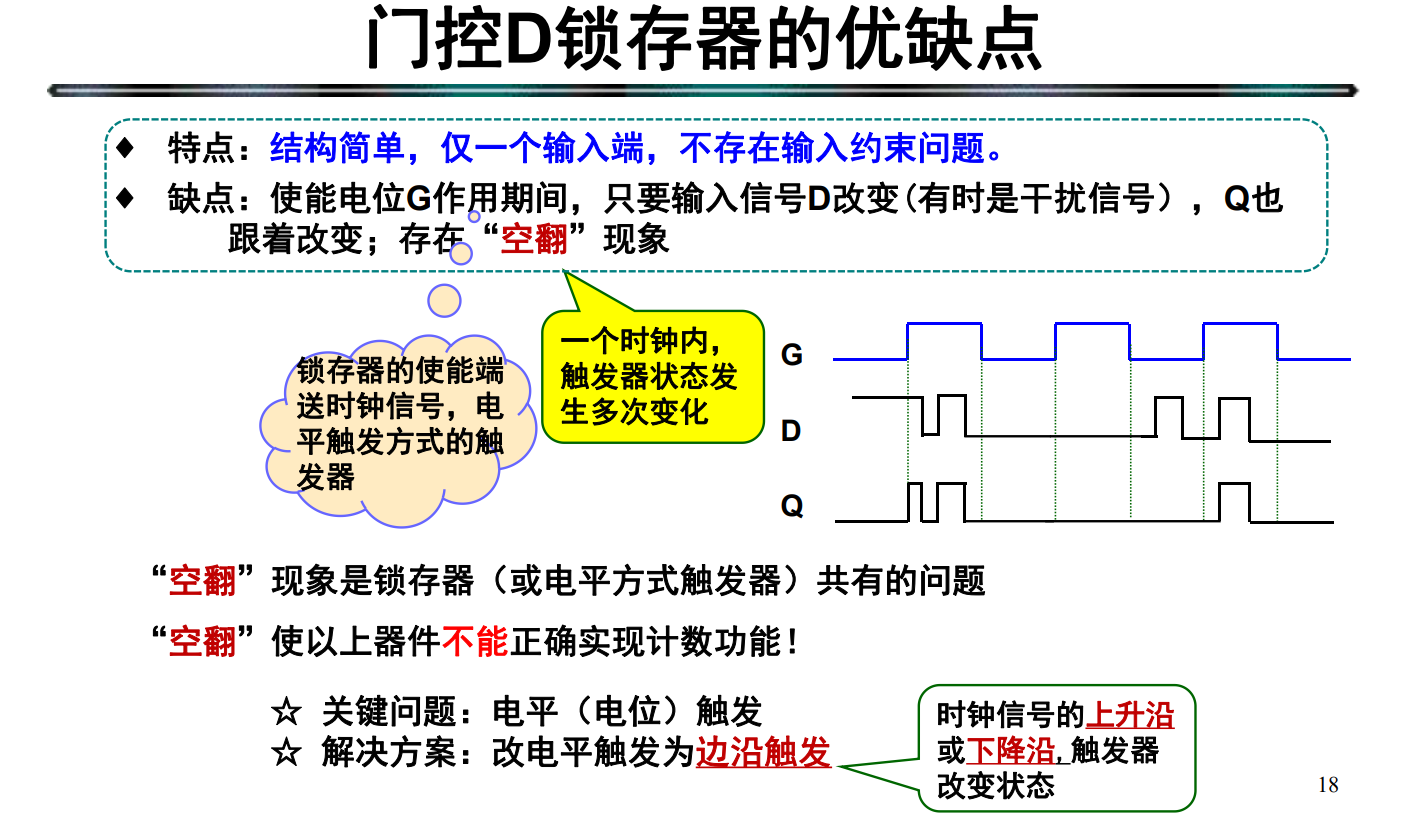

这种东西有什么优缺点呢?;

既然这样,我就要使用时钟信号啦。时序电路登场:

触发器主要有这些:

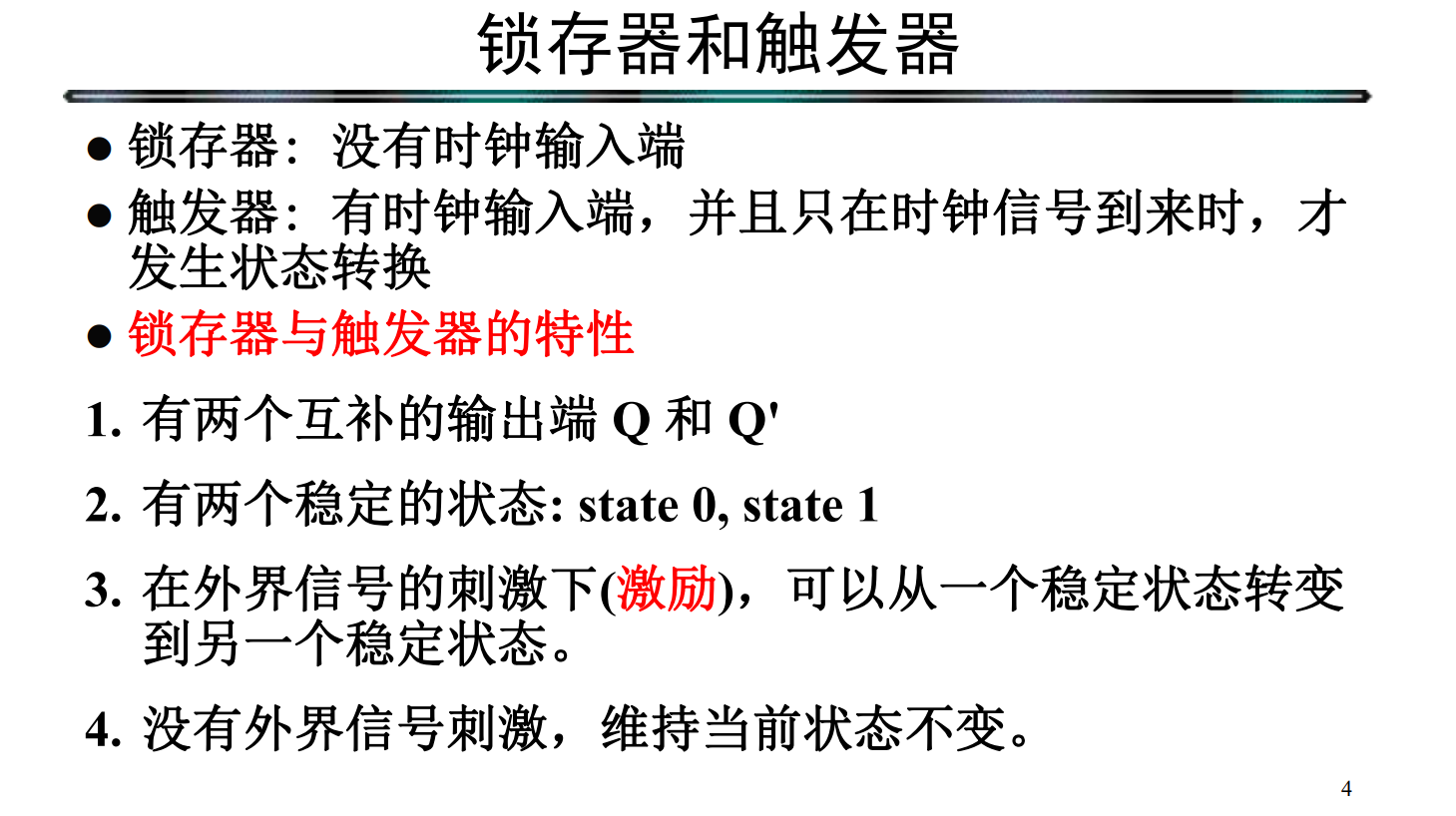

和之前的一个道理,就是有一个时钟输入端罢了。

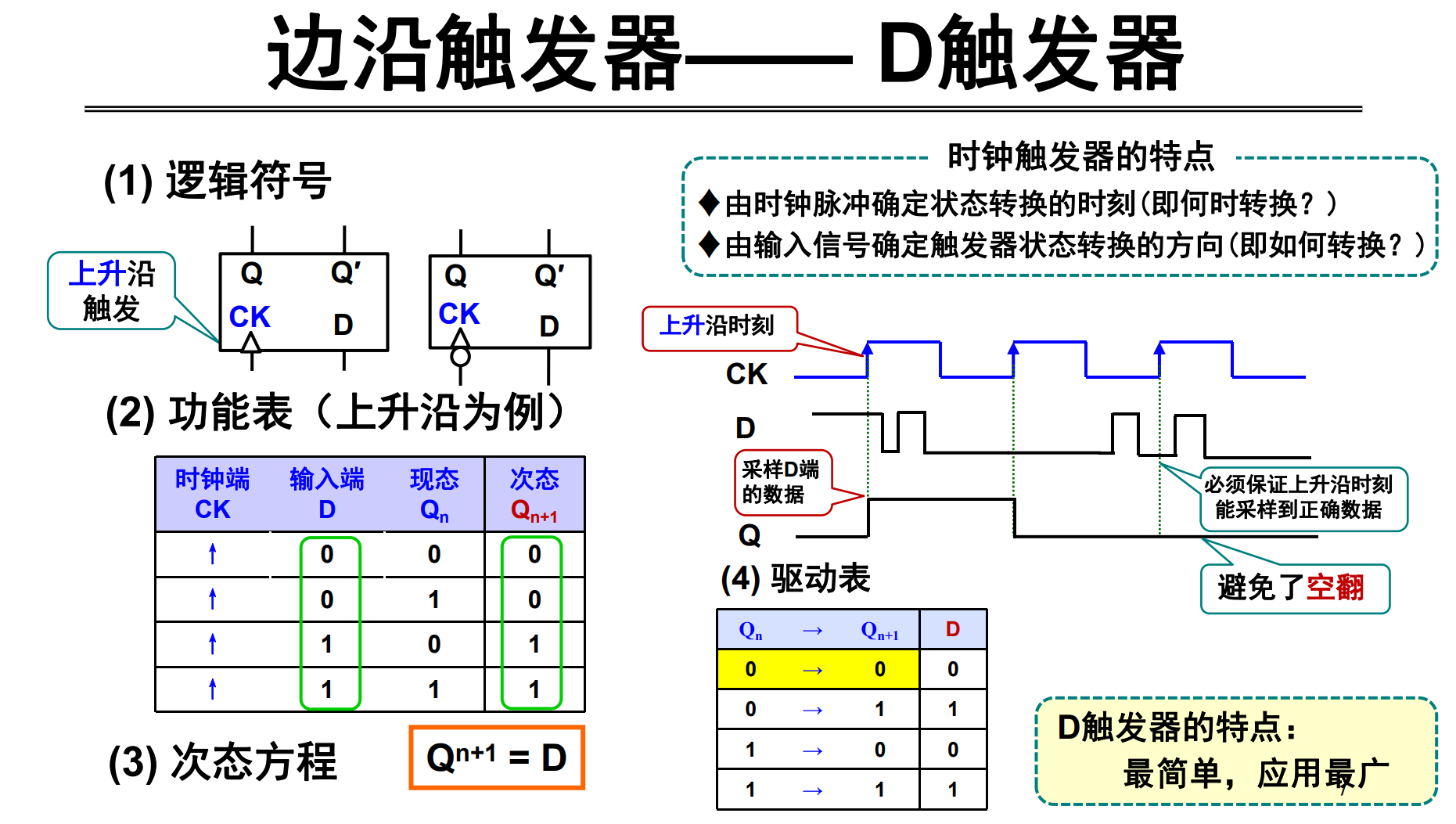

这之前的D锁存器一样,只是加了时钟。

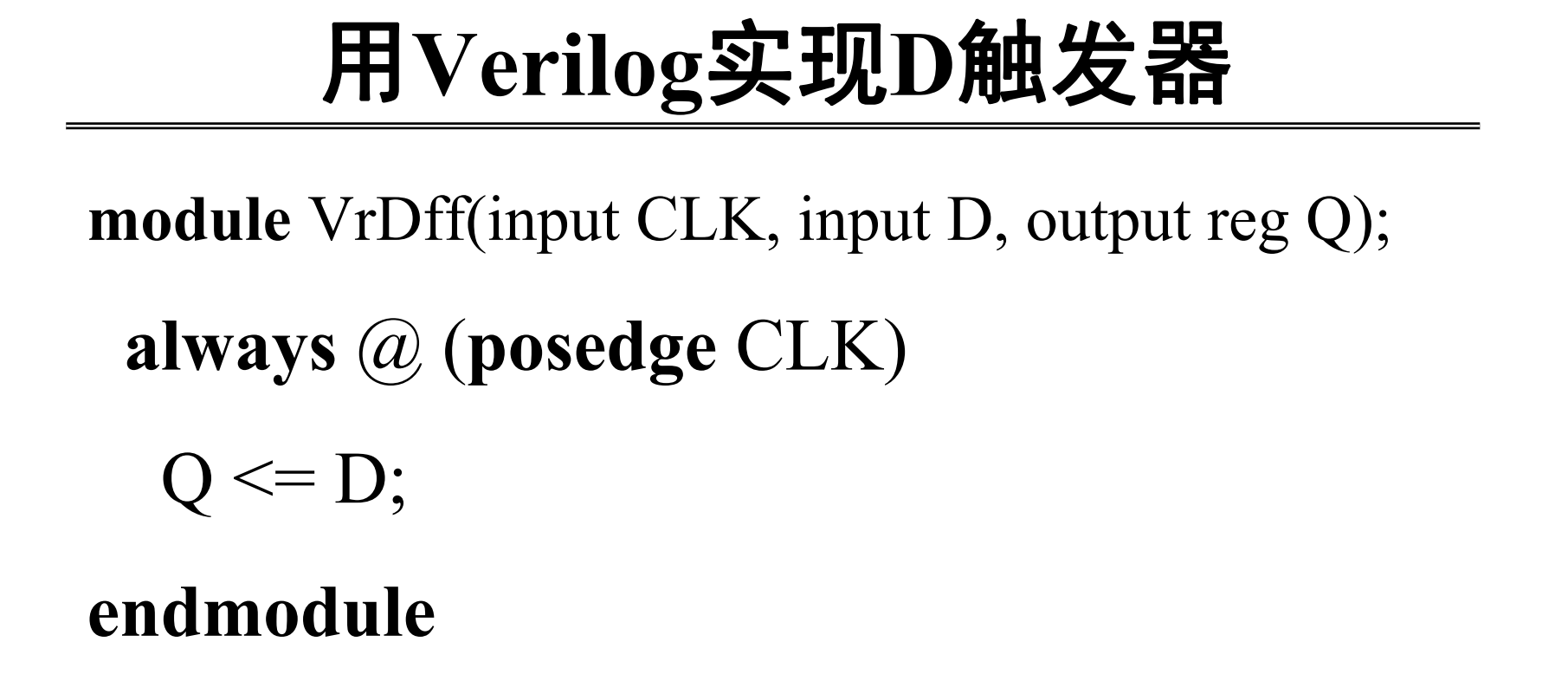

用veilog实现也非常简单,这些器件verilog都是自备的:

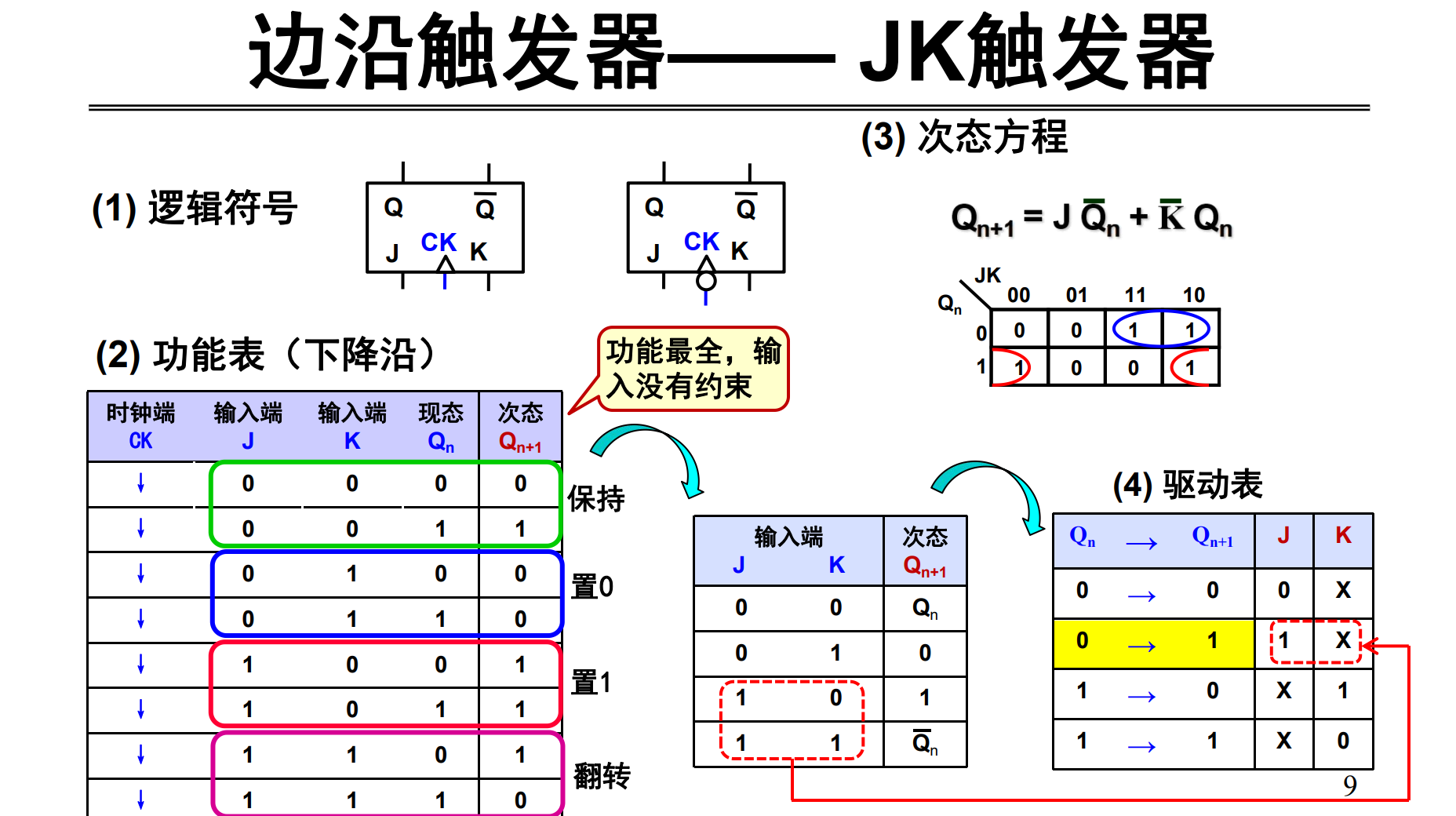

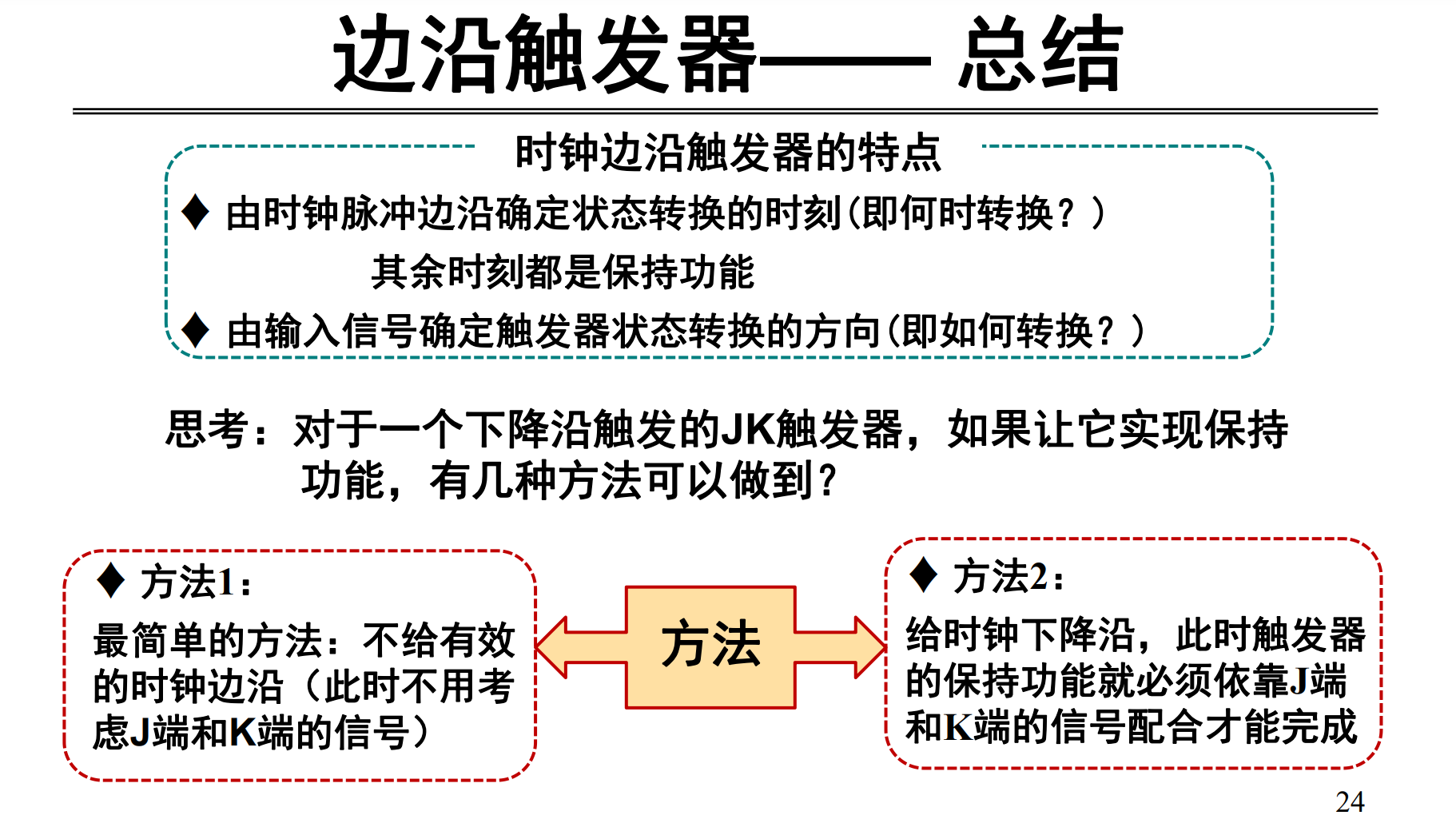

这个触发器有两个特点:一是J是置1端,K是置0端,二是予许同时输入1,会把结果反向。

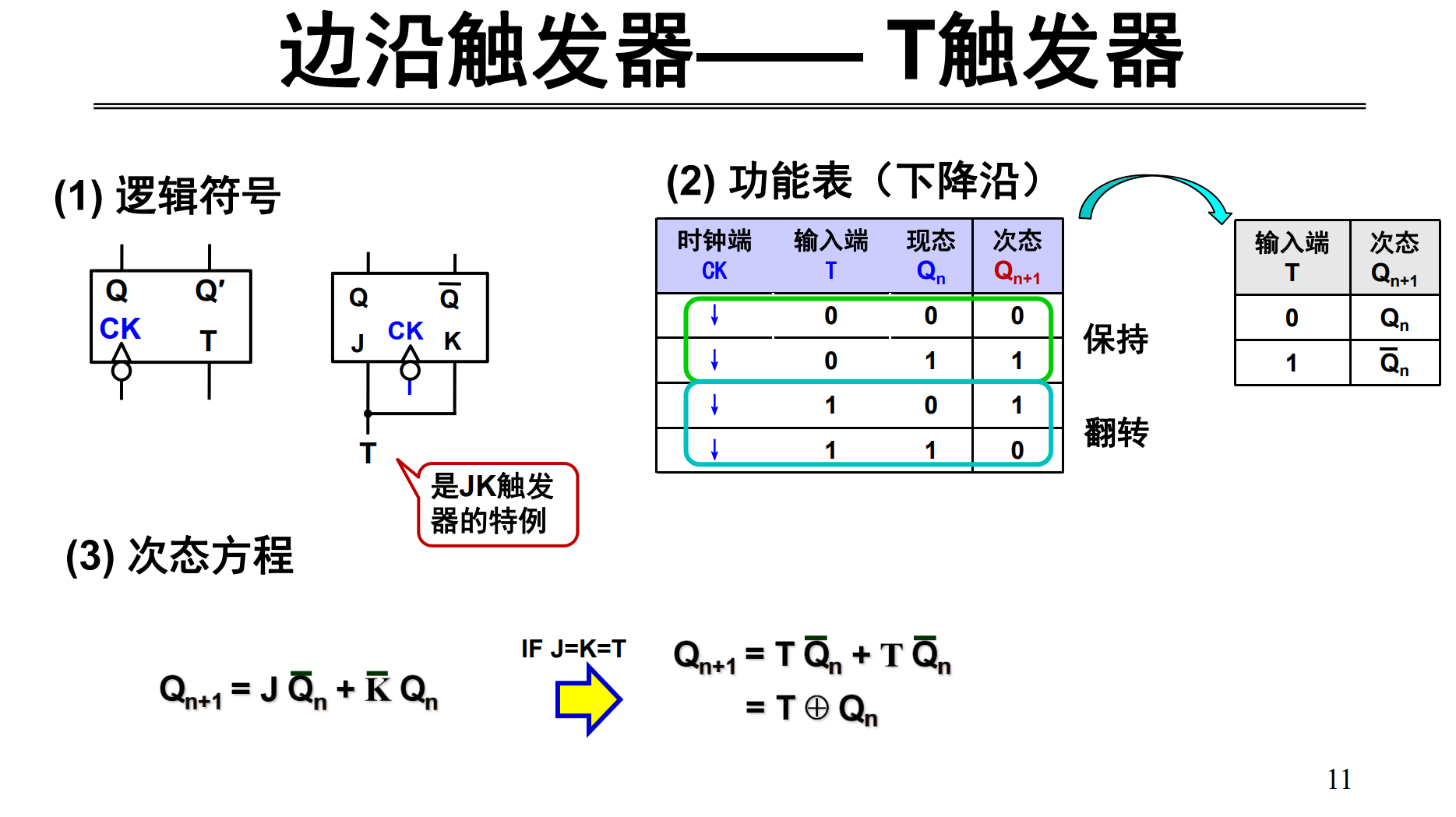

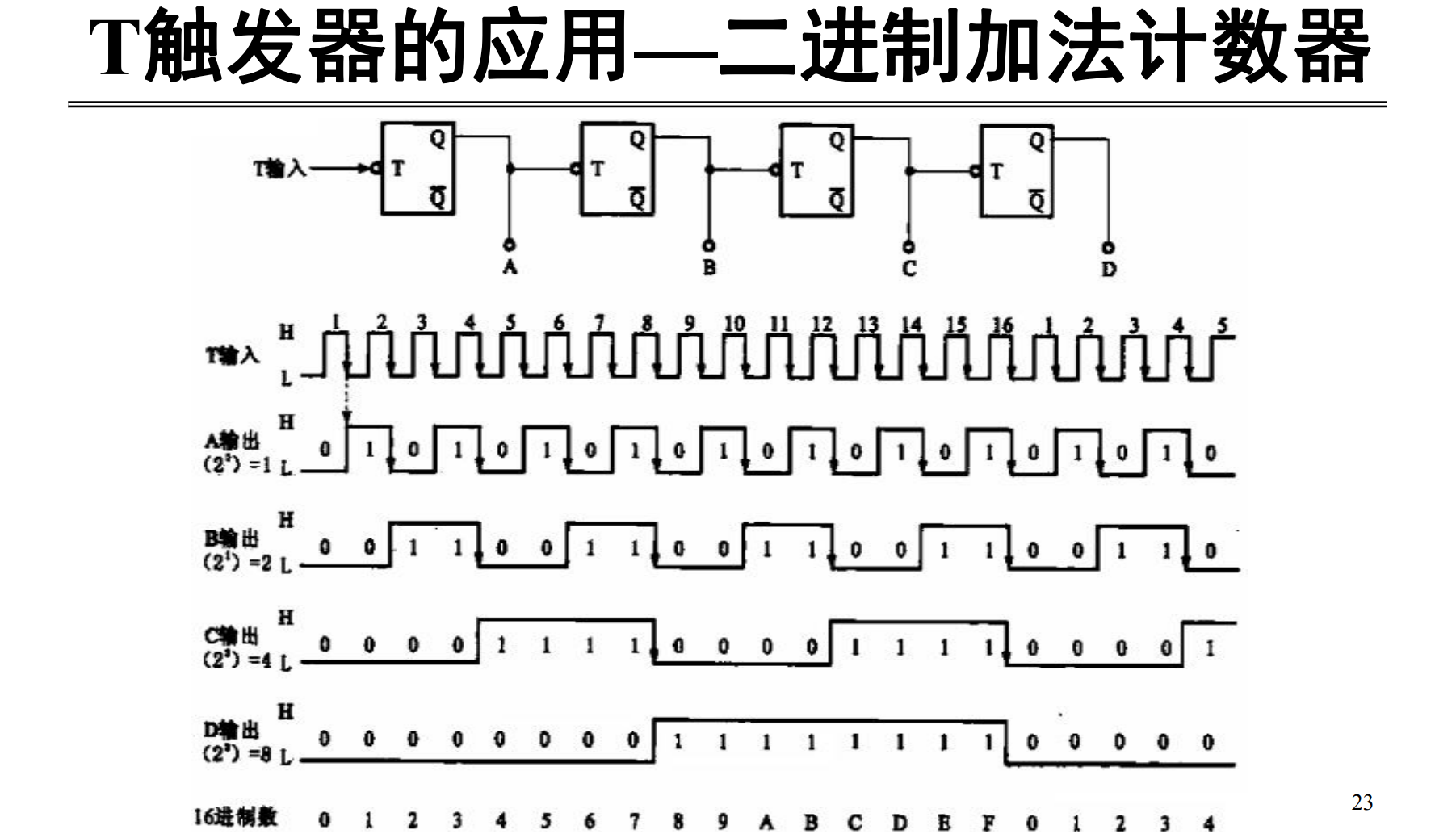

修改版JK,利用JK的性质,只有原样和反转两种情况。

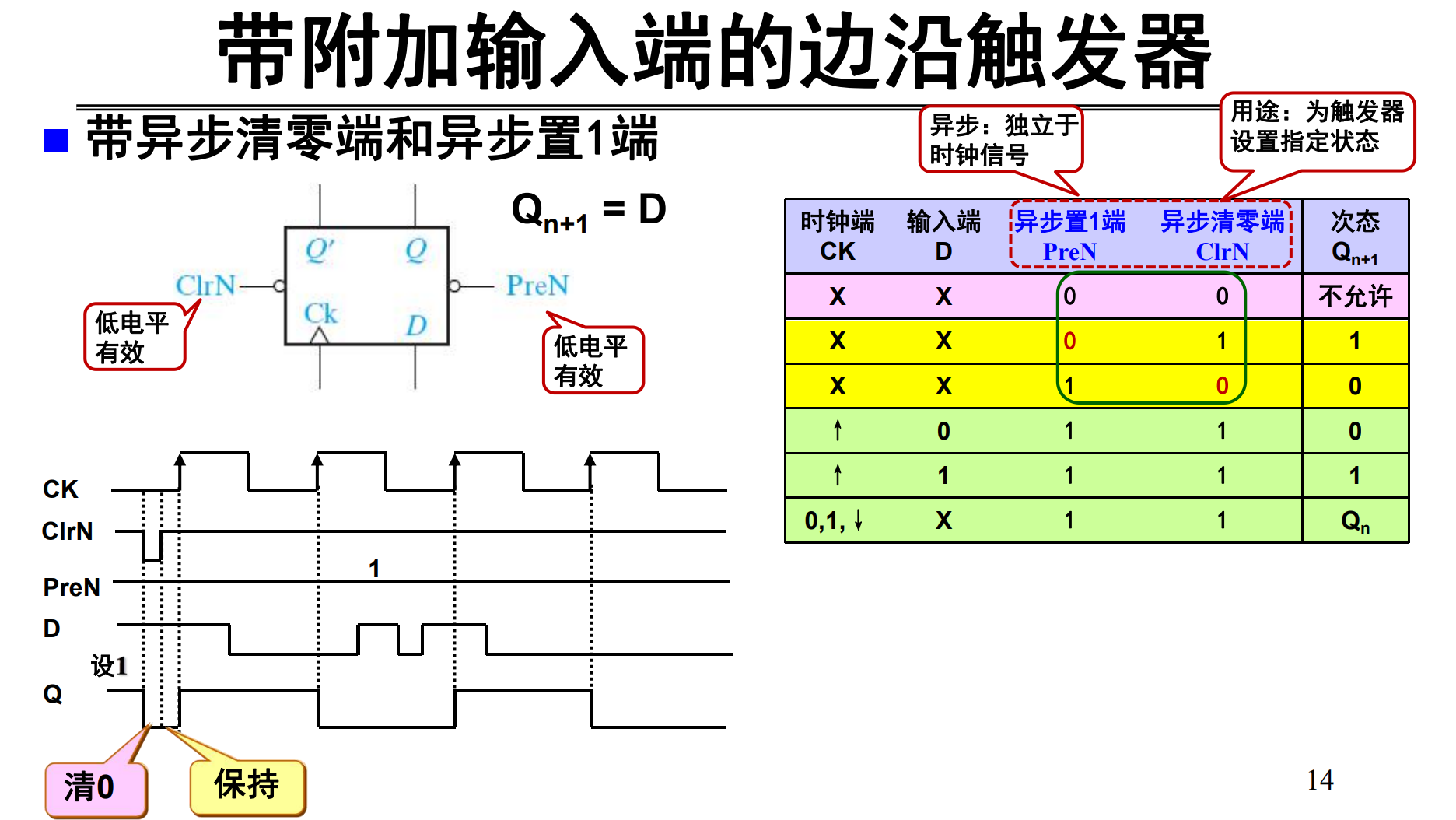

回忆一下D触发器是怎样的:D是多少,就要给改什么。但这里这玩意有了新的输入。可以看到,这个异步置1和异步清0就像是空降的领导,是低电平有效的(看到了那两个非了吗)。两个都是低电平(0),就不可以;置1低电平,那就是1,管你CK和D?清0也是同理,只有两个都无效(都是1)才回到了正常的步伐。

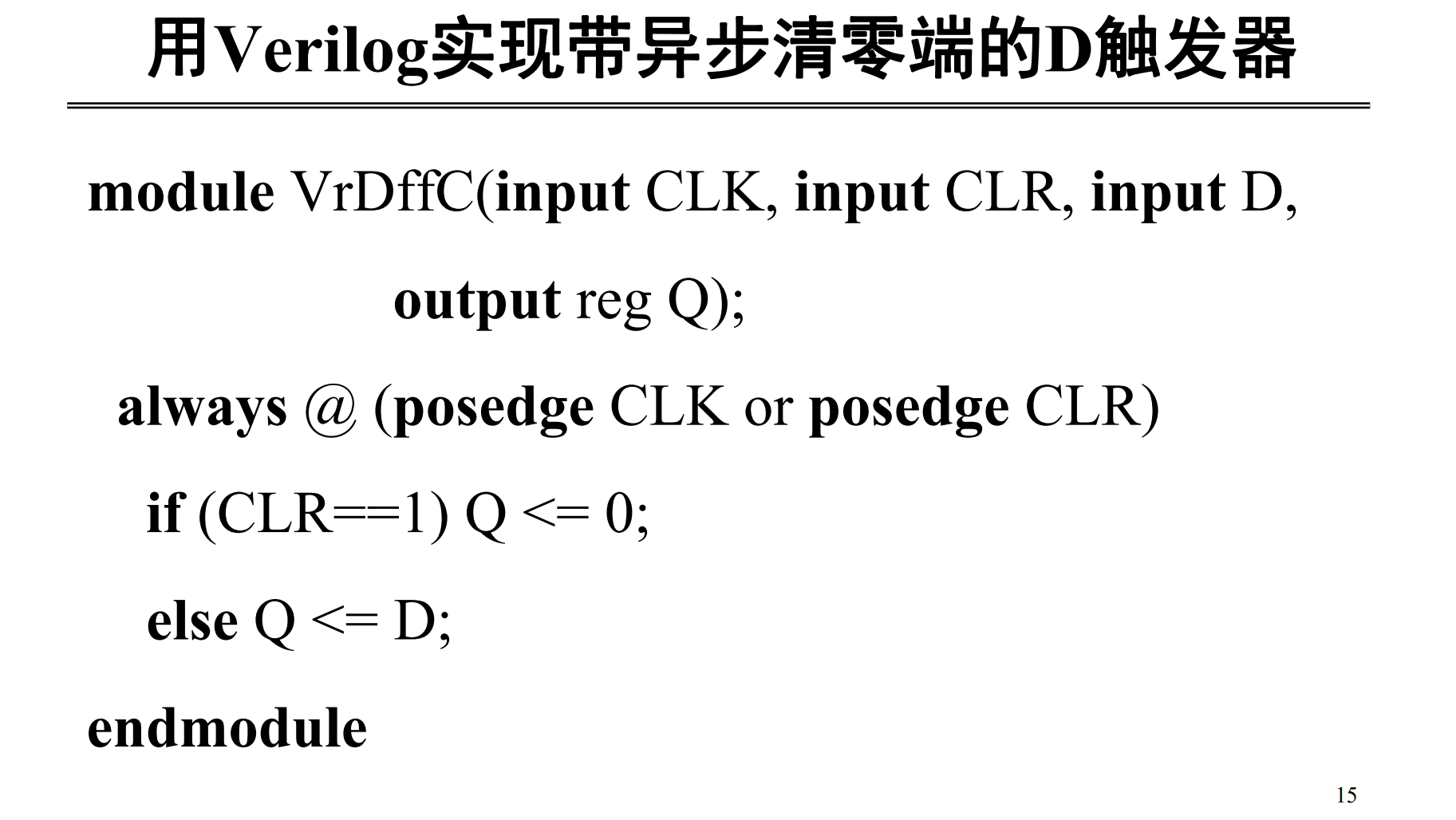

注意,这个只有清0端。而且是高电平有效的。

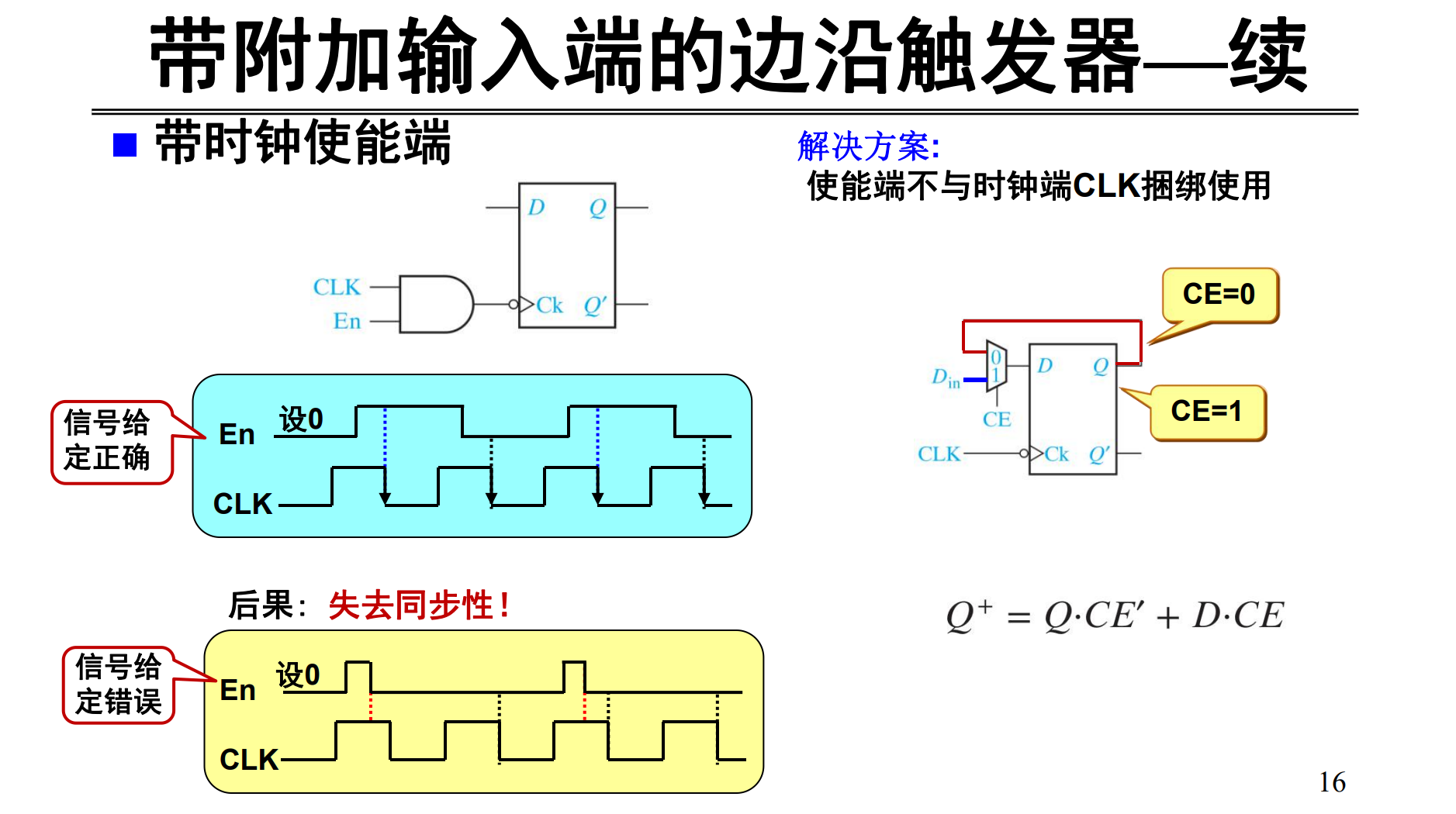

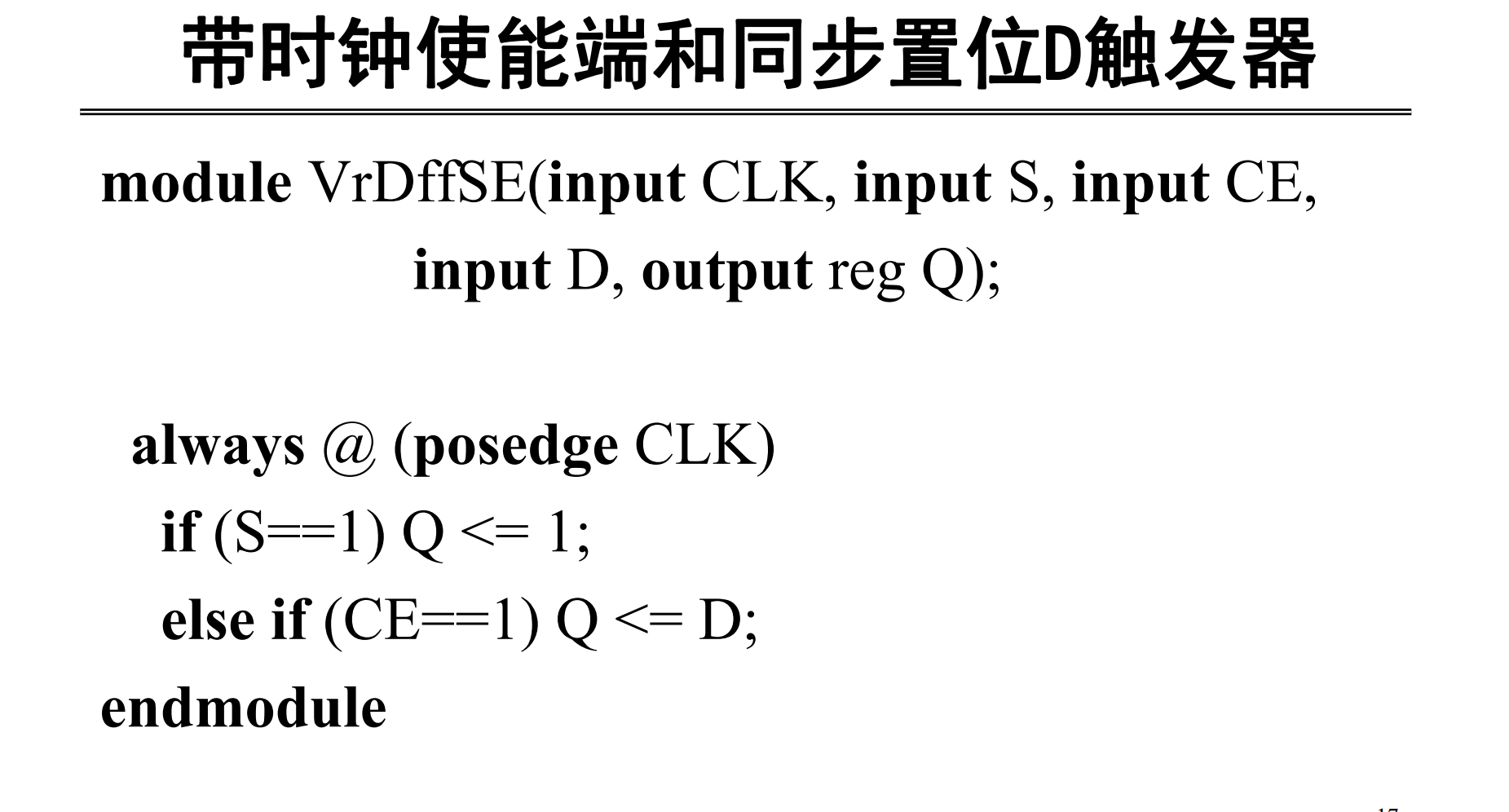

使能端为1的时候,D就会被选中,也就有用了。时钟信号是很敏感的东西,把使能端和CLK放一起,不怕最后时钟动了的时候CK不该,使能端动了CK改?所以不要这样做。

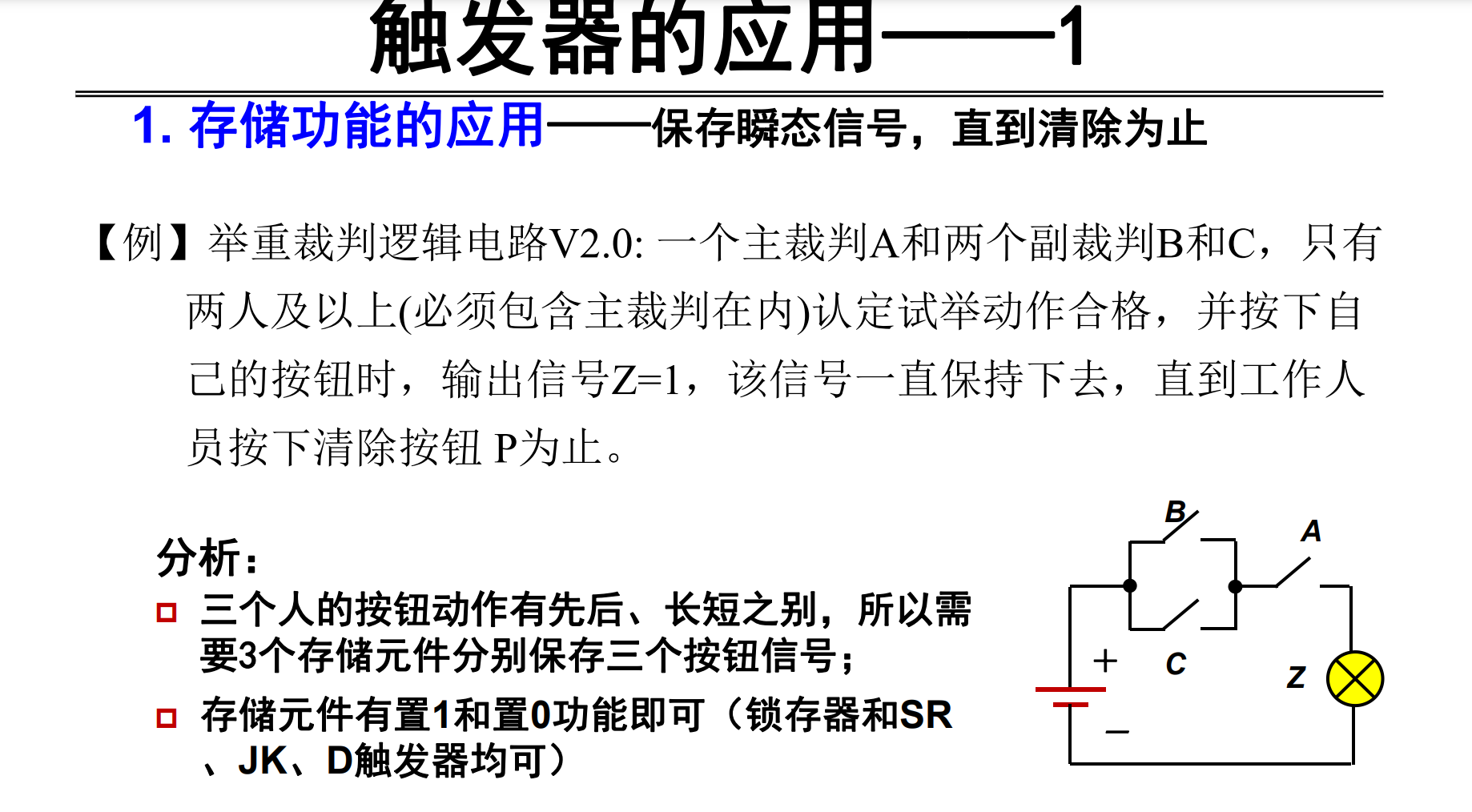

触发器有哪些用处呢?:

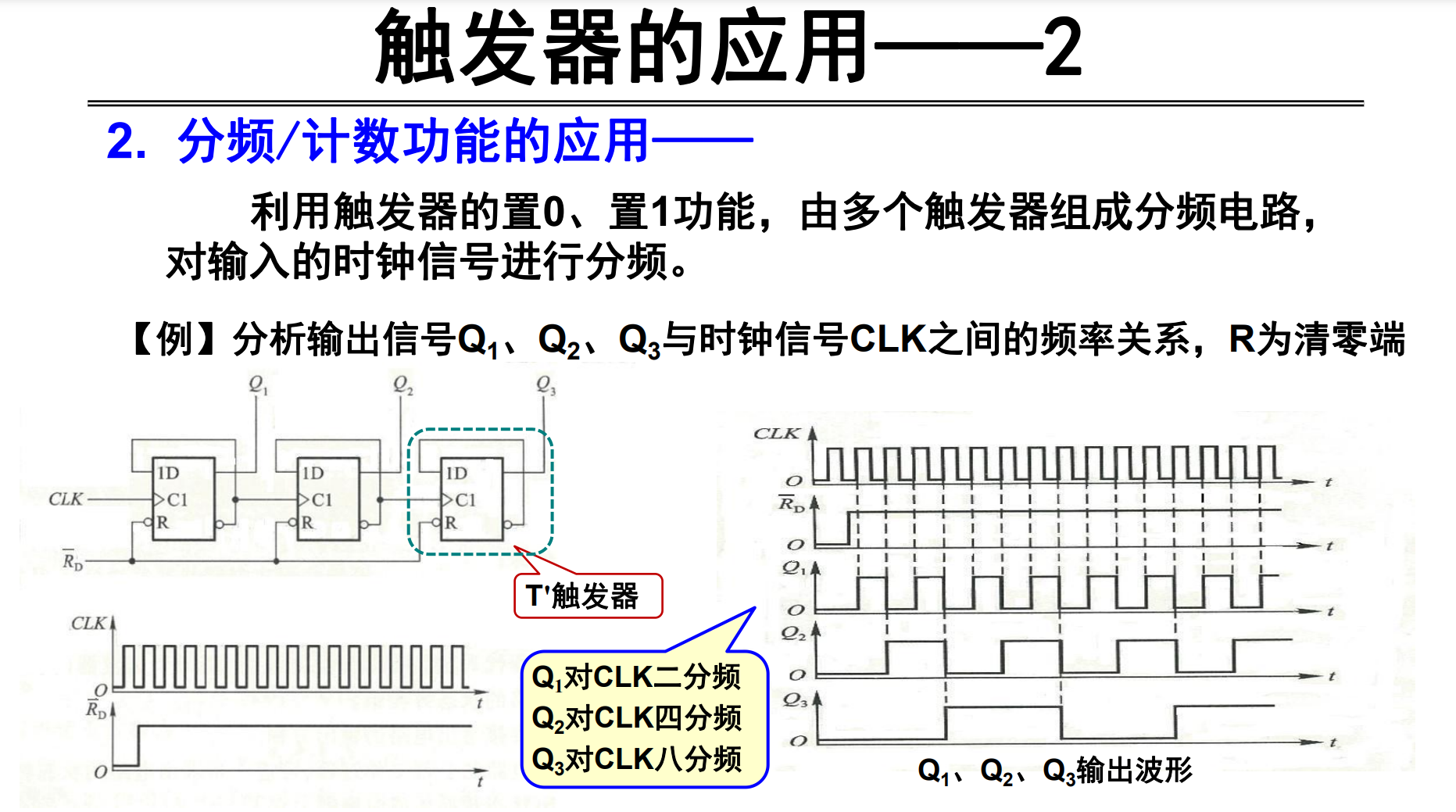

可以看到,Q1只对CLK的上沿感兴趣,所以只有2分频;Q2只对Q1的上沿感兴趣,只有Q1的二分频,结果就成了CLK的4分频。后面的以此类推。这里用的是T触发器,所以会有一输入就反转的效果。

最后

以上就是唠叨汉堡最近收集整理的关于数字逻辑:时序逻辑元件——锁存器的全部内容,更多相关数字逻辑内容请搜索靠谱客的其他文章。

发表评论 取消回复