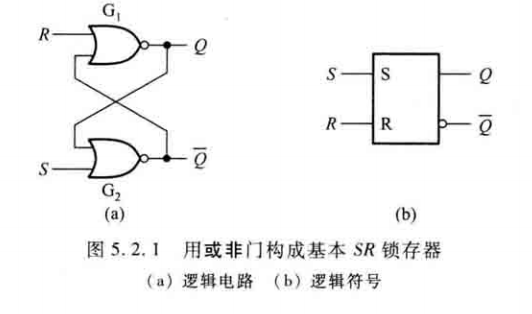

或非门构成的基本SR锁存器

1、结构

- 输入端 S、R

- 输出端Q、Q’

输入端S、R是两个或非门G1、G2。

| 门 | 输入端 | 反馈端 |

|---|---|---|

| G1 | R | Q’ |

| G2 | S | Q |

2、工作状态

根据S、R输入端的四种状态,基本SR锁存器有四种对应的工作状态

| S 、R | Q、Q’ | 功能 |

|---|---|---|

| 0,0 | 不变,不变 | 保持 |

| 1,0 | 1,0 | 置位,置1 |

| 0,1 | 0,1 | 复位,置0 |

| 1,1 | 0,0 | 禁止态 |

查看以上功能表,可以发现,或非门构成的基本SR锁存器根据输入的不同可以分为允许工作态和禁止态。

当SR=1,锁存器无法正常工作

当SR=0,锁存器可以根据SR的三种组合状态分为保持,置位,复位三种工作模式。

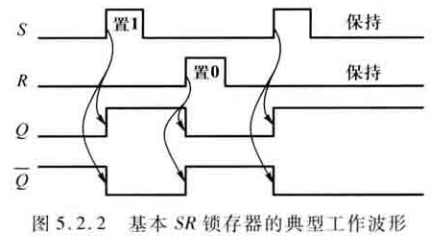

3、或非门构成的SR锁存器的典型工作波形

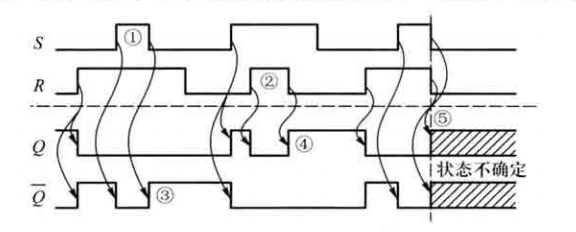

从第二幅图中可以看出几个特殊状态:① ② ⑤

- 状态①:S,R=1,1 此时为锁存器的非正常工作状态,超越了SR=0的约束,出现Q=Q’=0的错误输出。但是其后S首先下降,这样又避免了S、R同时下降置零,可以立马恢复正常工作态。

- 状态②:S,R=1,1 此时为锁存器的非正常工作状态,超越了SR=0的约束,出现Q=Q’=0的错误输出。但是其后R首先下降,这样又避免了S、R同时下降置零,也可以恢复正常工作态。

- 状态⑤:在S、R出现非正常工作输入的情况后,S和R又同时置零,导致输出保持了S,R=1,1的错误输出状态。这样就会使得输出一直保持在错误的输出下。

以上分析可见,无论是S、R是否同时置0,都将使得整体工作波形中出现短暂或者长期的错误输出。这样的SR输入在实际应用中应该避免。

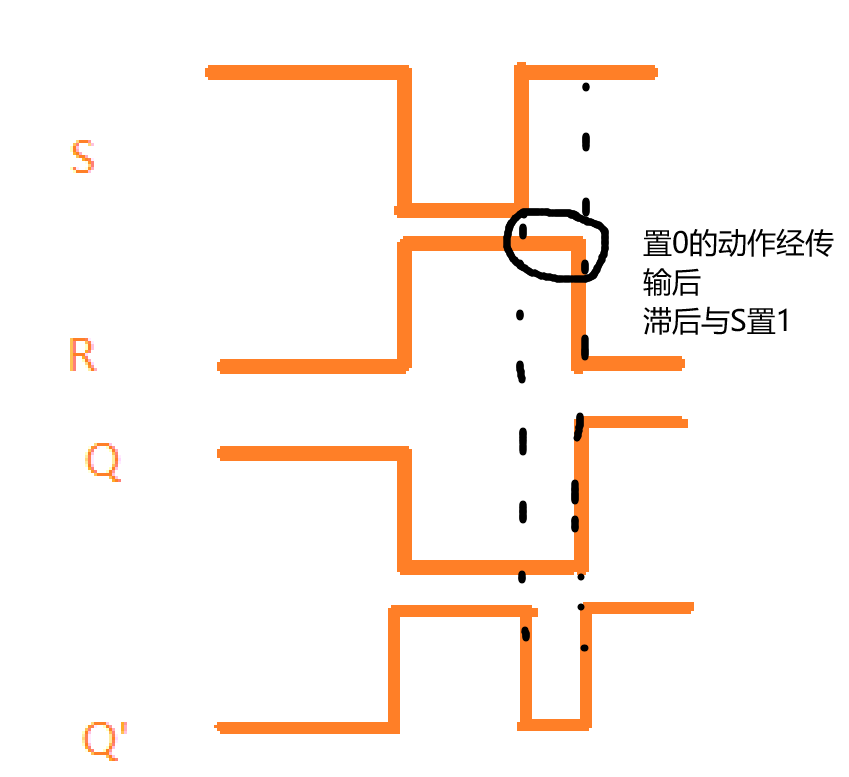

4、基本SR锁存器的动态特性

由于G1,G2两个或非门不同的传输延迟,导致在信号传输中可能发生以下情况:

- 在S、R从0,1状态变为1,0状态时,由于G2门的传输延迟较小,导致S信号首先传出,R信号滞后,这样就会形成短暂的1,1状态,这样就会在输出上产生0,0的错误。上面我们已经知道,在实际使用中应避免这种状态。

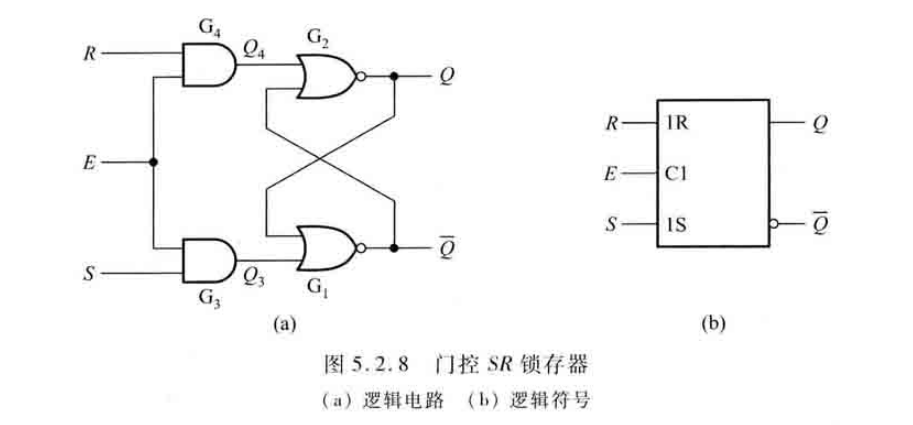

5、门控SR锁存器

在基本SR锁存器输入端做了处理:

- 添加两个逻辑与门G3、G4

- 添加使能信号与S、R进行与运算

引入使能信号,可以实现

- 在特定的时刻根据SR的信号输出

- 多个锁存器并行同步锁存数据

最后

以上就是聪明芒果最近收集整理的关于数组逻辑电路---SR锁存器的全部内容,更多相关数组逻辑电路---SR锁存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复