基于Primitive实现的四位二进制计数器

1.原理

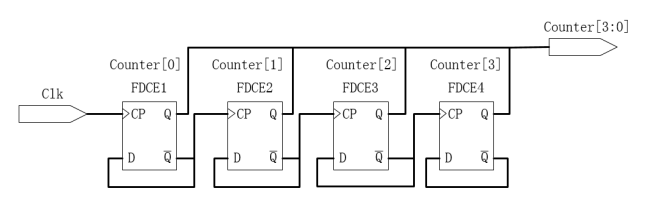

先看下图设计的四位二进制计数器电路:

采用上升沿触发的D触发器,所有触发器初始输出状态在Primitive里设置为0,即第零态为0000,所以四个D触发器的初始输入状态均为1,搞清楚初始输入输出状态后,下面进入正式原理分析:

当第一个Clk上升沿到来时,FDCE1输入端初态1送入Q,即Q=1,此导致Q非端及D端为0,而FDCE2时钟端此时正由1—>0,为下降沿,故其Q端状态不变,易分析FDCE3、FDCE4 Q端状态也保持不变为0,此为第一个状态0001(注意图中FDCE4为高位,FDCE1为低位)。

当第二个Clk上升沿到来时,FDCE1输入端状态0送入Q,即Q=0;此导致Q非端及D端为1,而FDCE2时钟端此时正由0—>1,为上升沿,故其D端初态1送入Q端,即Q=1,此导致其Q非端及D端为0,而FDCE3时钟端此时正由1—>0,为下降沿,故其Q端状态不变为0,易分析FDCE4 Q端状态也保持不变为0,此为第二个状态0010。

当第三个Clk上升沿到来时,FDCE1输入端状态1送入Q,即Q=1;此导致Q非端及D端为0,而FDCE2时钟端此时正由1—>0,为下降沿,故其Q端状态不变,即Q=1,所以Q非端不变,易分析FDCE3,FDCE4Q端也保持不变,此为第三个状态0011。同理可分析得到剩余的十二个状态。

通过上述分析过程可发现,FDCE1为受控Clk上升沿触发,FDCE2为受控FDCE1 Q非端上升沿触发,FDCE3为受控FDCE2 Q非端上升沿触发,FDCE4为受控FDCE3 Q非端上升沿触发。

十六个状态表:

| Counter[3] | Counter[2] | counter[1] | counter[0] | |

|---|---|---|---|---|

| 零态 | 0 | 0 | 0 | 0 |

| 第1个Clk上升沿 | 0 | 0 | 0 | 1 |

| 第2个Clk上升沿 | 0 | 0 | 1 | 0 |

| 第3个Clk上升沿 | 0 | 0 | 1 | 1 |

| 第4个Clk上升沿 | 0 | 1 | 0 | 0 |

| 第5个Clk上升沿 | 0 | 1 | 0 | 1 |

| 第6个Clk上升沿 | 0 | 1 | 1 | 0 |

| 第7个Clk上升沿 | 0 | 1 | 1 | 1 |

| 第8个Clk上升沿 | 1 | 0 | 0 | 0 |

| 第9个Clk上升沿 | 1 | 0 | 0 | 1 |

| 第10个Clk上升沿 | 1 | 0 | 1 | 0 |

| 第11个Clk上升沿 | 1 | 0 | 1 | 1 |

| 第12个Clk上升沿 | 1 | 1 | 0 | 0 |

| 第13个Clk上升沿 | 1 | 1 | 0 | 1 |

| 第14个Clk上升沿 | 1 | 1 | 1 | 0 |

| 第15个Clk上升沿 | 1 | 1 | 1 | 1 |

2.Primitive描述

FDCE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDCE_inst1 (

.Q(Counter[0]), // 1-bit Data output

.C(clk), // 1-bit Clock input

.D(~Counter[0]) // 1-bit Data input

);

FDCE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDCE_inst2 (

.Q(Counter[1]), // 1-bit Data output

.C(~Counter[0]), // 1-bit Clock input

.D(~Counter[1]) // 1-bit Data input

);

FDCE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDCE_inst3 (

.Q(Counter[2]), // 1-bit Data output

.C(~Counter[1]), // 1-bit Clock input

.D(~Counter[2]) // 1-bit Data input

);

FDCE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDCE_inst4 (

.Q(Counter[3]), // 1-bit Data output

.C(~Counter[2]), // 1-bit Clock input

.D(~Counter[3]) // 1-bit Data input

);

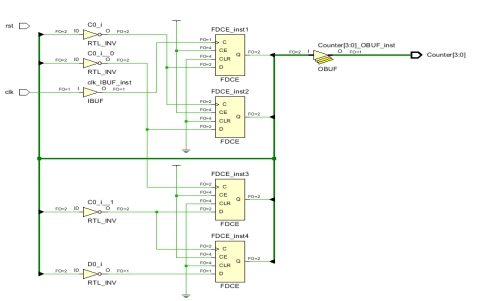

3.电路图

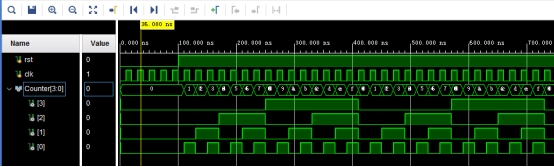

4.仿真结果

5.总结

BmbngX-1660895167350)]

4.仿真结果

[外链图片转存中…(img-MUm0cMcU-1660895167351)]

5.总结

计数器设计并不难,但主要是弄明白其原理,并熟悉Primitive设计的基本方法,这种类IP核的设计方法简单且有效。

最后

以上就是幸福向日葵最近收集整理的关于基于Primitive实现的异步四位二进制计数器基于Primitive实现的四位二进制计数器的全部内容,更多相关基于Primitive实现内容请搜索靠谱客的其他文章。

![[笔记] Johnson计数器(十)](https://www.shuijiaxian.com/files_image/reation/bcimg23.png)

发表评论 取消回复