目录

- 引言

- CTS基础

-

- 什么是时钟树综合

-

- 时钟源

- CTS

- OCV(on-chip variation)

- 时钟树综合的目标

-

- 1. clock latency 尽量短

- 2. clock skew 尽量小

- 时钟树结构

- 时钟树综合前的准备

-

- 标准设计约束文件(SDC)

- CTS 前的要求

- 时钟树工作条件确认

- 时钟树质量分析

- 参考

引言

数字设计中时钟是非常重要的一部分,时钟信号通常是整个芯片中有最大扇出、通过最长距离、以及最高速度运行的信号。今天的芯片设计中总的动态功耗的30%甚至更多都是消耗在时钟网络上。在后端保证时钟质量的步骤就是时钟树综合(Clock tree synthesis,CTS),这是后端物理设计的关键步骤之一。

CTS基础

什么是时钟树综合

时钟源

芯片中的时钟是如何获取以及如何供应给各个功能模块,一般有如下方法:

-

外部直接输入时钟信号

这种情况比较少见。由于SOC系统中不同功能模块工作的频率不一样,因此从外部直接拉时钟信号进芯片,不具备可行性。对于某些特别简单的ASIC芯片,可能有机会用到这种方案。 -

外部晶振+内部时钟发生器

这种方案是从外部晶振引入 IO,与内部时钟发生器产生一个24MHz时钟信号,然后供给各种功能模块。 -

外部晶振+内部时钟发生器+内部PLL产生高频时钟+内部分频器得到各种频率的时钟

这种时钟获取方式是目前 SOC 芯片设计实现中普遍采用的时钟产生方案。这个方案的整体思路是先从晶振,时钟发生器产生一个24MHz信号,再经过 PLL 产生倍频时钟(高频时钟),最后再经过分频电路产生各种频点的时钟供给各个功能模块。

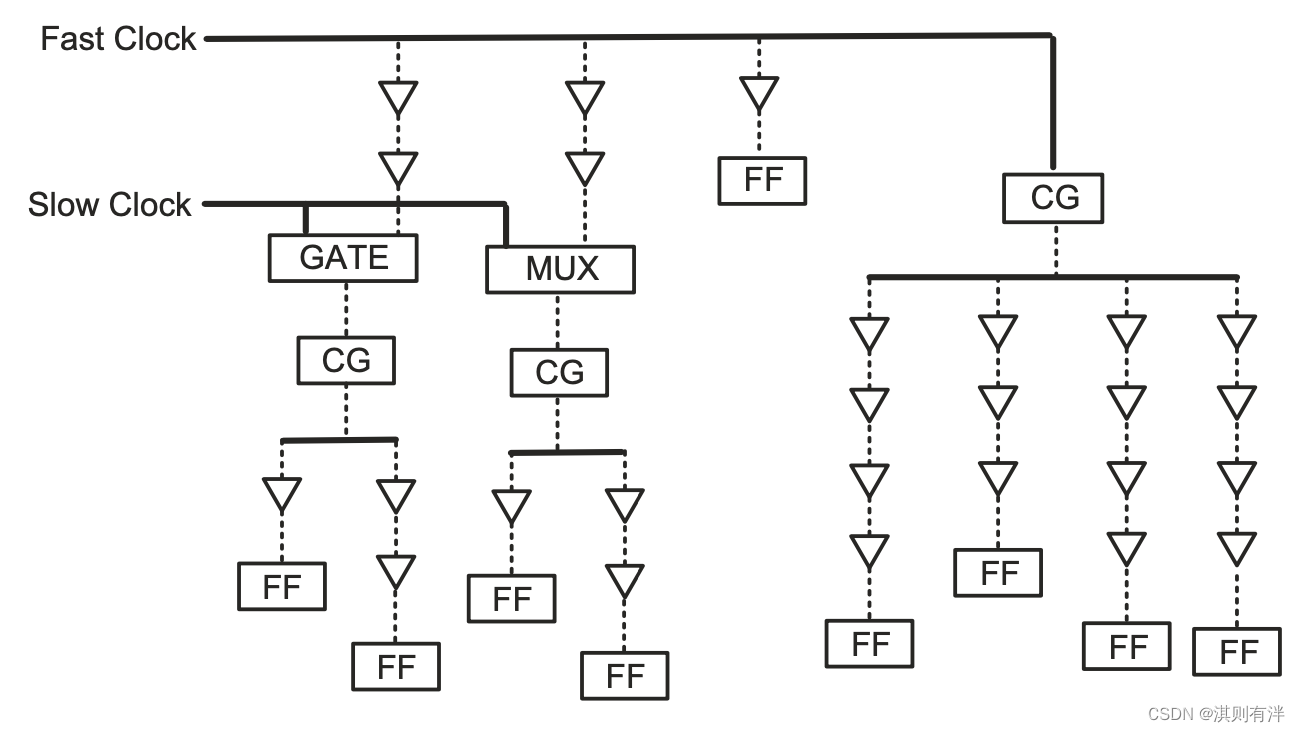

CTS

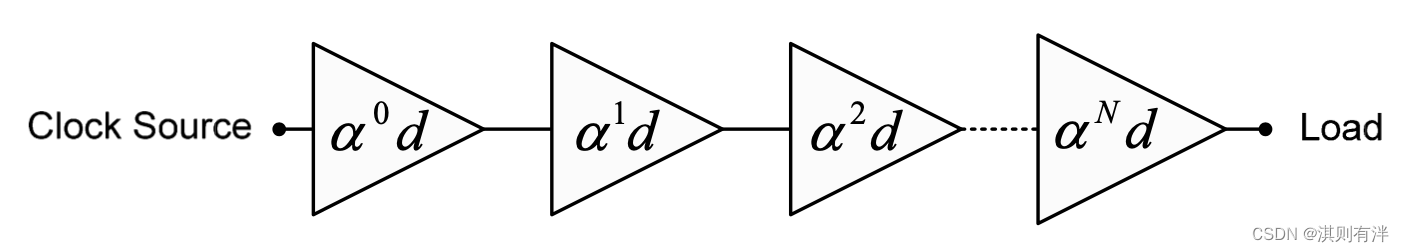

时钟网络由于布线很长,电阻和电容比较大。时钟树综合的概念是指沿着 ASIC 设计的时钟路径自动插入缓冲器(buffers)/反相器,以平衡所有时钟输入的时钟延迟。时钟树就是指从某个 clock 的 root 点长到各个 sink 点或叶节点(leaf)的 clock buffer/inverter tree。工具试图将某个 clock 所属的所有 sinks 做到相同长度。

OCV(on-chip variation)

过去,电路延迟的不均一性是在不同批次之间观察到的。随着 ASIC 制造工艺的进步,晶圆对晶圆(wafer-to-wafer)和芯片对芯片(die-to-die)的差异也变得明显。而在当前的深亚微米工艺中,延迟的不均一性在单个芯片上也可以看到,也即 OCV 。

如果时钟树算法选择在靠近时钟源的地方分支时钟路径而不是靠近叶单元,那么很可能会出现时钟偏移(skew)。

这意味着 CTS 算法必须能够在缓冲区插入期间尽可能多地使用公共路径(common path)。在这种情况下,每个时钟路径上的延迟差异将是局部的,而通过公共路径的延迟不会由于芯片上的变化而导致时钟偏移。

时钟树综合的目标

1. clock latency 尽量短

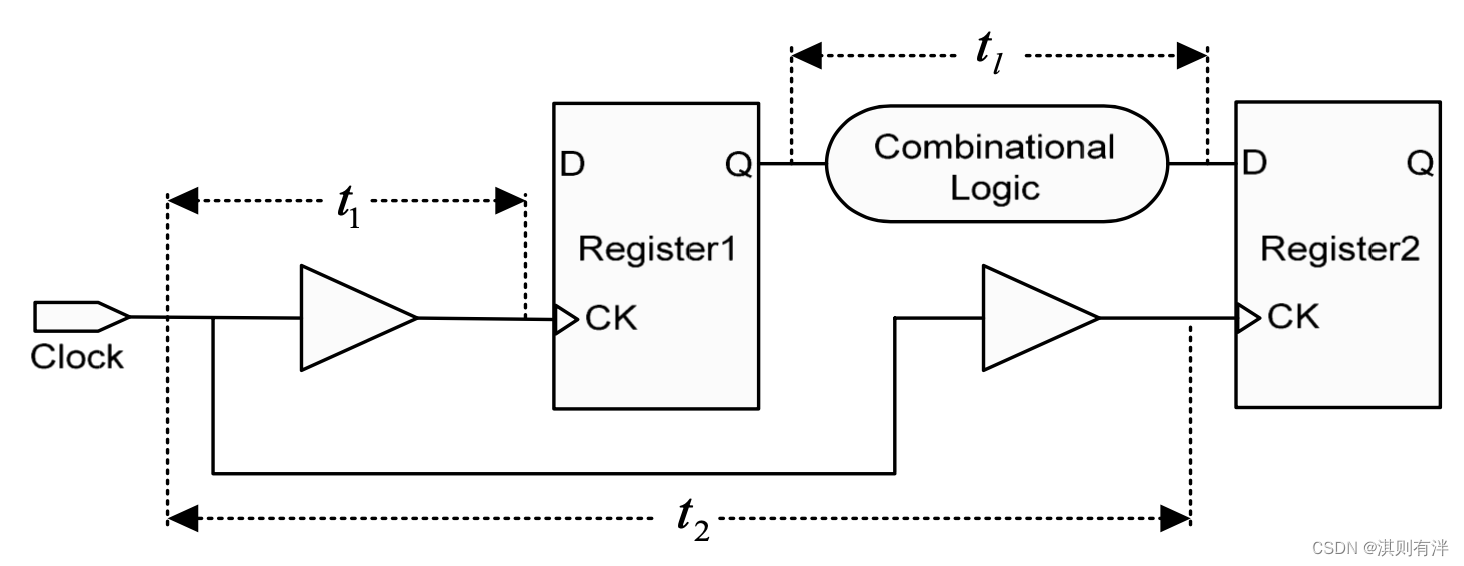

时钟信号的延滞(Latency)又被称为插入延迟(insertion delay),包括两部分:时钟源插入延迟和时钟网络插入延迟。时钟源插入延迟是来自系统(时钟源或来自芯片)到当前芯片(或模块)时钟根节点的延迟。时钟网络插入延迟是时钟树的延迟。

Clock tree 越长,意味着 clock tree 级数越长,级数长了,tree 上的 power 就越大。同时,受 OCV 效应影响,timing 就越难 meet 。

2. clock skew 尽量小

clock skew(时钟偏移)是表示两个 sink clock latency 的差值,分为 Global skew 和 Local skew 两大类。Global skew 是泛指 design 中任意两个寄存器 latency 之差的最大值。Local skew 是指 design 中两个相关寄存器 latency 之差的最大值。在数字后端设计中,更多关注 local skew。因为 local skew 会直接影响到时序的 setup 和 hold。对于 Positive skew 来说,Tskew 大于0,setup slack 变大,但是 hold slack 变小了。而对于 Negative skew,Tskew 小于0,setup slack 变小,hold slack 变大了。

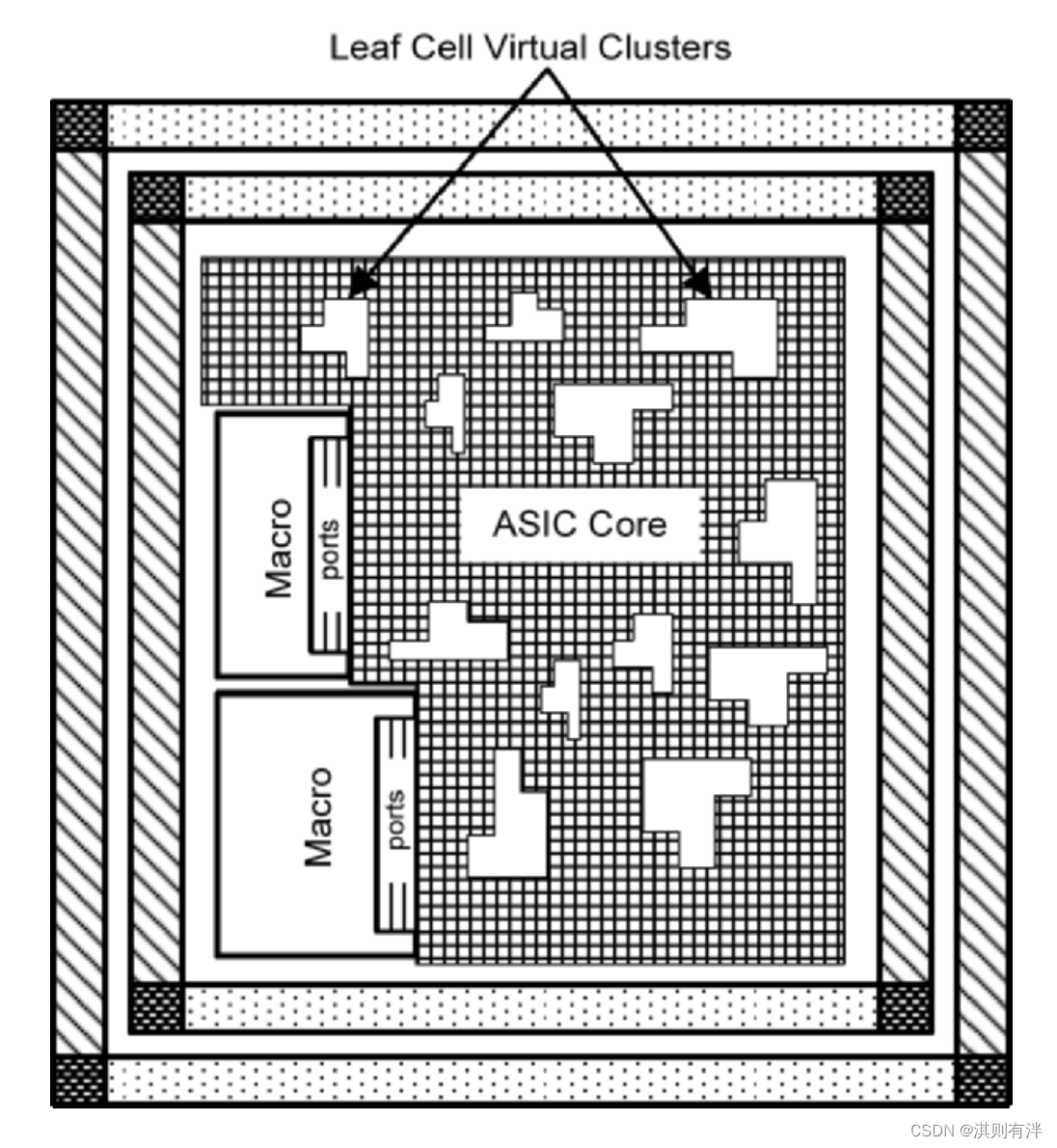

大多数 CTS 算法首先通过创建 virtual cluster 来识别 leaf registers 或 sink points 。virtual cluster 是通过识别彼此非常接近的 leaf cell 的位置来实现的。如果 leaf cell 远离任何簇,它们将被移动到最近的簇。每个簇的叶单元数由用户定义。一旦确定了簇及其位置,就会插入 buffer 使得每个簇时钟传播延迟相等,并且每个簇内的时钟偏移最小化。应该注意的是,簇越小,时钟偏移越小,但需要更多的时钟缓冲级,这有增加整体时钟传播延迟的趋势。

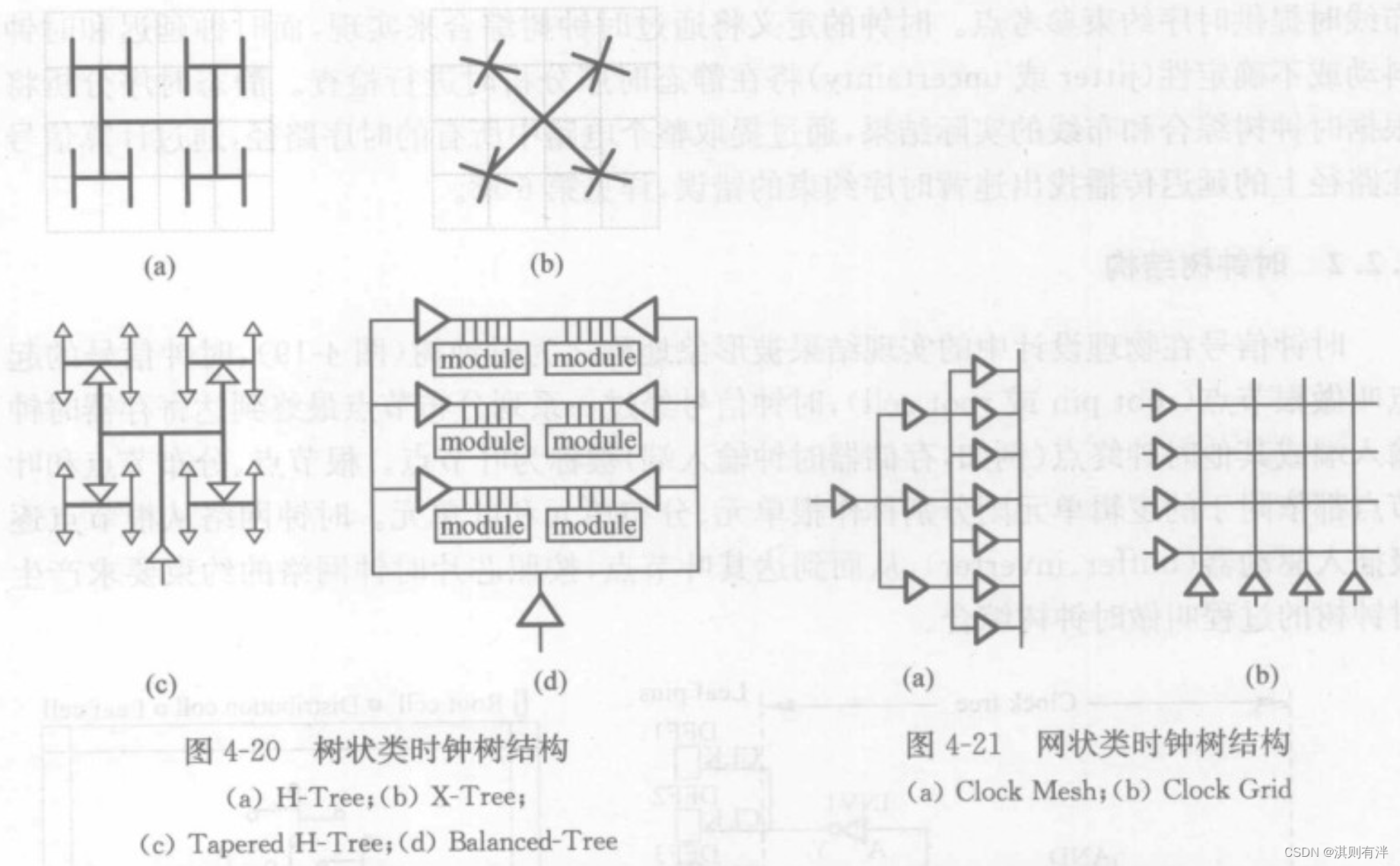

时钟树结构

时钟树根据其在芯片内的分布特征,可分为多种结构,主要类型有两种:树状(Tree)和网格(mesh)。具体有 H-tree、X-tree、balanced tree,Clock mesh、Clock Grid等种类。

时钟树综合前的准备

在 CTS 之前,了解设计的时钟结构和平衡要求非常重要,以便决定适当的例外情况并能够构建最佳时钟树。拿到一个 design,需要先花点时间,理清楚 clock 结构,各种 mode 如何切换。知道哪些clock 是需要同步,哪些是异步。一般情况下,中等规模及以上的 SOC 芯片的时钟树综合,都是需要编写时钟树约束文件。如果能够对时钟结构进行拆分,把时钟结构很清晰地告诉工具,那么它还是能够做的非常漂亮的。所以画时钟结构图和写时钟约束文件都是数字IC后端工程师必备的一项工作技能。

标准设计约束文件(SDC)

时钟树约束文件中首先是对时钟信号本身的定义,它们直接来源于标准设计约束文件。SDC 文件主要由三部分组成:时钟定义、输入延迟和输出延迟。在顶层设计中,还需要约束输入端口的驱动以及输出端口的负载等信息。对于多时钟的负载 SOC 设计,还需要根据设计的具体情况设定多周期检查路径、冗余的伪路径以及最大和最小延迟时间等约束。

CTS 前的要求

- 设置 DRC 参数

设置 max_transition max_capacitance max_fanout 等参数。对于 clock 的 max transition 的设置,应该根据 clock 的频率来设置。高频率的 clock,需要额外设置严格点。 - 指定 clock inverter list

clock inverter cell list 的选择往往比较有讲究。在做 CTS 综合时,往往采用 clock inverter 来做时钟树,防止 cell 的 rise delay 和 fall delay 不平衡导致 duty cycle 出问题。一般情况下 fab 都会给出建议。往往是驱动中等的几类cell。以 TSMC28 为例,官方建议 clock inverter 应该选用三款 cell,分别是 CKND8,CKD12,CKD16 的 cell 。

大驱动的 clock inverter(比如 CKND20,CKD24)容易出现 EM 问题。

而小驱动的 clock inverter(比如 CKND2),受 PVT 影响比较大,容易出现较大的工艺偏差。

用来 build clock tree 的 clock inverter 必须使用 LVT 或者 SVT,而且必须保证 clock tree 上只有一种 VT 。HVT cell 禁止使用在 clock tree 上,因为工艺偏差较大,导致 signoff 的 timing 和实测严重不符,甚至导致功能错误。 - 设置 don’t_use cell list

- 设置 floating pin 和 inter-clock balance

很多时候为了将某些 reg 做短(可能是 timing 考虑,可能是 clock latency 的要求),需要设置 floating pin。有的 hierarchical design,需要告诉工具子模块中 clock latency 的长度,也要设置 floating pin 。

当两个时钟并不是同步的,但是他们的某些 register 会进行 talk 。默认情况下,CTS build CLOCK1 和 CLOCK2 时,会各自 build clock tree,不会做 inter-clock balance 。因此,需要设置 inter-clock balance 选项:

set_inter_clock_delay_options -balance_group "Clk1 Clk2" -balance_group_name group2 - 设置 NDR rule

为了防止 clock 上的 SI 和 EM,我们需要对时钟信号线进行 non-default rule 的设置。通常设置两倍宽度,两倍间距(当然也有更大,根据实际情况进行更改)。

define_routing_rule CTS_NDR_RULE -widths { M2 0.15 M3 0.15 M4 0.15 M5 0.15 M6 0.15 } -spacings { M2 0.15 M3 0.15 M4 0.15 M5 0.15 M6 0.15 }

由于标准单元出 pin 大部分是 M1/M2,如果设置 ndr rule,会导致很多 DRC。因此,可以将最 leaf 端采用默认的线宽和线间距来走线。

set_clock_tree_options -routing_rule_ rule -use_default_routing_for_sinks 1

为了使得 clock tree 质量更好,往往将高层用来作为时钟信号的走线。

set_clock_tree_options -layer_list {M7 M8}

除了对 clock net 设置 NDR 外,还需要对某些对时钟质量要求比较高的 clock,进行 shielding。 - Apply IO Latency

set_latency_adjustment_options -from_clock clk -to_clock virtual_clk

(如果 IO port 是用 virtual clock 来 constraint 的,通过此命令来进行 IO Latency 的 apply)

update_clock_latency

时钟树工作条件确认

- 时钟定义正确

Clock source 应该是通过 create_clock 或者 create_generated_clock 来声明的。Generated clock 定义的点必须能 trace 到 source 上。

create_generated_clock

在数字IC设计中,芯片中各个模块的工作频率可能都不太一样。因此有了时钟产生电路(clock generation)。通常通过 create_generated_clock 来定义分频和倍频后的时钟,说明 generated clock 与source clock 的相位(边沿)关系。同时根据 source clock 找到 master clock 以及 source clock 和master clock 的关系, 最终会确定 generated clock 和 master clock 的相位(边沿)关系。 - 标准单元已经正常摆放好

使用 check_legality –verbose 来检查所有标准单元是否 legal 。如果对一个存在 illegal 的模块进行时钟树综合,其 QoR 会比较差,而且会加倍整个 runtime。 - Congestion 适度

如果一个模块 placement 做完之后 congestion map 特别差,存在特别大的 overflow,那么基于这样的database 继续做时钟树综合意义不是很大。一方面是 QoR 会比较差,另外一方面是 CTS 后 congestion 会更差,模块本身一定是绕不通的。 - Timing 可接受

Placement 后时序要差不多符合设计要求。如果 placement 后 wns 是500ps左右,那继续 tune cts 也是没太大意义。因为本身 placement 没做好,即标准单元的摆放位置并不是很合理。此时应该返回 place 阶段,进一步 fine tune timing。 - DRV(Max transition Max capacitance)可接受

- Power & Ground net 已经 prerouted

- 高扇出的 net,比如 scan 使能端,已经解过 fanout(时钟树综合后存在特别大的 max transition 问题)

- Floorplan 是否对时钟树友好

比如细长条 memory 之间的 channel,未进行特殊处理。这种情况,如果 reg 被摆放进去,很有可能导致比较大的 clock skew 或者拖长 clock tree。 - Placement 后逻辑分布合理

时钟树质量分析

可以从 log 中看到每个 clock 长 tree 的情况,比如 clock latency,clock skew,某个 clock domain 中最长的 clock path 和最短的 clock path。时钟树结果主要关注 clock skew,clock latency 。查看工具做出来的 skew 和 latency 是否符合设计要求,是否是最优的。如果不是,要根据实际情况进行调整和优化。

参考

微信公众号:吾爱IC社区

陈春章等,《数字集成电路物理设计》

Andrew B.kahng, etc 《VLSI Physical Design: From Graph Partitioning to Timing Closure》

Khosrow Golshan 《The Art of Timing Closure》

最后

以上就是知性电脑最近收集整理的关于时钟树综合(CTS)引言CTS基础时钟树综合前的准备时钟树质量分析参考的全部内容,更多相关时钟树综合(CTS)引言CTS基础时钟树综合前内容请搜索靠谱客的其他文章。

发表评论 取消回复