1、clock gating check的条件

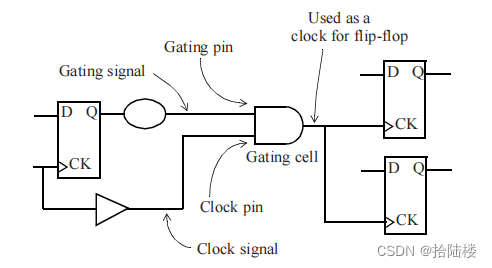

一个非buffer/inverter的组合逻辑单元可以由gating控制信号控制其clock信号传递的时候,在STA时序分析时会将其作为clock gating cell(如下图),并做clock gating check。

所以clock gating check的前提条件是:

1)Gating cell的Gating pin所连接的Gating信号不能是clock信号。

2)Gating cell的输出作为clock信号的下游,可以接flip flop的clock pin,可以接output port,也可以作为generate clock的source pin。

2、clock gating check的类型

常见的gaing cell的组合逻辑部分为and门或者or门。也对应两种clock gating check的类型:

1)高电平有效(Active-high)的clock gating check,通常结构为and/nand。

2)低电平有效(Active-low)的clock gating check,通常结构为or/nor。

其中Active-high和Active-low指的是gating信号的状态,如果一个gating cell的功能过与复杂,例如mux或者xor,STA分析可能无法识别gating cell,自然无法做clock gating check,这个时候用户可以自行使用set_clock_gating_check去指定gating cell的gating关系。

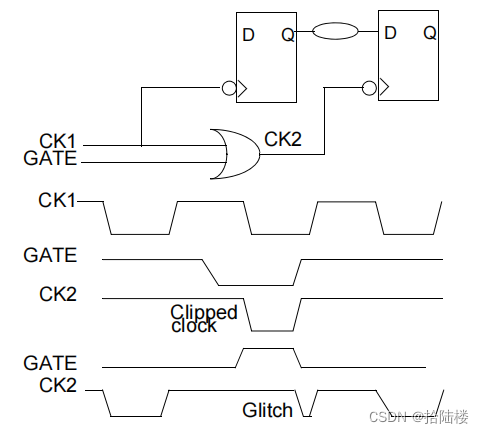

2.1 Active-High Clock Gating

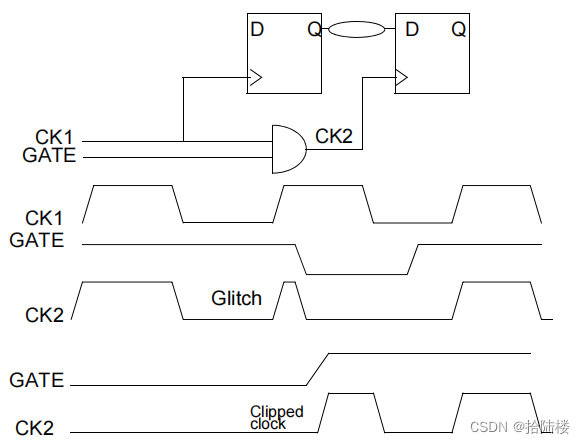

多出现在gating cell为and或nand的情况下,gating信号为高电平有效,gating信号为低电平时,门控关闭,为了保证gating cell输出不产生毛刺(glitch)或者削切(clipped)时钟波形,需要让clock信号为低电平时gating信号发生变化,如下图。

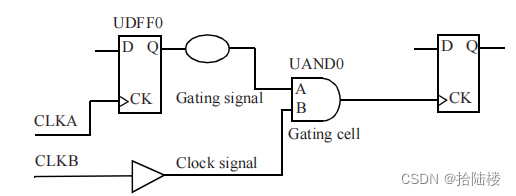

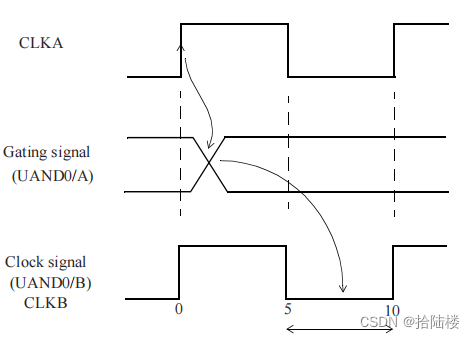

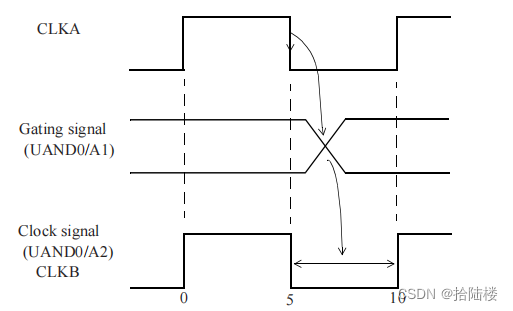

举例来说,UDFF0为上升沿触发的寄存器,UAND0为与门结构的gating cell,如下图。

create_clock -name CLKA -period 10 -waveform {0 5}

[get_ports CLKA]

create_clock -name CLKB -period 10 -waveform {0 5}

[get_ports CLKB]

为了保证UAND0输出信号没有glitch或者clipped,gating信号需要在CLKB为低电平时发生变化。所以setup和hold的检查的范围在5-10ns之间,这就导致hold检查的时候做半周期检查时序很难收敛。

Startpoint: UDFF0

(rising edge-triggered flip-flop clocked by CLKA)

Endpoint: UAND0

(rising clock gating-check end-point clocked by CLKB)

Path Group: **clock_gating_default**

Path Type: min

Point Incr Path

---------------------------------------------------------------

clock CLKA (rise edge) 0.00 0.00

clock source latency 0.00 0.00

CLKA (in) 0.00 0.00 r

UDFF0/CK (DF ) 0.00 0.00 r

UDFF0/Q (DF ) 0.13 0.13 r

UAND0/A1 (AN2 ) 0.00 0.13 r

data arrival time 0.13

clock CLKB (fall edge) 5.00 5.00

clock source latency 0.00 5.00

CLKB (in) 0.00 5.00 f

UAND0/A2 (AN2 ) 0.00 5.00 f

clock gating hold time 0.00 5.00

data required time 5.00

---------------------------------------------------------------

data required time 5.00

data arrival time -0.13

---------------------------------------------------------------

slack (VIOLATED) -4.87假设UDFF0是下降沿触发,那么就可以避免这个问题(此时的setup检查为半周期)。如下图。

Startpoint: UFF0

(falling edge-triggered flip-flop clocked by CLKA)

Endpoint: UAND0

(rising clock gating-check end-point clocked by CLKB)

Path Group: **clock_gating_default**

Path Type: min

Point Incr Path

---------------------------------------------------------------

clock CLKA (fall edge) 5.00 5.00

clock source latency 0.00 5.00

CLKA (in) 0.00 5.00 f

UFF0/CKN (DFN ) 0.00 5.00 f

UFF0/Q (DFN ) 0.13 5.13 f

UAND0/A1 (AN2 ) 0.00 5.13 f

data arrival time 5.13

clock CLKB (fall edge) 5.00 5.00

clock source latency 0.00 5.00

CLKB (in) 0.00 5.00 f

UAND0/A2 (AN2 ) 0.00 5.00 f

clock gating hold time 0.00 5.00

data required time 5.00

---------------------------------------------------------------

data required time 5.00

data arrival time -5.13

---------------------------------------------------------------

slack (MET) 0.13所以,常见的ICG高电平有效的结构多为低电平触发的latch+and的形式。

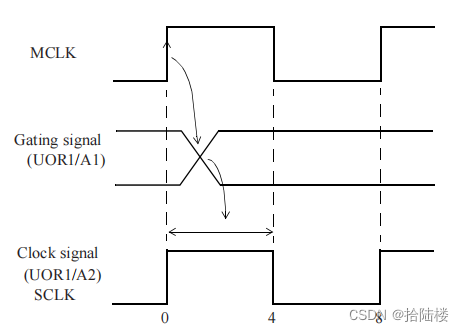

2.2 Active-Low Clock Gating

多出现在gating cell为or或nor的情况下,gating信号为低电平有效,gating信号为高电平时,门控关闭,所以gating信号必须在clock信号为高电平时变化才能保证没有glitch和clipped。如下图。

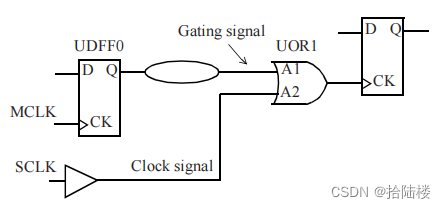

举例来说,UDFF0为上升沿触发,UOR1为gating cell。

create_clock -name MCLK -period 8 -waveform {0 4}

[get_ports MCLK]

create_clock -name SCLK -period 8 -waveform {0 4}

[get_ports SCLK]

为了保证UOR1输出不产生glitch和clipped问题,gating信号需要在SCLK为高电平时才能发生变化,这就导致setup检查变成了半周期。

Startpoint: UDFF0

(rising edge-triggered flip-flop clocked by MCLK)

Endpoint: UOR1

(falling clock gating-check end-point clocked by SCLK)

Path Group: **clock_gating_default**

Path Type: max

Point Incr Path

---------------------------------------------------------------

clock MCLK (rise edge) 0.00 0.00

clock source latency 0.00 0.00

MCLK (in) 0.00 0.00 r

UDFF0/CK (DF ) 0.00 0.00 r

UDFF0/Q (DF ) 0.13 0.13 f

UOR1/A1 (OR2 ) 0.00 0.13 f

data arrival time 0.13

clock SCLK (fall edge) 4.00 4.00

clock source latency 0.00 4.00

SCLK (in) 0.00 4.00 f

UOR1/A2 (OR2 ) 0.00 4.00 f

clock gating setup time 0.00 4.00

data required time 4.00

---------------------------------------------------------------

data required time 4.00

data arrival time -0.13

---------------------------------------------------------------

slack (MET) 3.873 set_clock_gating_check与set_disable_clock_gating_check

当gating cell为mux或者xor等复杂功能cell时,STA分析的工具不会把它当成gating cell,用户可以手动设置 set_clock_gating_check去做clock gating check,默认情况下gating cell在做clock gating check时的setup、hold time都是0,用户可以用-setup/-hold手动指定一个值。

set_clock_gating_check -setup 0.2 -hold 0.4 [get_clocks CLK1]同理,当工具误把一个组合逻辑当成gating cell时也可以使用set_disable_clock_gating_check解除clock gating check。

set_disable_clock_gating_check U44/Z

最后

以上就是碧蓝秋天最近收集整理的关于静态时序分析—门控时钟检查(clock gating check)1、clock gating check的条件2、clock gating check的类型3 set_clock_gating_check与set_disable_clock_gating_check 的全部内容,更多相关静态时序分析—门控时钟检查(clock内容请搜索靠谱客的其他文章。

发表评论 取消回复