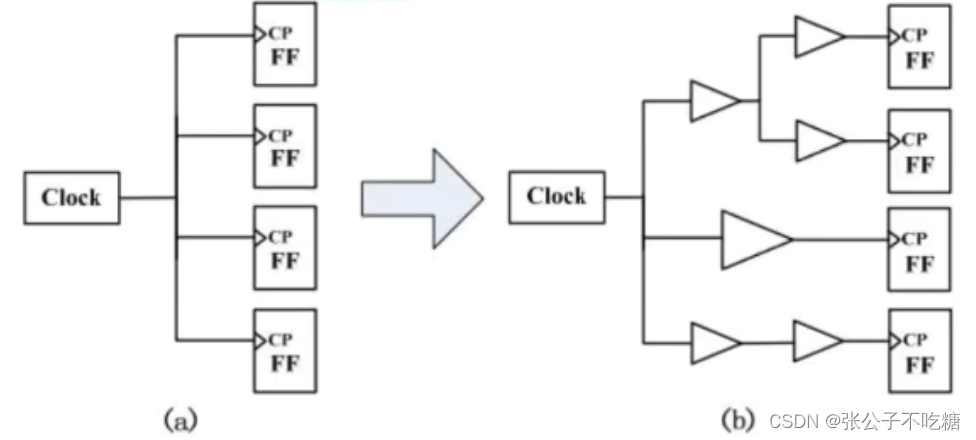

CTS的目的:建立一个buffer clock network,平衡clock path delays。

分2步:

1.CTS:把clock tree 网络建立起来,遵循DRC,解high fanout,max transition

2.CTO:调整clock tree结构,优化latency,降低skew。

CTS 目标:

1.满足DRC要求(Max cap/Max transition,Max fanout)

2.Clock latency

insetion delay = clock latency

3.Clock skew

4.others(Area/power/congestion)

CTS basic parameters definitions- latency

clock latency = source latency + network latency

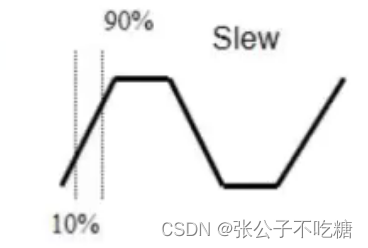

Slew/Transition

transition:低电平转换为高电平所需要的时间。

Clock tree 要设置max transition,因为:

1.考虑动态功耗,时钟信号一直反转,transition小,功耗降低

2.考虑timing,cell delay与transition相关,transition越小,cell delay越小。

为什么clk max transition比data path max transition卡得更严?

因为clk 后有很多DFF,关联的timing path很多,影响大。

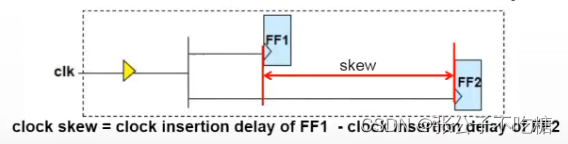

SKEW

skew:不同的时序逻辑latency的差值

做CTS的终极目标就是把skew做到0

1.global skew

一个时钟域里所有reg ck pin最大的skew

2.local skew

有timing check的DFF

CLock basic parameters definitions

clock uncertainty 在place时就考虑

Pre CTS uncertainty = estimated clock skew(预估的) + clock jitter + margin

Post CTS uncertainty = clock jitter + margin

Real clocks

真实存在的clock

1.与设计的至少一个pin或port相关联,并且物理存在

2.CTS将为real clock构建clock tree

Real clock的2个mode:

1.ideal clock

CTS之前,real clock就是ideal clock,clock insertion delay 为0

2.propagated clock

CTS之后,有了实际的buffer tree,real clock就是propagated clock,insertion delay 不是0

Virtual Clock

1. CTS不会做buffer tree

2.没有实际的source点

3.仅在STA分析中做参考,以指定相对于clock的input和output delay。

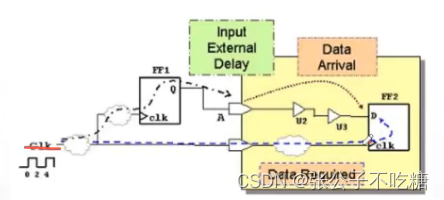

Input Delay:

表征外部的逻辑。在SDC里设置。

top上有1个DFF要与block上的1个DFF进行timing check,切block时,把这个path一分为二,把register一端放在top上,一端放在block上。2个port之间,加一个input delay模拟外部的长度。

最后

以上就是无语帽子最近收集整理的关于PR-Clock Tree IntroductionCTS basic parameters definitions- latencySlew/TransitionSKEW CLock basic parameters definitions的全部内容,更多相关PR-Clock内容请搜索靠谱客的其他文章。

发表评论 取消回复