明天就是数电的考试了,最后再总结一下,数电第四遍复习当中,发现的问题。

注意,文章不是详细地讲解知识点,而是适合有一定基础的人进行复习和一定拓展。

由于这篇文章是手机写的,所以排版看起来可能不太爽

下面是正文

BCD码,它是用二进制码来表示0--9这十个数,注意只有10个数!

比如,题目要求:设计一位8421BCD码的判奇电路,当输入码中1的个数为奇,输出1,否则输出0。那么,由于让设计的是一位BCD码,则只包含0-9,所以画真值表的时候,>9的数输出为❌,也就是无关项。

标准形式

有时候,题目会问一个逻辑表达式的标准形式是什么,实际上就是把他写成最小项之和或最大项之积

OC门全名

集电极开路门(ttl)

TS门全名

三态输出门(ttl)

CMOS 的TS门与TTL不同,前者为非 后者与非

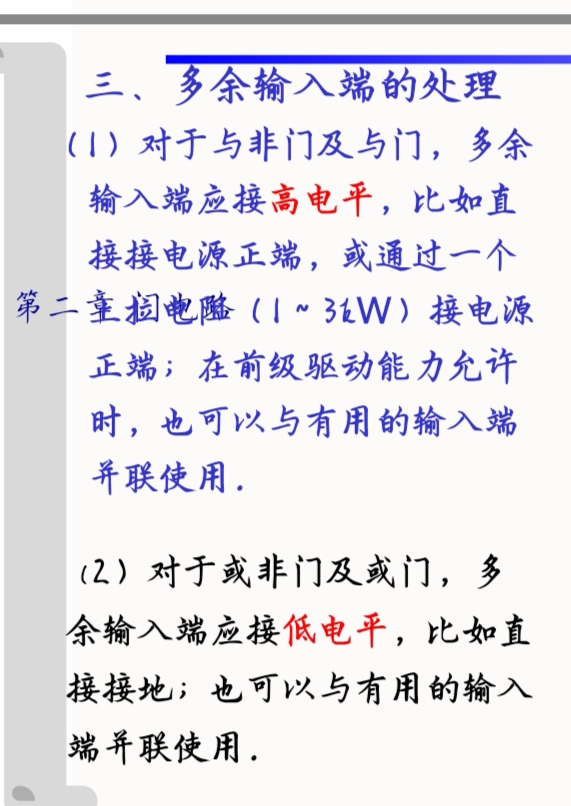

多余输入端处理

触发器的分类

根据逻辑功能

rs d jk t t'

根据电路结构

基本rs 同步 主从 边沿

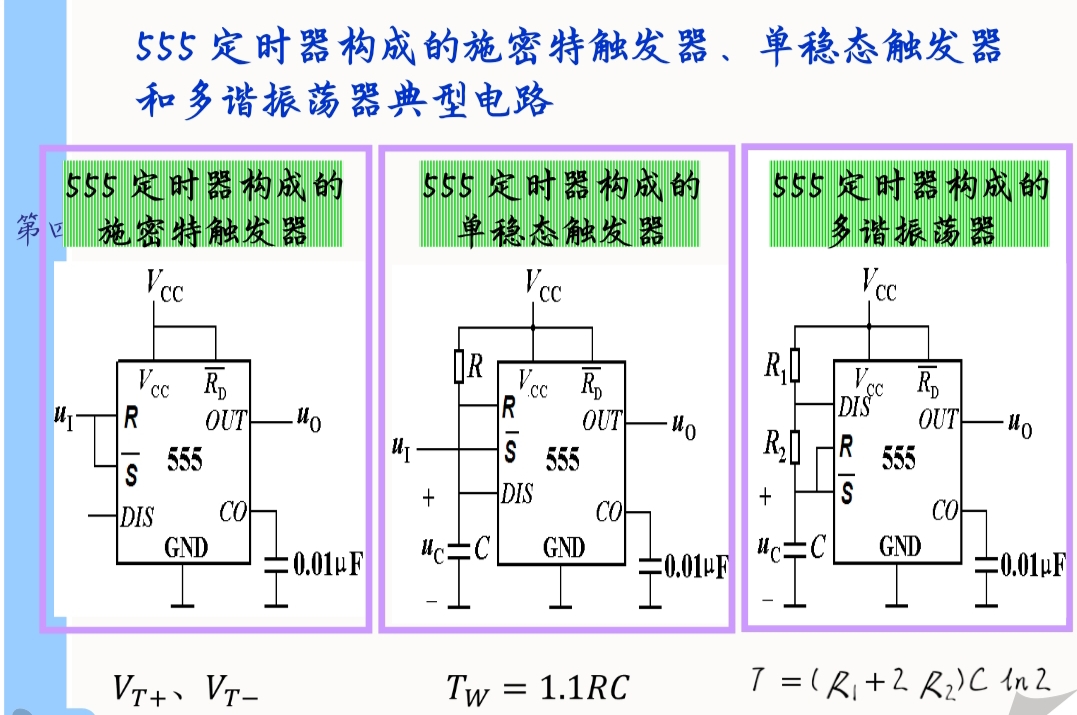

多谐振荡器没有稳态

单稳态触发器有一个稳态一个暂稳态

施密特触发器有两个稳态

重要的图片

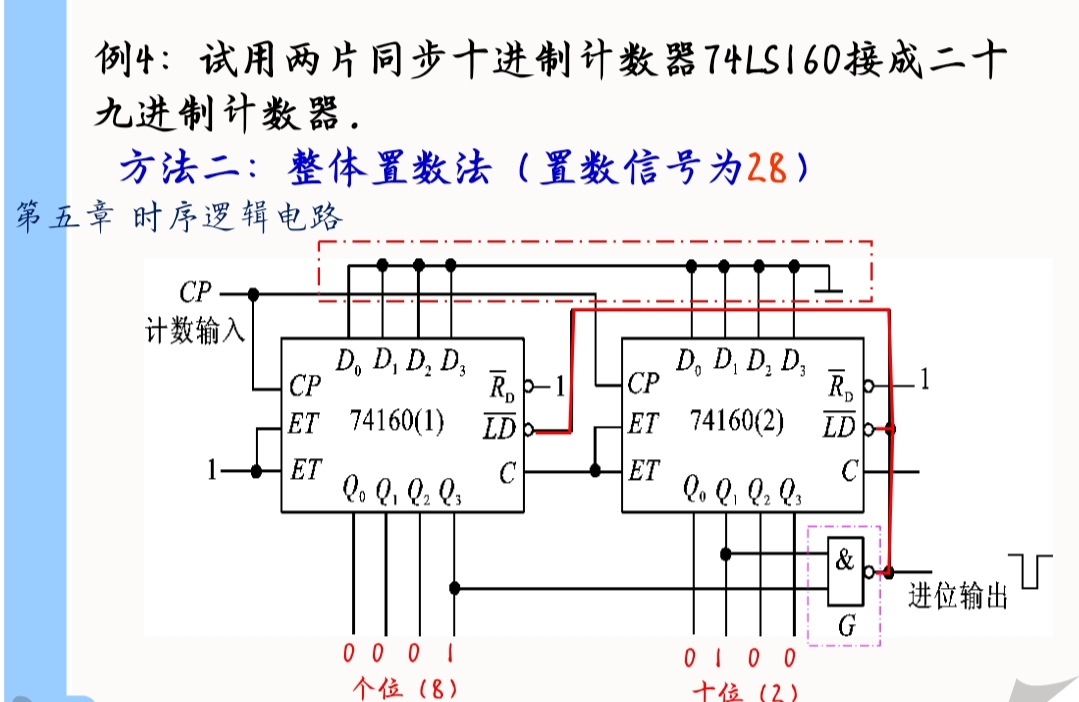

还有一个比较难的地方是多位片的n模计数器设计,比如这种

这内容稍微有点多,由于时间问题,不再展开说,若有相关问题,可以私信或评论

下面看一些填空题经常出的

存储器分为只读存储器(ROM) 随机存储器(RAM)

ram分为sram(静态随机 适合高速 小容量)和dram(动态随机 适合低速 大容量)

主要性能指标有 存储容量存储时间

rom组成:存储矩阵 地址译码器 输出缓冲器

sram:存储矩阵 地址译码器 读写控制电路

倒t型电路构成仅有r和2r两种阻值

a/d过程 采样 保持 量化 编码

直接adc:并联比较 计数 逐次渐近

速度快 精度低 抗干扰差

间接adc:双积分 V-F转换

速度慢 精度高 抗干扰能力强

四种阵列型PLD电路:PROM (可编程只读存储器 可编程或 固定与(地址译码器)) FPLA (现场可编程逻辑阵列 由可编程的与阵列 可编程的或阵列 输出缓冲器组成)PAL(可编程阵列逻辑 可编程与 固定或) GAL(通用阵列逻辑 )

可编程的输出逻辑宏单元(OLMC):五种工作模式,专用输入 专用组合输出 带反馈组合输出 时序逻辑组合输出 寄存器输出

最后

以上就是幸福蛋挞最近收集整理的关于[数字电子技术期末95+]考前突击总结一遍易错点、难点、重点、遗漏点的全部内容,更多相关[数字电子技术期末95+]考前突击总结一遍易错点、难点、重点、遗漏点内容请搜索靠谱客的其他文章。

![[数字电子技术期末95+]考前突击总结一遍易错点、难点、重点、遗漏点](https://www.shuijiaxian.com/files_image/reation/bcimg12.png)

发表评论 取消回复