一. 简介

欢迎关注 微信公众号 FPGA之旅 获取获取更多,最后项目工程将会在公众号进行开源。

回复 FPGA俄罗斯方块 获取项目工程

完整视频演示

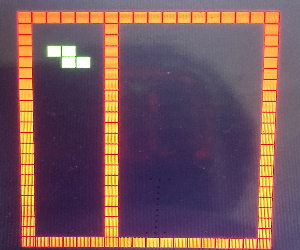

在前一篇文章中,简要的介绍了一下俄罗斯方块的一些基本要素,以及一些需要注意的点。在这篇文章中,主要实现两个功能 1. 绘制俄罗斯方块的边界,2.绘制出下一个方块的图像。 现在让我们开始吧。先看一下效果图。

二. 边界的绘制

在这里定义每一个方块的边长为10,边框的起始点相对于屏幕的偏移为(20,20)。

然后设置下一个方块的预览区域的宽度为5(5个方块大小,后面不再提示)。

这样整个俄罗斯方块的边界大小就确定下来了为宽18,高22。

localparam TerisW = 'd10;

localparam TerisH = 'd10;

localparam StartX = 'd20;

localparam StartY = 'd20;

1. 绘制最上面一行方块

- 首先判断y_addr的值是否到了设置的区域内,然后判断x_addr是否也到了设置的区域内。

- 为了每一个方块之间有一个间隙,这里还要计算x_addr对TerisW 取余,看是不是方块的左边界,如果是的话,就不显示。

- XNum为总宽度。然后最后一行的显示也是如此。

else if(y_addr >= StartY && y_addr < StartY + TerisH)

if(x_addr%TerisW == 'd0) //the aim is generate gap

WallReg <= 1'b0;

else if(x_addr > StartX && x_addr < StartX + XNum)

WallReg <= 1'b1;

else

WallReg <= 1'b0;

2. 绘制中间区域的三列方块

- 判断的方式,和上面一样,只是判断的条件发生了变化。

else if(y_addr > StartY + TerisH && y_addr < (StartY + YNum - TerisH))

if(y_addr%TerisH == 'd0) //生产间隙

WallReg <= 1'b0;

else if(x_addr > StartX + TerisW*4'd6 && x_addr < StartX + TerisW*4'd7) //中间那列方块

WallReg <= 1'b1;

else if(x_addr > StartX && x_addr < StartX + TerisW) //最左边那列方块

WallReg <= 1'b1;

else if(x_addr > (StartX + XNum -TerisW) && x_addr < StartX + XNum) //最右边那列方块

WallReg <= 1'b1;

else

WallReg <= 1'b0;

到这里边界的绘制就完成了,这还是非常容易的,就没有做过多的解释,有疑问可以留言哦。

三. 下一个图形生成与显示。

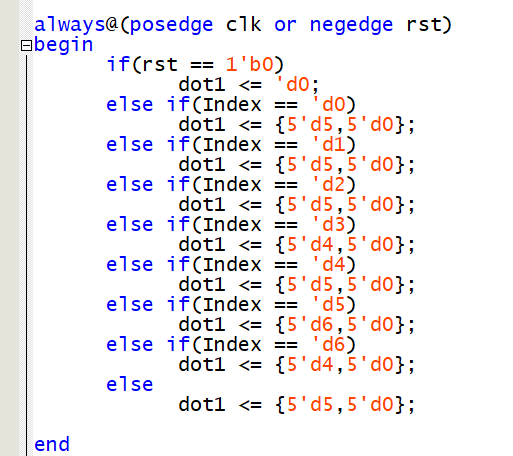

1. 图形的生成

图形的生成是随机的,这里需要用到之前贪吃蛇中随机数生成的模块,直接拿来用就可以了。

- 每一个图形都是由四个方块组成,所以可以直接用四个寄存器存储四个方块的位置即可。

- 这里使用10位的寄存器存储,高5位表示x的位置,低5位表示y的位置。

- 根据随机数生成的值,来判断当前选择那个图形,对照上一篇文章中的图片,一一对应赋值就可以了,如下图,以第一个点为例,这样我们下一个图形的数据就生成了。

2. 图形的显示

- 这里以一个点的显示为例,先判断x的位置,然后再判断y的位置。

- 这里还要结和起始偏移值。

- x的值是对应于游戏区域内的值,要想放在下一个图形显示区域内,需要调整XStart的值。

- XStart ,YStart 的值可以根据显示需要自行调整。

localparam XStart = 'd00;

localparam YStart = 'd50;

always@(posedge clk or negedge rst)

begin

if(rst == 1'b0)

NextDisplayEnReg1 <= 1'b0;

else if(x_addr > (TerisW*dot1[9:5] + XStart) && x_addr < (TerisW*dot1[9:5] + XStart + TerisW))

if(y_addr > (TerisH*dot1[4:0] + YStart) && y_addr < (TerisH*dot1[4:0] + YStart + TerisH))

NextDisplayEnReg1 <= 1'b1;

else

NextDisplayEnReg1 <= 1'b0;

else

NextDisplayEnReg1 <= 1'b0;

end

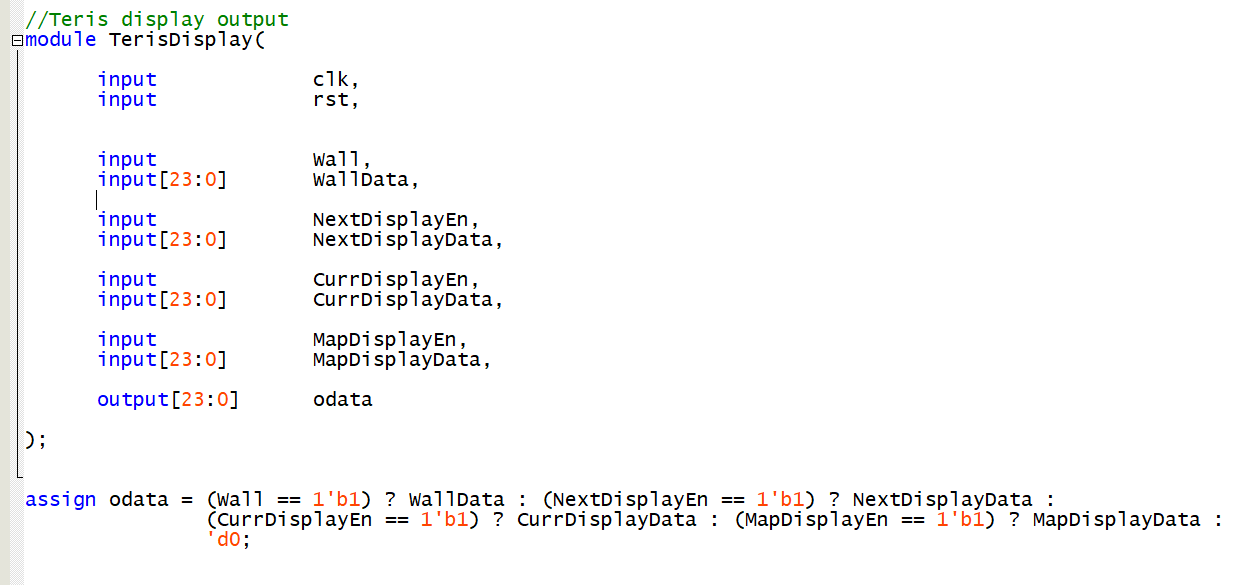

四. 游戏数据输出

游戏可以分为四部分数据显示,分别是边界,下一个图形,当前图形和以及静止的图形。这里通过一个模块来选择输出对应的数据

自此这部分的说明就完成了。

下一篇

我们将在下篇文章继续推进该项目的学习。

欢迎关注 微信公众号 FPGA之旅 获取获取更多,最后项目工程将会在公众号进行开源。

回复 FPGA俄罗斯方块 获取项目工程

最后

以上就是光亮鱼最近收集整理的关于FPGA实现俄罗斯方块(二)的全部内容,更多相关FPGA实现俄罗斯方块(二)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复