一、时序路径

在一个时序逻辑和组合逻辑组成的电路中对于时序路径一共有4种

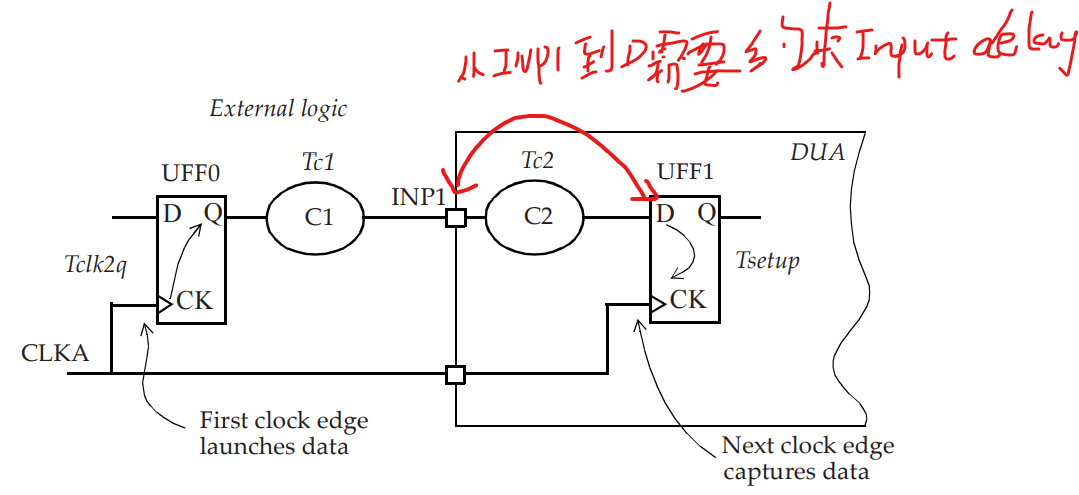

1.源D触发器CLK端 →目的D触发器的D端

2.输入input →目的D触发器的D端 这种情况需要设置 input delay

3.源D触发器CLK端 → 到输出OUTPUT端口 这种情况需要设置output delay

4.输入input→ 到输出output 这种情况需要设置 input 和output delay

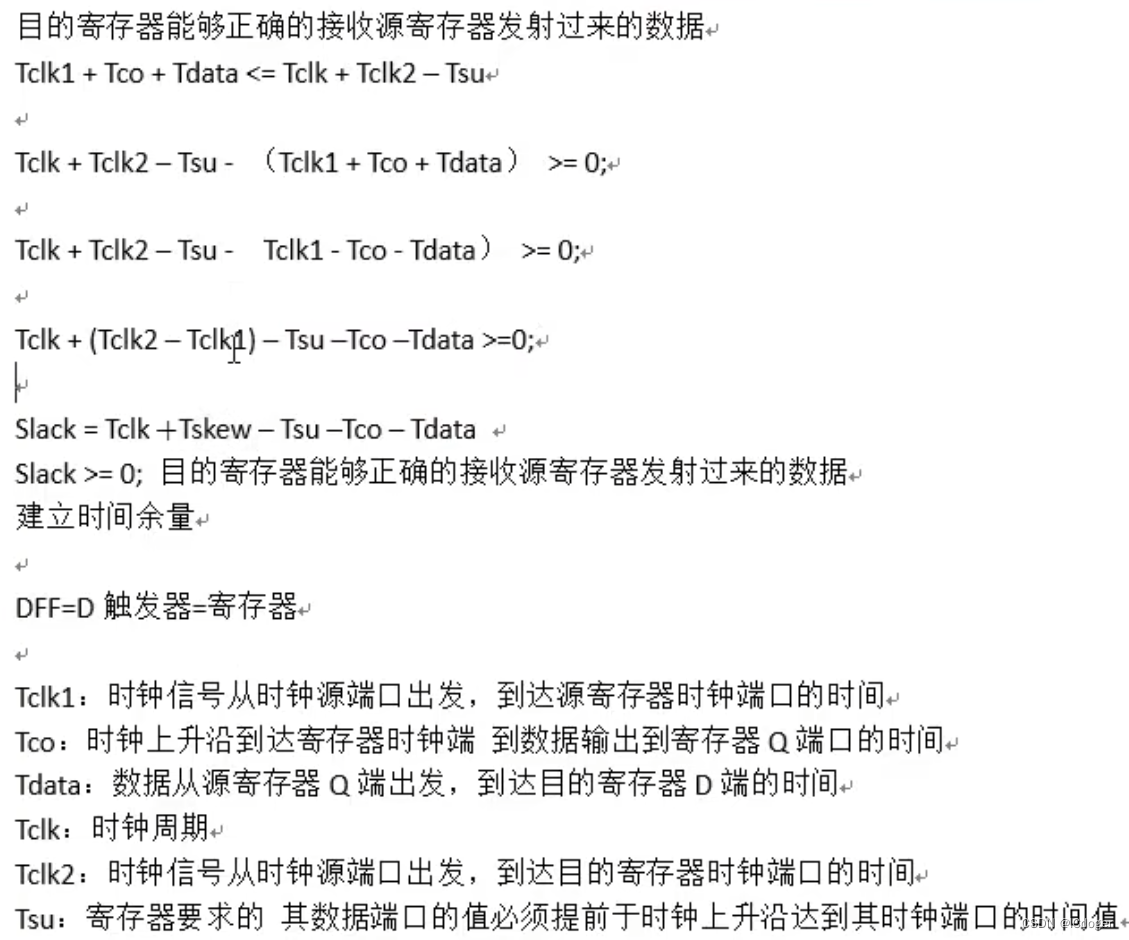

Tsetup是约束最大延迟即:最大延迟情况下数据也必须在下级触发器的Tsetup之前稳定;同理Thold就是指最小延迟约束:即电路延迟不能太小否则会在下一级的Thold时间段内发生变化

removal和recovery time都只是针对复位撤销,不是复位置位

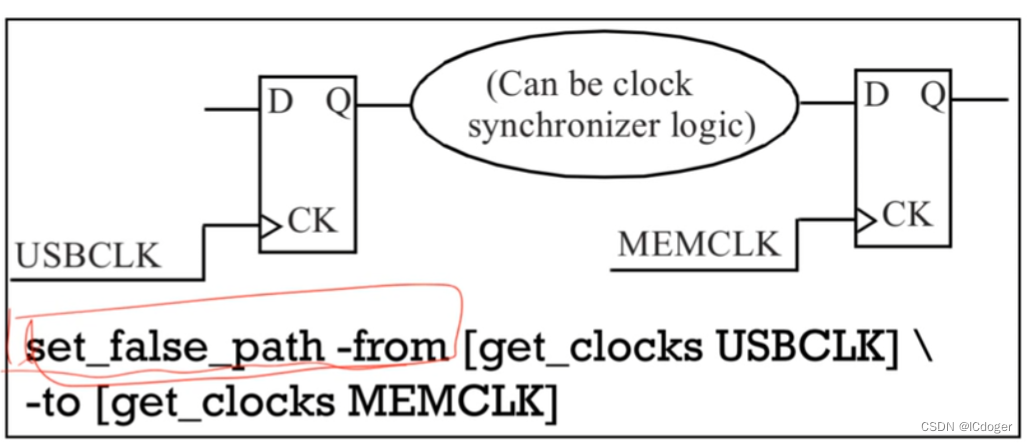

设置异步时钟域内不需要进行时序检测的路径

二、STA中的三种PVT类型

1.fast 2. slow 3. typ 其中对应ss表示最坏延迟即:Vmin + Tmax 状态 此时检查 Tsetup是否能够满足。 而对于ff表示速度最快即延迟最小:Vmax + Tmin 状态 此时检查 Thold 是否能够满足时序要求

三、STA中的sdc

1. 创建一个时钟约束create_clock -period 10 -waveform {5 10} [get_ports FCLK]

2. 设置时钟沿跳变延时set_clock_transition(即时钟从低电平跳到高电平的延迟反之亦然)其中set_clock_transition会应用与整个时钟网络,而set_input_transition只会作用与该port

3. 设置时钟的uncertainty

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

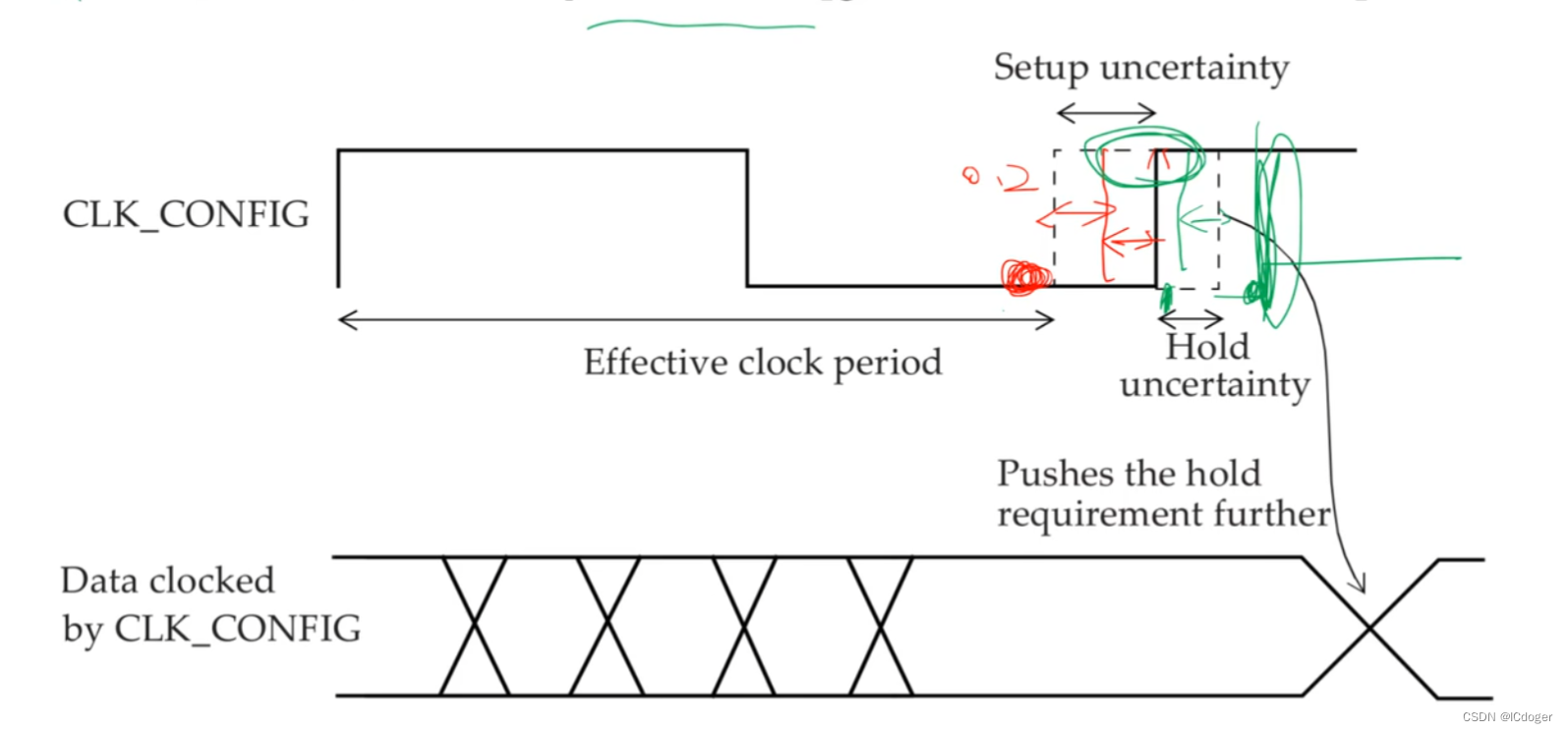

4. 一个电路中的clock latency包括 1.source latency 和 2. network latency 如下图所示:

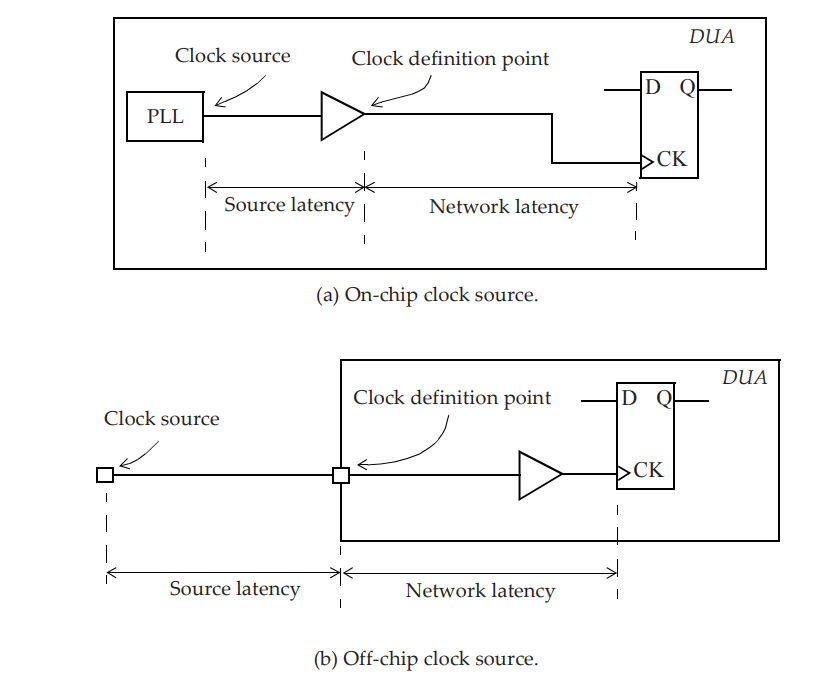

5. Generated Clocks

如果在电路中对于一个源时钟进行了改变如:分频之类的则需要在时序约束时采用以下 generated clock

create_generated_clock -name CLKPDIV2 -source UPLL0/CLKOUT

-divide_by 2 [get_pins UFF0/Q]若未定义可能进行STA时系统会判断这是两个时钟域,但是并不一定要定义generated_clock 例如,后级电路对时钟做了一些逻辑操作之后,时序完全乱掉了则可直接定义一个master clock

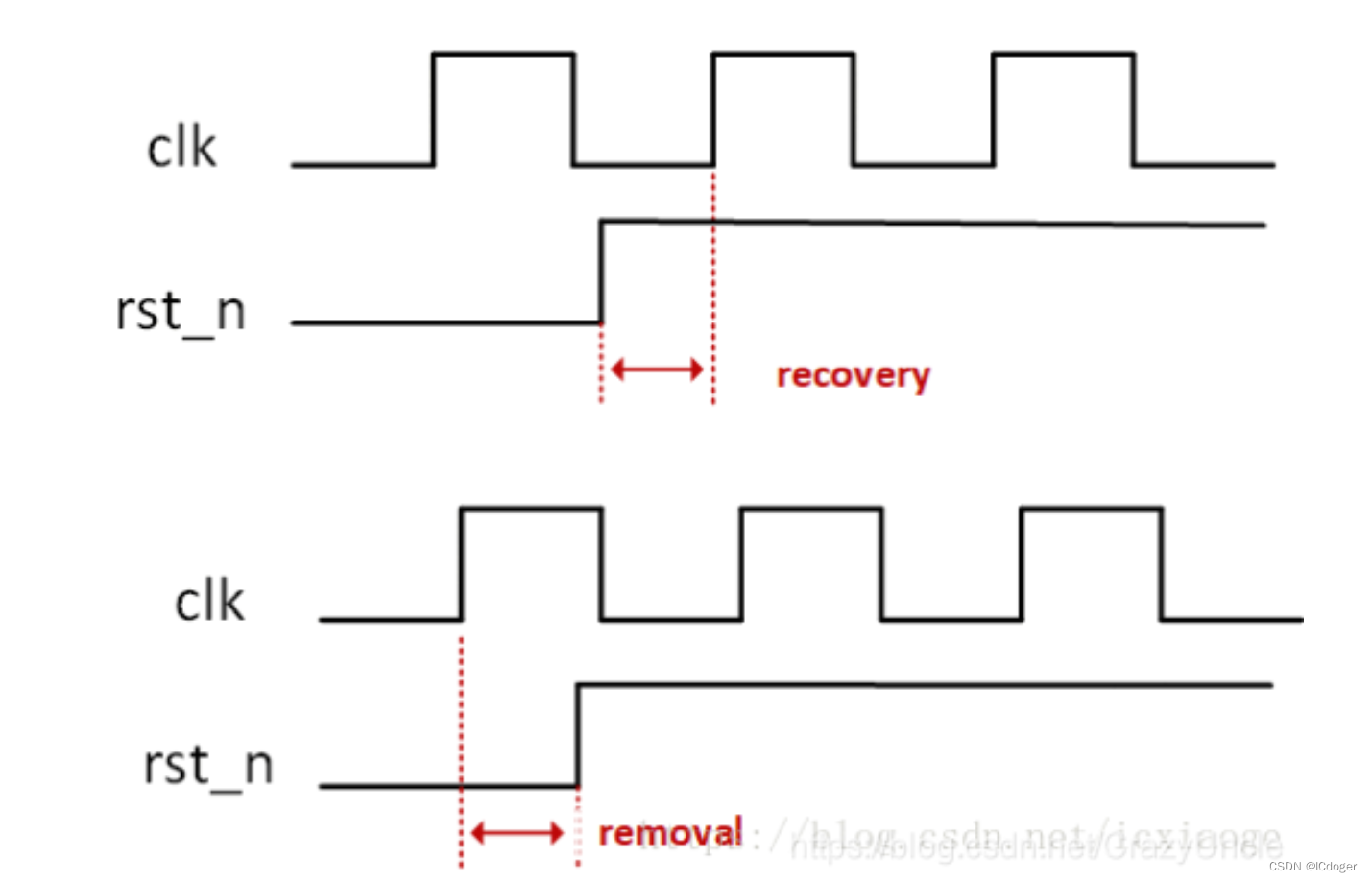

Asynchronous Checks

Recovery and Removal time 1.这两个类型的时序检查是针对异步复位或者异步置位等操作,用于判断异步引脚在下一个有源时钟边沿是否正确地返回到非活动状态。

1、recovery time:恢复时间

撤销复位时,恢复到非复位状态的电平必须在时钟有效沿来临之前的一段时间到来,才能保证时钟能有效恢复到非复位状态,此段时间为recovery time。类似于同步时钟的setup time。

2、removal time :去除时间

复位时,在时钟有效沿来临之后复位信号还需要保持的时间为去除时间removal time(去除时间)。类似同步时钟hold time

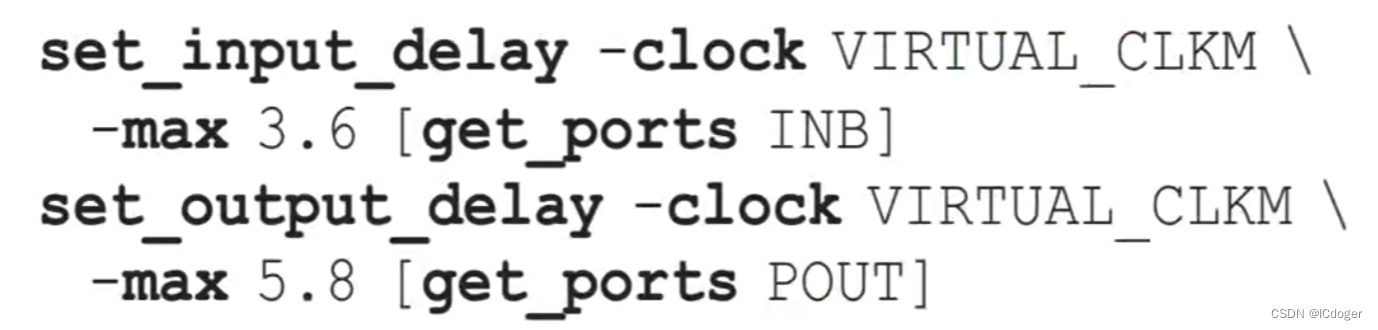

6. 约束input paths 和 output paths

约束代码如下:设置一个input delay 目的是为了满足UFF1的Tsetup

set Tclk2q 0.9

set Tc1 0.6

set_input_delay -clock CLKA -max [expr Tclk2q + Tc1]

[get_ports INP1

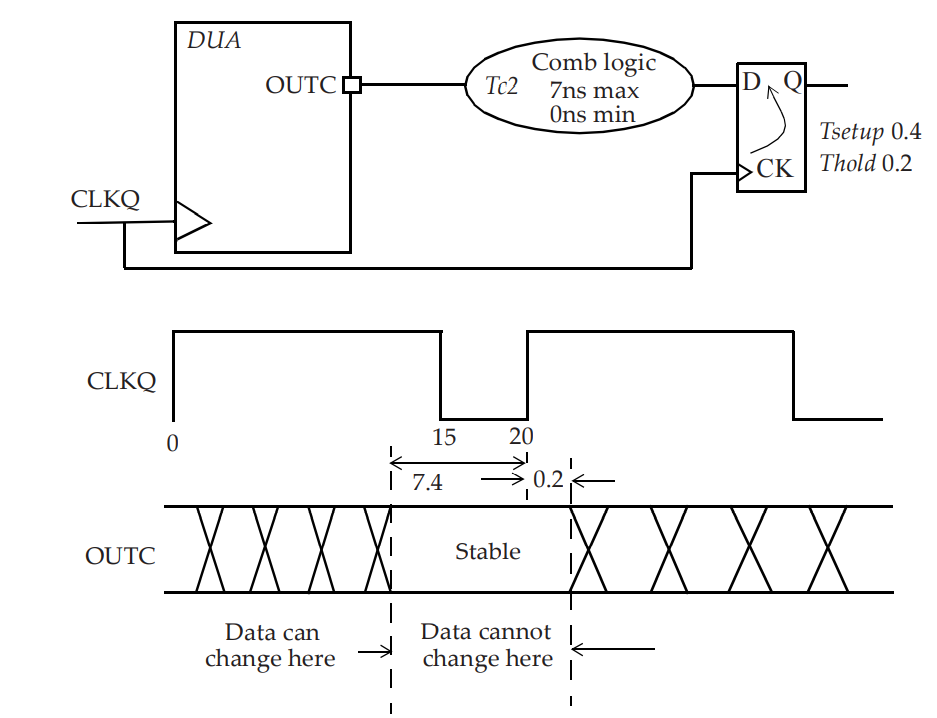

其中对于OUTC 的约束为:

create_clock -period 20 -waveform {0 15} [get_ports CLKQ]

set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC]

set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]7. 在STA中对于时钟组分类是按照endpoint 进行分类 即 同一endpoint 的时钟是同一个group

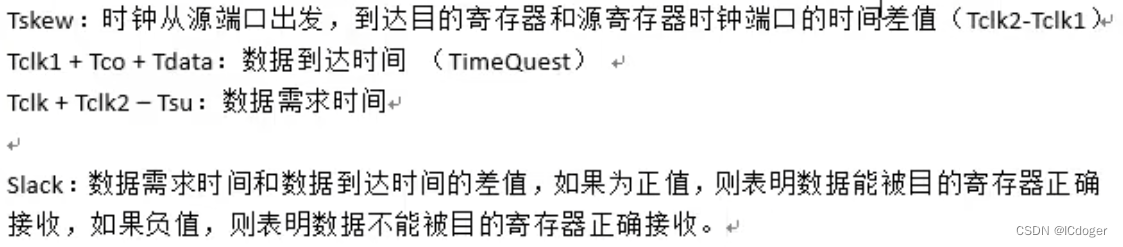

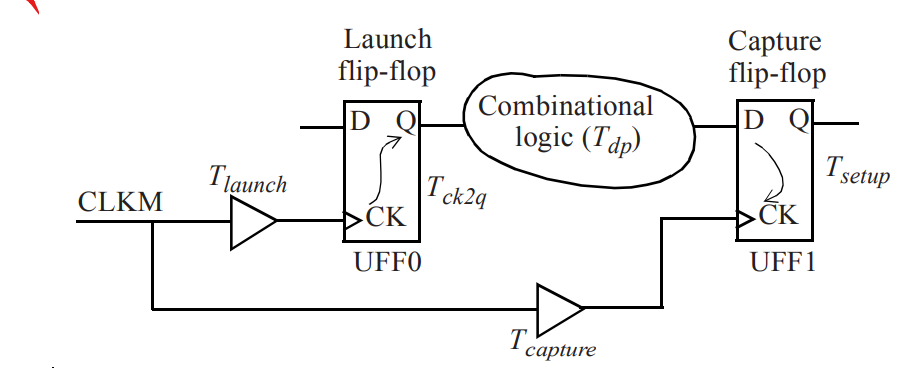

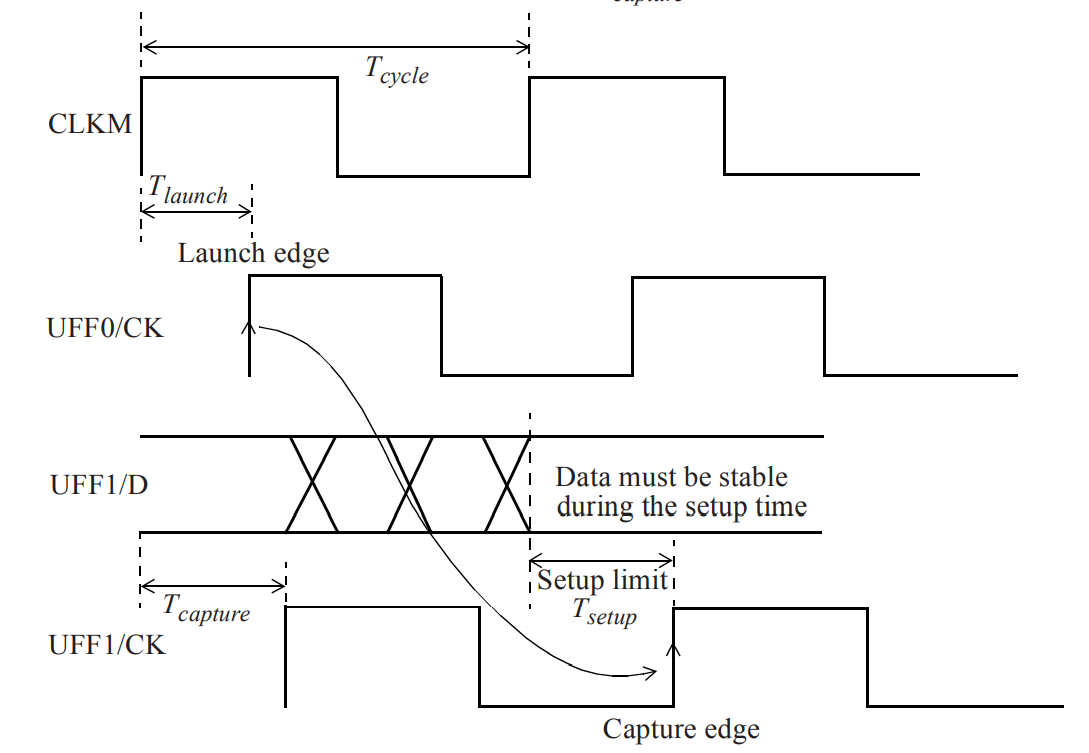

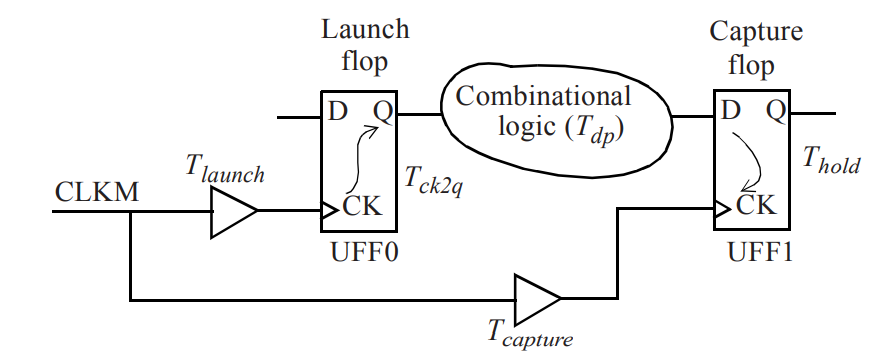

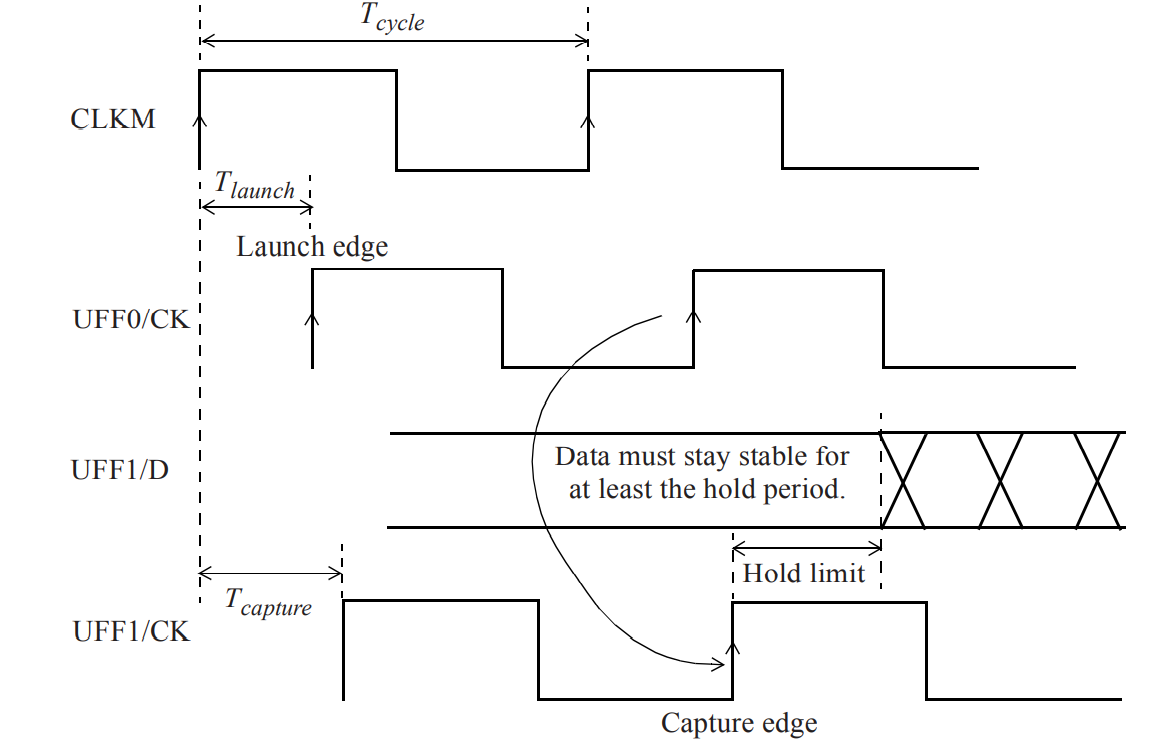

三、STA中的setup 时间和 hold 时间 check

Tlaunch + Tck2q + Tdp < Tcapture + Tcycle(时钟周期) - Tsetup

Tlaunch + Tck2q + Tdp > Tcapture + Thold

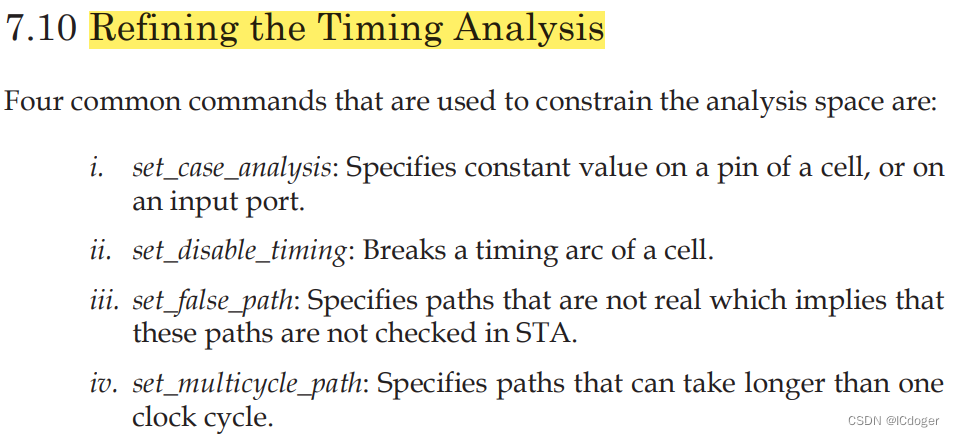

四、 Multicycle Paths

一般来说在电路A向电路B传递数据时都使用每半个周期传递一波数据,因为这样的话Thold时间比较宽裕,在电路设计时更方便,一般电路设计时Tsetup是比较好修改的

针对Multicycle Paths 以及 halfcycle Paths 、 falsecycle Paths 参考STA圣经 P261

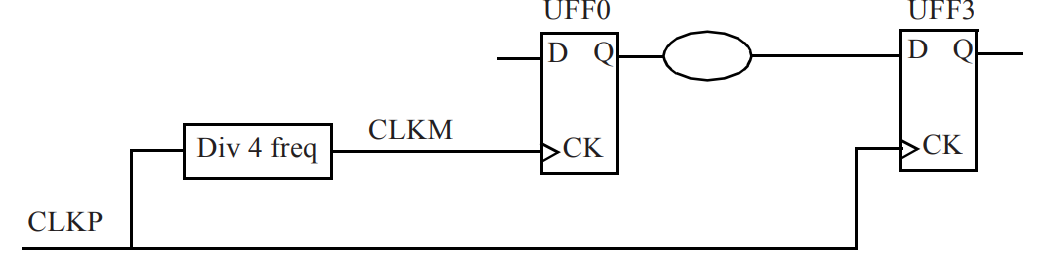

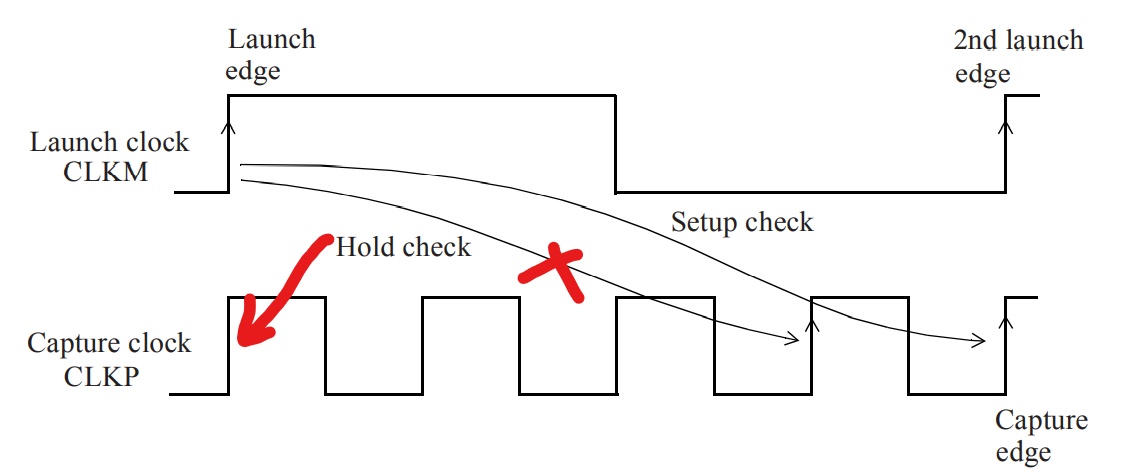

五、Timing across Clock Domains

1. Slow to Fast Domains

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]一般对于该电路记住这不是CDC电路,因为CLKP与CLKM具有固定的相位与频率关系,所以可以进行STA。针对该电路一般采用Multicycle Path 的方法 对n个周期之后的CLKP的上升沿进行Tsetup分析,同时也对n-1个周期之前的Thold 时间进行检查 具体约束例子如下:

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -end

set_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] -end

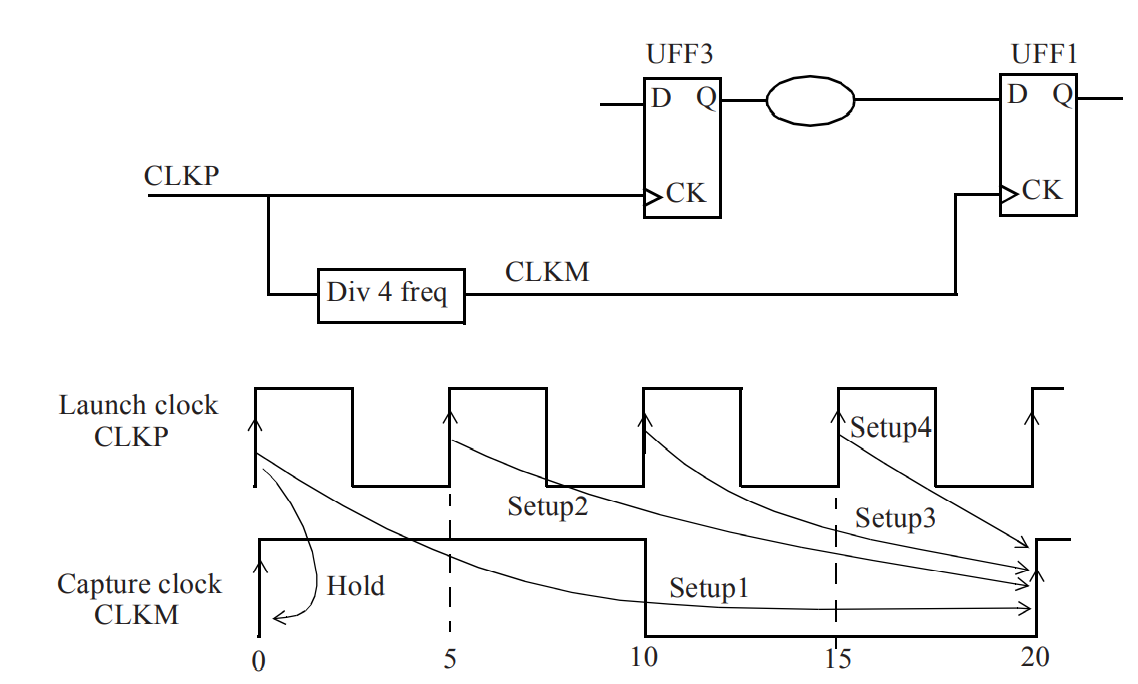

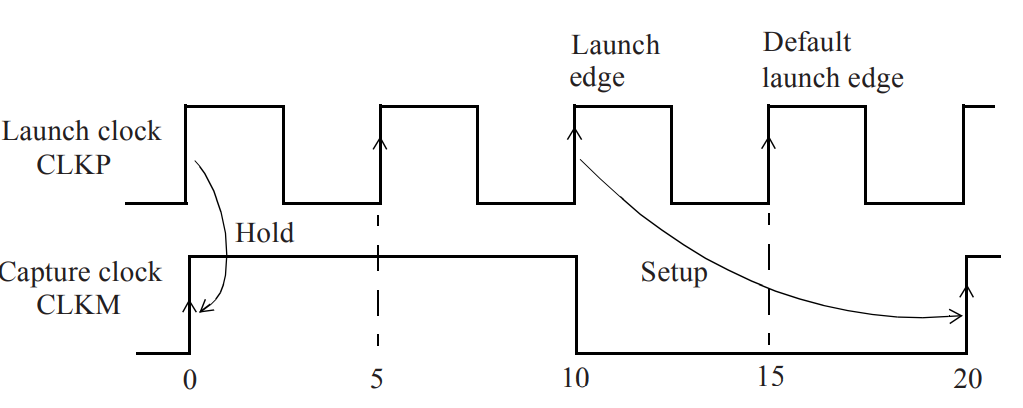

2. Fast to Slow Domains

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

针对此情况,若想时序宽松一点可以用Multicycle Path 将Tsetup check 时间前移几个CLKP的时钟

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start

五、On-Chip Variations

一般在进行时序分析时还需要考虑芯片上的噪声干扰,需要设置以下约束以人为的考虑OCV,将launch时序路径变得再慢一点,将capture路径时序变快一点。

set_timing_derate -early 0.8

set_timing_derate -late 1.1但是在某些情况下对于setup时序的检查已经是at the worst-case slow corner 时就不需要再使其变得更慢可以采用以下约束:

set_timing_derate -cell_delay -early 0.9

set_timing_derate -cell_delay -late 1.0

而对于Hold时序分析则与Setup相反这里就不再细说

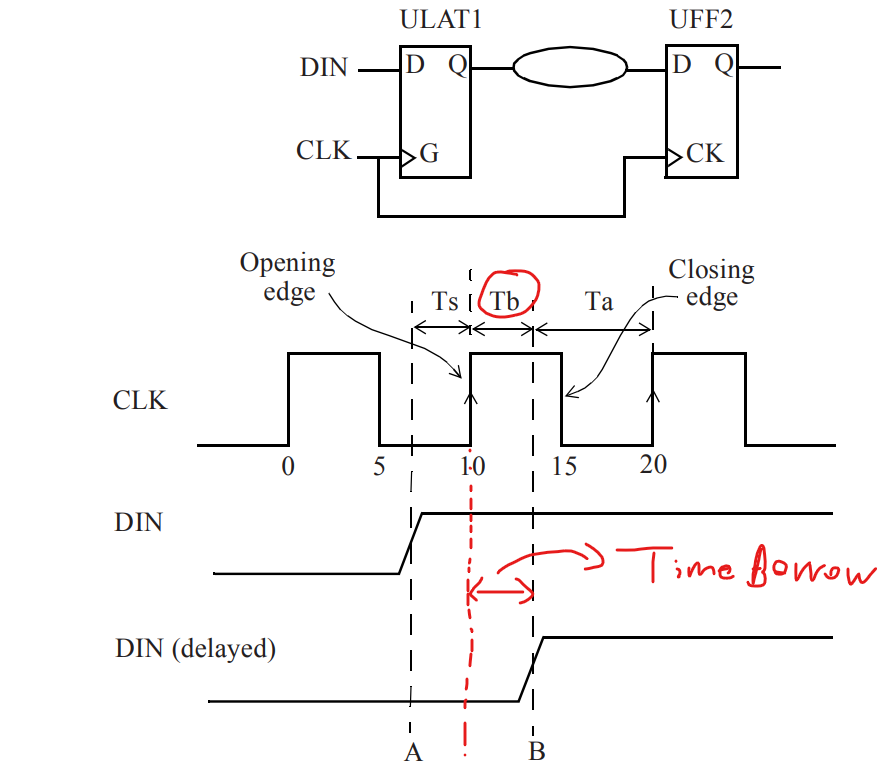

六、Latch 的STA

1. Timing Borrowing

在对latch进行STA时会对其进行opening edge 和 closing edge 的定义。前者指Q端在这个时钟沿变得透明可以得到D端数据,后者则是指Q端数据不再随D端改变。针对这两种状态就有了Timing Borrowing 的概念 即:当有效数据来临时可以在opening edge 延迟一段时间到来 ,即向下一个时钟周期borrow time 具体模型参考如下:

具体参考STA圣经P381

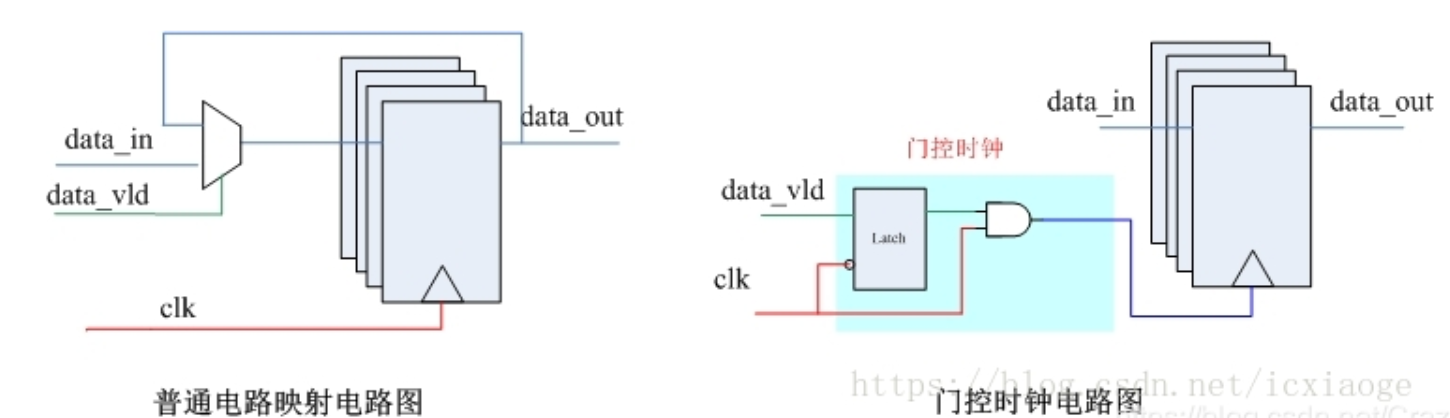

2. 可生产clock gating 的Verilog 描述

//可生成门控时钟

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

data_out <= 8'b0;

else if(en)

data_out <= data_in;

end3. 不可产生clock gating 的Verilog 描述

//无法生成门控时钟

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

data_out <= 8'b0;

else if(en)

data_out <= data_in;

else

//data_out <= 8'b0; 这是错误的,没有en时应该保持,功能错误

data_out <= data_out;

end上面两段代码的综合图:

clock gating check 一个很关键的设计 STA圣经P400开始

对于STA工具其会自动检测那些路径是门控时钟的路径,判断是否是门口时钟是根据时钟经过一些简单的逻辑门之后是接入的触发器的D端还是CLK端

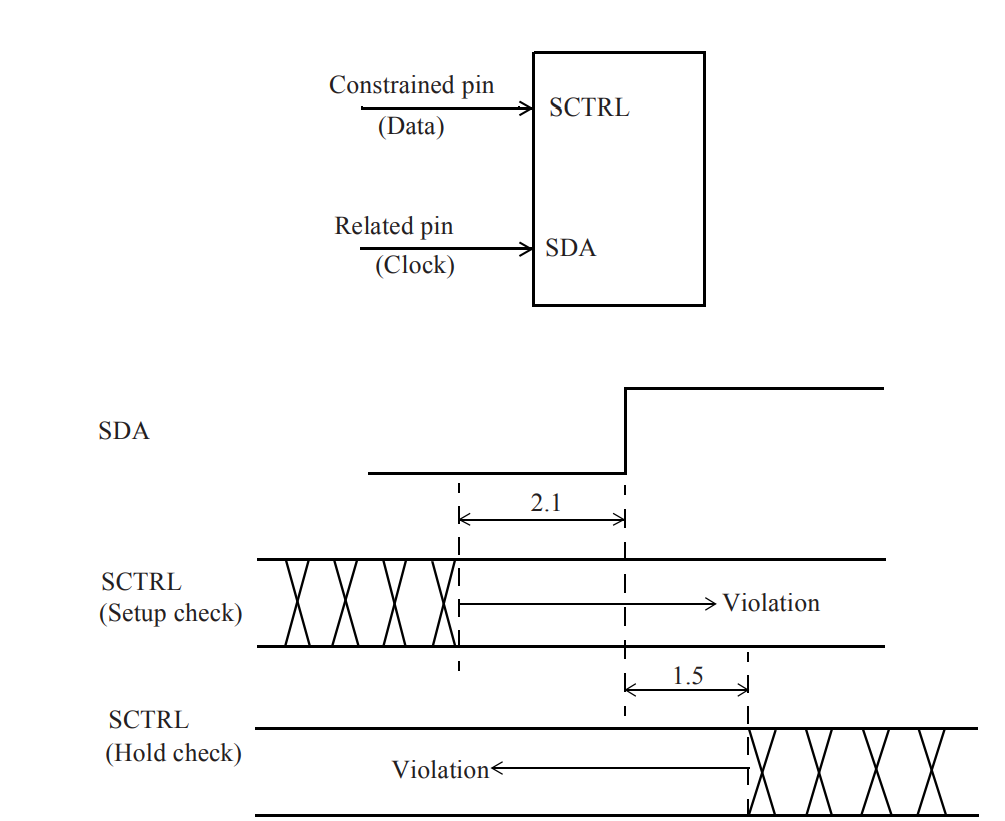

七、data to data check

对于data to data check 该时序检查中的Tsetup检查为同一时钟沿

约束如下:

set_data_check -from SDA -to SCTRL -setup 2.1

set_data_check -from SDA -to SCTRL -hold 1.5最后

以上就是开放外套最近收集整理的关于STA学习笔记的全部内容,更多相关STA学习笔记内容请搜索靠谱客的其他文章。

发表评论 取消回复