双稳态电路:具有存储或记忆1位二进制数据的功能

锁存器(latch):对脉冲电平敏感的存储单元电路。它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。

数据有效 滞后于 时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器 。

- 锁存器容易产生毛刺

- 锁存器在ASIC设计中应该说比FF要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和FF来组成锁存器,这样就浪费了资源

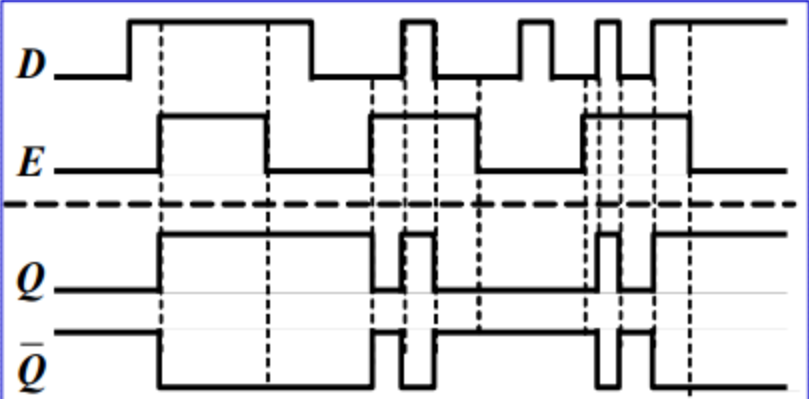

下面是D锁存器的波形图。

触发器(Flip-Flop,简写为 FF):是一种对脉冲边沿敏感的存储电路,其状态只在时钟脉冲的上升沿或下降沿的瞬间改变 。

时钟有效 迟后于 数据有效,这意味着数据信号先建立,时钟信号后建立,在CP有效沿时刻打入到寄存器 。

最后

以上就是落寞过客最近收集整理的关于锁存器和触发器的全部内容,更多相关锁存器和触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复