最大采样率

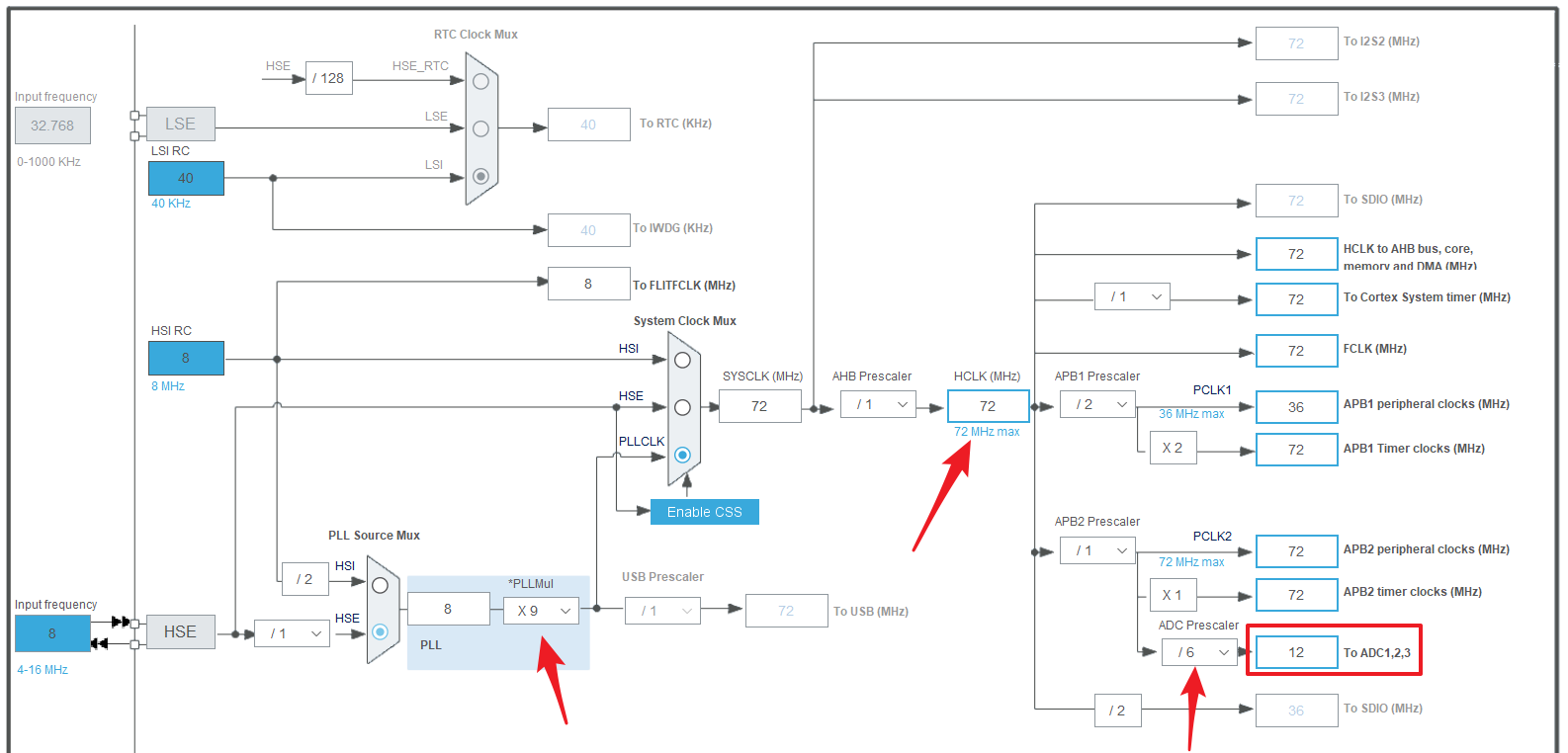

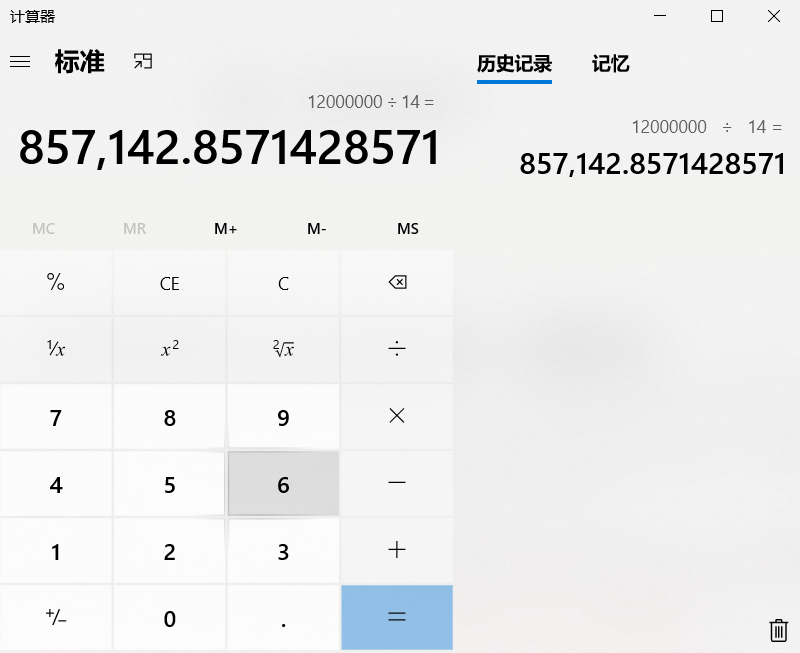

如果设置PLCK2为6分频,那么ADCCLK为:72M/6=12MHz。在外部晶振为8MHZ的情况下,这是F103系列ADC得到的最大时钟频率。

最小采样周期为1.5个周期+12.5周期=14周期。

那么最大采样频率为:12MHZ/14周期=851.142KHZ≈851KHZ

也就是1s可以采样851K个数据,对于STM32F1这个采样率已经是最大能力了。

最小采样率

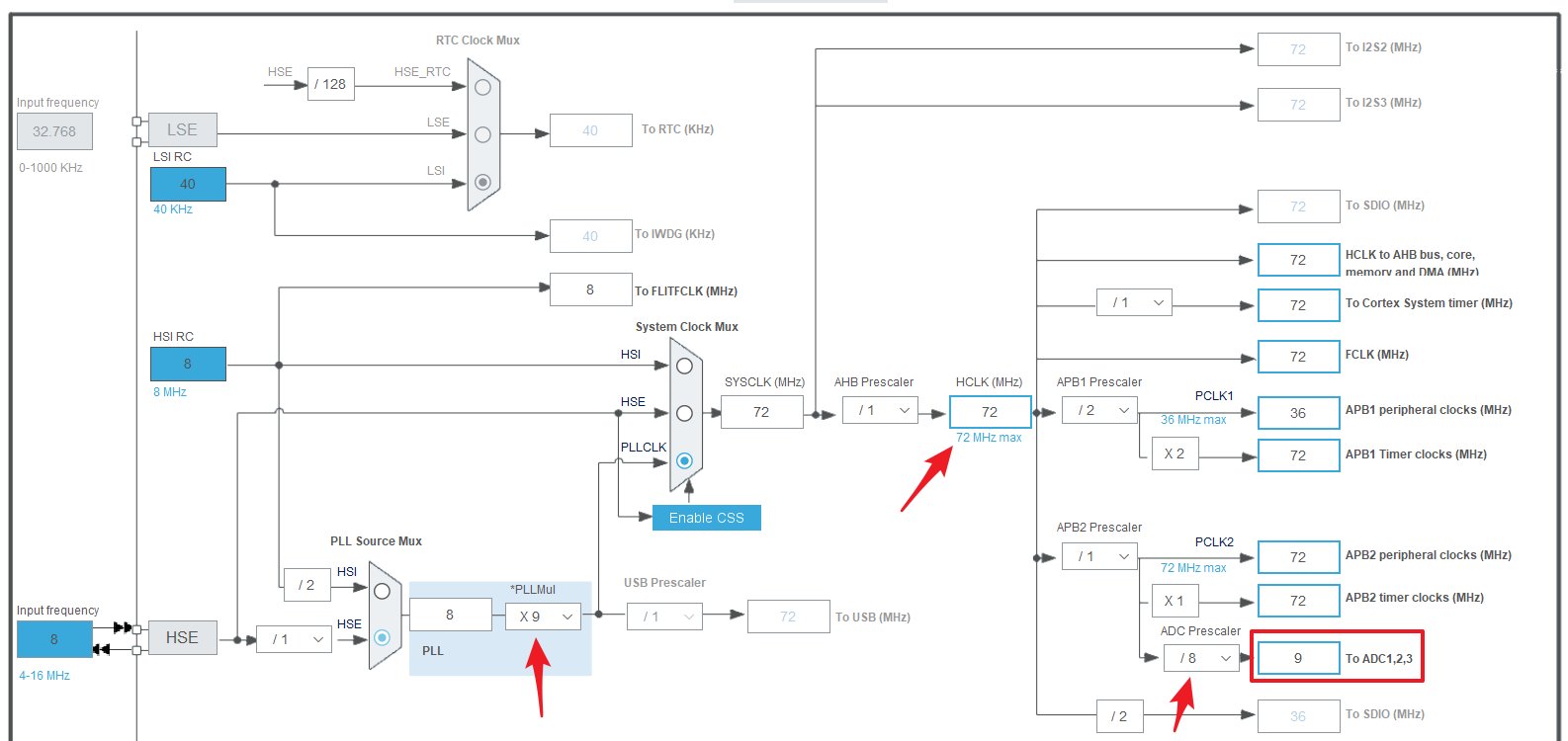

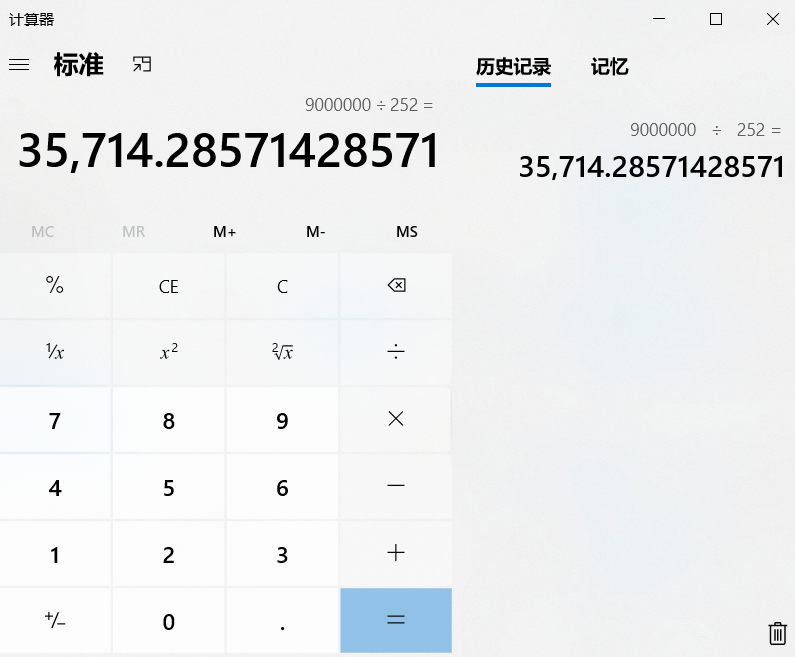

如果设置PLCK2为8分频,那么ADCCLK为:72M/8=9MHz。在外部晶振为8MHZ的情况下,这是F103系列ADC得到的最小时钟频率。

最大采样周期为239.5个周期+12.5周期=252周期。

那么最大采样频率为:9MHZ/252周期=35.714KHZ≈35.7KHZ

也就是1s可以采样35.7K个数据,对于STM32F1这个采样率时其最小的采样能力。

最后

以上就是无语香菇最近收集整理的关于STM32 ADC采样频率的理解最大采样率最小采样率的全部内容,更多相关STM32内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复