8.1 概述

文章目录

- 8.1 概述

- 8.2 Processor Subsystems

- 一个双核A72

- 三个双核R5F

- 一个C7

- 两个C66

- 8.3 Accelerators and Coprocessors

- PRU 内核

- GPU

- VPAC 视觉预处理加速器

- 深度和运动感知加速器

- 解码器

- 编码器

- 8.4 Other Subsystems

- 多核共享内存控制器

- 导航器子系统

- DMA 控制器

- 外设

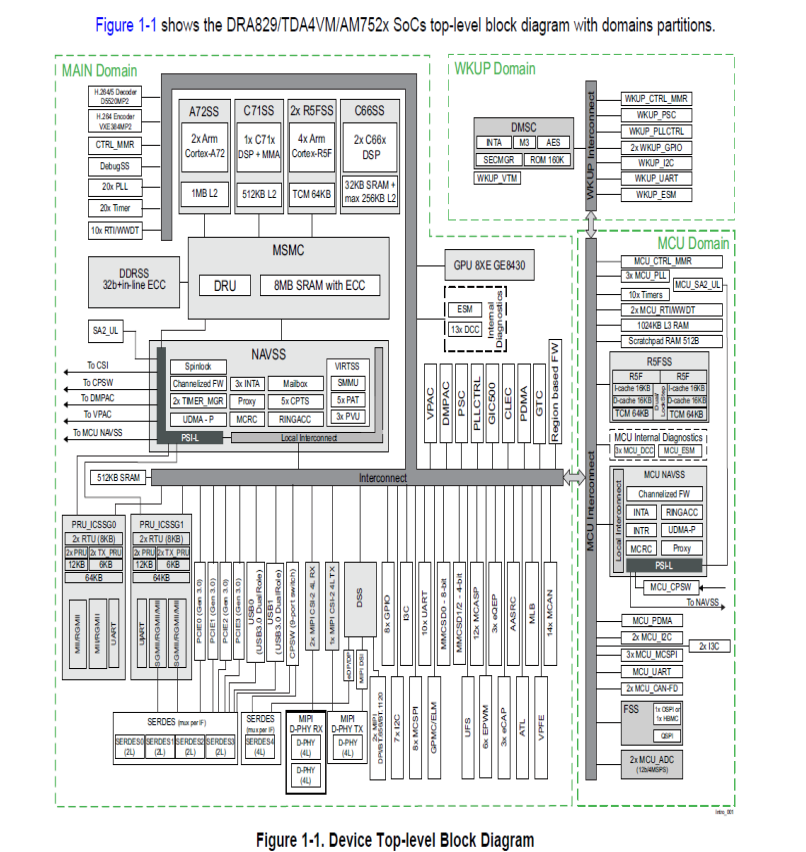

- 逻辑框图

8.2 Processor Subsystems

一个双核A72

该设备实现了一个双核 Arm® Cortex®-A72 MPU,它与其他模块一起集成在计算集群中。 Cortex-A72 内核是通用处理器,可用于运行客户应用程序。 A72SS 围绕 Arm Cortex-A72 MPCore(A72 集群)构建,由 Arm 提供并由 TI 配置。它基于对称多处理器 (SMP) 架构,因此可提供高性能和最佳电源管理和调试功能。 A72 处理器是一个多问题无序超标量执行引擎,具有集成的 L1 指令和数据缓存,兼容 Armv8-A 架构。 Armv8-A 架构带来了许多新特性。其中包括 64 位数据处理、扩展虚拟寻址和 64 位通用寄存器。

三个双核R5F

MCU_ARMSS 是针对拆分/锁定操作配置的 Arm® Cortex®-R5F 处理器的双核实现。它还包括随附存储器(L1 缓存和紧耦合存储器)、标准 Arm® CoreSight™ 调试和跟踪架构、集成向量中断管理器 (VIM)、ECC 聚合器以及用于协议转换和地址转换的各种包装器,以便轻松集成到SoC。

一个C7

TMS320C71x 是下一代定点和浮点 DSP 平台。 C71x DSP 是德州仪器 (TI) DSP 系列中的新内核。 C71x DSP 支持矢量信号处理,与 C6x DSP 系列相比,在广泛的通用信号处理任务中显着提升了 DSP 处理能力。 此外,C71x 还提供了多项专用功能,可将目标功能加速 30 倍以上。 除了扩展向量处理能力外,新的 C71x 内核还融合了先进技术来提高控制代码效率和编程的简易性,例如分支预测、受保护的流水线、精确的异常和虚拟内存管理

两个C66

C66x 子系统基于 TI 的标准 TMS320C66x DSP CorePac 模块。它包括子系统逻辑,以简化 C66x CorePac 与 SoC 的集成,同时最大限度地重复使用以前设备的软件。 C66x DSP 通过增强功能和新功能扩展了 C64x+ 和 C674x DSP 的性能。许多新功能旨在提高矢量处理的性能。 C64x+ 和 C674x DSP 支持 16 位数据的 2 路 SIMD 操作和 8 位数据的 4 路 SIMD 操作。在 C66x DSP 上,通过扩展 SIMD 指令的宽度来提高矢量处理能力。 C66x DSP 可以执行对 128 位向量进行操作的指令。例如,QMPY32 指令能够在每个包含四个 32 位数据的两个向量之间执行元素到元素的乘法。 C66x DSP 还支持 SIMD 进行浮点运算。改进的向量处理能力(每条指令可以并行处理多个数据)与 C6000 架构的自然指令级并行性(例如,每个周期最多执行 8 条指令)相结合,产生了非常高的并行性,可通过DSP 程序员通过使用 TI 优化的 C/C++ 编译器

8.3 Accelerators and Coprocessors

PRU 内核

8.3.1 PRU_ICSSG

PRU 内核的可编程特性以及它们对引脚、事件和所有设备资源的访问,为实现快速实时响应、专用数据处理操作、自定义外设接口以及从其他处理器内核卸载任务提供了灵活性。装置。

8.3.1.1 PRU_ICSSG PRU 内核

PRU 内核使用小型确定性指令集进行编程。每个PRU可以独立运行,也可以相互协同工作,也可以与设备级主机CPU协同工作。处理器之间的这种交互由加载到 PRU 中的固件的性质决定

指令存储器。

8.3.1.2 PRU_ICSSG 宽边加速器

PRU_ICSSG 支持宽边接口,该接口使用 XFR(XIN、XOUT 或 XCHG)指令将 PRUn、RTU_PRUn 或 TX_PRUn(其中 n = 0 或 1)寄存器的内容传送到加速器或从加速器传出。该接口最多支持 31在单个指令中传输的寄存器(R0-R30,或 124 字节)。本节详细介绍了通过宽边接口可用于 PRUn 和/或 RTU_PRUn 和 TX_PRUn 的各种加速器。

8.3.1.3 PRU_ICSSG 本地INTC

PRU_ICSSG 中断控制器 (INTC) 将来自设备不同部分的中断(映射到 PRU_ICSSGn,其中 n = 0 或 1)映射到一组减少的 PRU_ICSSG 中断通道。

8.3.1.4 PRU_ICSSG UART 模块

PRU_ICSSG UART0 外设基于行业标准 TL16C550 异步通信元件,而后者又是 TL16C450 的功能升级。

8.3.1.5 PRU_ICSSG ECAP 模块

8.3.1.6 PRU_ICSSG PWM 模块

8.3.1.7 PRU_ICSSG MII_G_RT 模块

8.3.1.8 PRU_ICSSG MII MDIO 模块

8.3.1.9 PRU_ICSSG IEP

GPU

8.3.2 图形处理器

图形处理单元 (GPU) 可加速 3 维 (3D) 和 2 维 (2D) 图形和计算应用程序。

GPU 模块是一种可扩展的架构,可以高效地同时处理多个不同的工作负载:

- 3D 图形工作负载,涉及用于渲染 3D 场景的顶点数据和像素数据处理。

- 2D 图形工作负载,涉及用于渲染 2D 对象的像素数据处理。

- 计算应用程序工作负载,涉及通用数据处理。

VPAC 视觉预处理加速器

8.3.3 VPAC

视觉预处理加速器 (VPAC) 是一组常见的视觉基元函数,执行内存到内存 (M2M) 像素数据处理任务,例如:颜色处理和增强、噪声过滤、宽动态范围 (WDR) 处理 ,镜头失真校正,用于去扭曲的像素重新映射,即时比例生成,即时金字塔生成。 VPAC 从主 SoC 处理器(ARM、DSP 等)卸载这些常见任务,因此可以将这些 CPU 用于差异化的高级算法。 VPAC 旨在通过在时分复用模式下工作来支持多台摄像机。 VPAC 用作视觉处理的前端,并为 SoC 中的其他视觉加速器或处理器内核的进一步处理准备帧/比例

深度和运动感知加速器

8.3.4 DMPAC

深度和运动感知加速器 (DMPAC) 是一种高能效硬件加速器,可计算来自相机输入的密集立体深度图(深度)和密集光流矢量(运动)。 基于图像/视频传感器的环境感知(也称为场景理解)是汽车、工业和消费电子领域许多新兴应用的核心。 通常,这涉及通过分析一个或多个相关的输入视频流来检测场景中的所有对象以及它们相对于观察者或汽车的 3D 位置和运动。 各种计算机视觉算法用于实现这些任务。

从图像中获取 3D 深度的一种非常可靠的方法是在立体设置中使用两个摄像头——两个具有已知相对位置和摄像头参数的摄像头。分析从两个不同的相机姿势/视角捕获的同一场景的两个图像,以找出图像中每个像素位置之间的差异。这称为立体视差图。每个像素的视差值可用于通过三角测量获得它们所属的对象/空间的 3D 位置。

另一方面,通过分析在两个不同时间实例(即视频中的两个时间帧)捕获的来自单个相机的两个图像,可以确定过去帧中的每个像素在未来帧中移动到的位置。这被称为光流矢量。每个像素位置的流向量可用于获得场景的 3D 结构、识别运动物体并确定它们的相对速度和运动方向。 DMPAC 专用于上述图像处理任务。立体和光流处理分为两个顶级子块:密集光流 (DOF) 引擎和立体视差引擎 (SDE)。 DOF 和 SDE 块共享公共共享本地存储器、DMA、外部消息传递和控制基础结构。

解码器

8.3.5 D5520MP2

DECODER 模块是 D5520MP2 双核 PowerVR® VPU(视频处理器单元)。

D5520MP2 能够支持:

• 1x 4kp60 解码或

• 2x 4kp30 解码或

• 4x 1080p60 解码或

• 8x 1080p30 解码

编码器

8.3.6 VXE384MP2

ENCODER 模块是 VXE384MP2 核心 PowerVR® VPU(视频处理器单元)。

VXE384MP2 能够支持:

• 1x 1080p60 视频流编码或

• 2x 或 3x 1080p30 视频流编码

8.4 Other Subsystems

多核共享内存控制器

8.4.1 MSMC

多核共享内存控制器 (MSMC) 构成了计算集群 (COMPUTE_CLUSTER0) 的核心,提供进出所有连接处理元件和系统其余部分的高带宽资源访问。

导航器子系统

8.4.2 导航系统

8.4.2.1 NAVSS0

主 SoC 导航器子系统 (NAVSS0) 由 DMA/队列管理组件 - UDMA 和环加速器 (UDMASS)、外设(模块子系统 [MODSS])、虚拟化转换 (VirtSS) 和北桥 (NBSS) 组成。

8.4.2.2 MCU_NAVSS

MCU Navigator Subsystem (MCU NAVSS) 具有主 NAVSS 的模块子集,并在 MCU 域中实例化。

MCU 导航器子系统由 DMA/队列管理组件 - UDMA 和环加速器 (UDMASS) 以及外设(模块子系统 [MODSS])组成。

DMA 控制器

8.4.3 PDMA 控制器

外设 DMA 是一种简单的 DMA,其架构专门用于满足外设的数据传输需求,这些外设使用通过标准非相干总线结构访问的存储器映射寄存器执行数据传输。 PDMA 模块旨在靠近一个或多个需要外部 DMA 进行数据移动的外设,其架构旨在通过使用 VBUSP 接口和仅支持静态配置的传输请求 (TR) 操作来降低成本

外设

8.4.4 外设

8.4.4.1 ADC

模数转换器 (ADC) 模块包含一个 12 位 ADC,可以多路复用到 8 个模拟输入(通道)中的任何一个。

8.4.4.2 ATL

HD Radio™ 应用程序使用音频跟踪逻辑 (ATL) 将数字音频输出与基带时钟同步。这个相同的 IP 也可以一般用于跟踪两个参考信号(例如帧同步)之间的错误,并生成一个调制时钟输出(使用软件控制的周期窃取),平均到某个所需的频率。此过程可用作异步采样率转换算法的硬件辅助。

8.4.4.3 AASRC

Audio Asynchronous Sample Rate Converter (AASRC) 模块从一个时钟区采样并移动到另一个时钟区,同时保持高信噪比,以确保输出质量足以满足各种高端算法的要求。

8.4.4.4 CSI

8.4.4.4.1 相机流接口接收器(CSI_RX_IF)和 MIPI DPHY 接收器(DPHY_RX)

CSI_RX_IF 模块的集成允许设备将来自多个摄像头的视频输入流式传输到图像处理加速器 (VPAC) 或内部存储器。视频输入也可以通过发送器 CSI (CSI_TX_IF) 重新发送以用于调试和测试目的。

8.4.4.4.2 摄像机流接口发送器(CSI_TX_IF)

CSI_TX_IF 模块的集成允许设备从内存中输出视频数据,或从 CSI 接收器重新传输作为用于诊断、调试和测试目的的可选环回输出。

8.4.4.5 CPSW2G

双端口千兆以太网 MAC (MCU_CPSW0) 子系统为设备提供以太网数据包通信,其配置方式与以太网交换机类似。 MCU_CPSW0 具有精简千兆媒体独立接口 (RGMII)、精简媒体独立接口 (RMII) 和用于物理层设备 (PHY) 管理的管理数据输入/输出 (MDIO) 接口。

有关更多信息,请参阅设备 TRM 的外设章节中的千兆以太网交换机 (CPSW0) 部分。

8.4.4.6 CPSW9G

9 端口千兆以太网交换机 (CPSW0) 子系统为设备提供以太网数据包通信,并可配置为以太网交换机。 CPSW0 具有串行千兆媒体独立接口 (SGMII)、精简千兆媒体独立接口 (RGMII)、精简媒体独立接口 (RMII) 和用于物理层设备 (PHY) 管理的管理数据输入/输出 (MDIO) 接口。

8.4.4.7 双时钟比较器

双时钟比较器 (DCC) 用于确定应用程序时间执行期间时钟信号的准确性。具体而言,DCC 旨在检测与预期时钟频率的漂移。可以根据每个应用的计算对所需的精度进行编程。 DCC 使用另一个输入时钟作为参考来测量可选时钟源的频率。

8.4.4.8 DDRSS

该器件中的 DDR 子系统包括 DDR 控制器、DDR PHY 和封装逻辑,以将这些模块集成到器件中。 DDR 子系统称为 DDRSS0,用于提供与外部 SDRAM 设备的接口,可用于存储程序或数据。 DDRSS0 通过 MSMC 访问,而不是直接通过系统互连。

8.4.4.9 DSS 显示控制器

DSS 是一个灵活的支持组合的显示子系统,支持多个高分辨率显示输出。它由一个显示控制器(DISPC)和一个帧缓冲解压核心(FBDC)组成。 DISPC 支持其每个显示输出的多层混合和透明度。 DISPC 还支持具有缩放功能的回写管道,以实现内存到内存的组合和/或捕获以太网视频编码的显示输出。

8.4.4.9.1 DSI

MIPI DSI v1.3.1 控制器 (DSITX) 实现了 MIPI DSI 1.3 标准所需的流仲裁和低级协议层功能。

8.4.4.9.2 电子数据处理

VESA DP1.4/eDP1.4 兼容发射机主机控制器 (EDP) 可以输出多达 4 个视频流(通过多流传输 / MST)和一个音频流,通过 4 通道伴随 SerDes 模块。它提供高达 25.92 Gbps 的应用带宽。

8.4.4.10 VPFE

视频处理前端(VPFE)是一个输入接口模块,它接收来自外部成像外设(如图像传感器、视频解码器等)的原始(未处理)图像/视频数据或 YUV 数字视频数据,并执行 DMA 传输以存储在系统 DDR 内存中捕获数据。

8.4.4.11 eCAP

增强型捕获 (ECAP) 模块可用于:

• 音频输入的采样率测量

• 旋转机械的速度测量(例如,通过霍尔传感器感测的齿形链轮)

• 位置传感器脉冲之间经过的时间测量

• 脉冲串信号的周期和占空比测量

• 解码来自占空比编码的电流/电压传感器的电流或电压幅度。

有关更多信息,请参阅设备 TRM 的外设章节中的增强捕获 (ECAP) 模块部分。

8.4.4.12 EPWM

有效的 PWM 外设必须能够以最少的 CPU 开销或干预生成复杂的脉宽波形。它需要高度可编程且非常灵活,同时易于理解和使用。此处描述的 EPWM 单元通过分配所有需要的时序和

在每个 PWM 通道的基础上控制资源。避免了资源的交叉耦合或共享;

相反,EPWM 由具有独立资源的较小单通道模块构成,并且可以

根据需要共同运作以形成一个系统。这种模块化方法导致正交架构和

提供更透明的外围结构视图,帮助用户快速了解其操作。

8.4.4.13 ELM 错误定位模块

错误定位模块 (ELM) 与 GPMC 一起使用。读取 NAND 闪存页面时即时生成并存储在 GPMC 寄存器中的综合多项式将传递给 ELM。然后,主机处理器可以通过翻转 ELM 错误位置输出指向的位来纠正数据块。从 NAND 闪存读取时,需要进行一定程度的纠错。对于没有内部校正功能的 NAND 模块(有时称为裸 NAND),校正过程委托给存储器控制器。 ELM 还可用于支持并行 NOR 闪存或 NAND 闪存。

8.4.4.14 ESM 错误信号模块

错误信号模块 (ESM) 将整个设备中的安全相关事件和/或错误聚合到一个位置。它可以向处理器发出低优先级和高优先级中断信号,以处理安全事件和/或操纵 I/O 错误引脚以向外部硬件发出发生错误的信号。因此,外部控制器能够重置设备或将系统保持在安全的已知状态。

8.4.4.15 eQEP

增强型正交编码器脉冲 (EQEP) 外设用于与线性或旋转增量编码器的直接接口,以从旋转机器获取位置、方向和速度信息,以用于高性能运动和位置控制系统。增量编码器的磁盘是用单轨插槽图案图案化的。

8.4.4.16 通用输入输出口

通用输入/输出 (GPIO) 外设提供可配置为输入或输出的专用通用引脚。当配置为输出时,用户可以写入内部寄存器以控制输出引脚上驱动的状态。当配置为输入时,用户可以通过读取内部寄存器的状态来获取输入的状态。另外,GPIO外设可以在不同的中断/事件生成模式下产生主机CPU中断和DMA同步事件

8.4.4.17 GPMC 通用存储器控制器

通用存储器控制器是一个统一的存储器控制器,专用于与外部接口

存储设备,如:

• 类似 SRAM 的异步存储器和专用集成电路 (ASIC) 设备

• 异步、同步和页模式(仅在非多路复用模式下可用)突发 NOR 闪存

设备

• NAND 闪存

• 伪 SRAM 设备

有关更多信息,请参阅外设章节中的通用存储器控制器 (GPMC) 部分

设备 TRM。

8.4.4.18 超级总线

Hyperbus 模块是设备闪存子系统 (FSS) 的一部分。

Hyperbus 模块是低引脚数存储器接口,可提供高读/写性能。 Hyperbus 模块连接到 hyperbus 内存(HyperFlash 或 HyperRAM)并使用简单的 hyperbus 协议进行读写事务。设备内部有一个 Hyperbus™ 模块。 Hyperbus 模块包括一个 Hyperbus Memory Controller (HBMC)。

8.4.4.19 I2C

该器件包含 10 个多主控集成电路间 (I2C) 控制器,每个控制器都提供本地主机 (LH)(例如 Arm 或数字信号处理器 (DSP))与连接到 I2C 总线的任何 I2C 总线兼容设备之间的接口通过 I2C 串行总线。连接到 I2C 总线的外部组件可以通过 2 线 I2C 接口向左手设备串行发送和从左手设备接收最多 8 位数据。每个多主 I2C 模块都可以配置为充当从设备或主 I2C 兼容设备。

8.4.4.20 I3C

该器件包含三个改进的内部集成电路 (I3C) 控制器,每个控制器都提供本地主机 (LH)(例如 Arm)与通过 I3C 串行总线连接的任何 I3C 总线兼容设备之间的接口。

8.4.4.21 MCAN

控制器局域网 (CAN) 是一种串行通信协议,可有效支持分布式实时控制。

8.4.4.22 MCASP

MCASP作为通用音频串口,针对各种音频的需求进行了优化

应用程序。

8.4.4.23 MCRC 控制器

VBUSM CRC 控制器是一个模块,用于执行 CRC(循环冗余校验)以验证内存系统的完整性。

8.4.4.24 MCSPI

MCSPI 模块是多通道发送/接收、主/从同步串行总线。

8.4.4.25 MMC/SD

MMCSD 主机控制器为 eMMC 5.1(嵌入式多媒体卡)、SD 4.10(安全数字)和 SDIO 4.0(安全数字 IO)设备提供接口。

8.4.4.26 OSPI

八进制串行外设接口 (OSPI) 模块是一种串行外设接口 (SPI) 模块,允许对外部闪存设备进行单、双、四或八进制读写访问。

8.4.4.27 PCIE

外围组件互连 Express (PCIe) 子系统围绕多通道双模式 PCIe 控制器构建,该控制器可提供低引脚数、高可靠性和高速数据传输,每通道高达 8.0 Gbps 的速率,用于串行链路背板和印刷线路板。

8.4.4.28 串行解串器

SerDes 的目标是将设备 (SoC) 并行数据转换为可通过高速电气接口输出的串行数据。在相反的方向上,SerDes 将高速串行数据转换为设备可以处理的并行数据。为此,SerDes 包含各种功能块来处理外部模拟接口和内部数字逻辑。

8.4.4.29 WWDT

窗口看门狗定时器为操作系统和基准代码提供定时器功能。

8.4.4.30 定时器

所有计时器都包含特定功能,可向操作系统生成准确的滴答中断。每个定时器可以由几个不同的独立时钟提供时钟。时钟源的选择由 MCU_CTRL_MMR0/CTRL_MMR0 中的寄存器进行

8.4.4.31 串口

UART 是一个从外设,它利用 DMA 通过主机 CPU 进行数据传输或中断轮询。器件中有十二个 UART 模块。当使用 48 MHz 功能时钟时,所有 UART 模块都支持 IrDA 和 CIR 模式。每个 UART 可用于与多个外部外围设备或设备之间的处理器间通信的配置和数据交换。

8.4.4.32 USB

与早期版本的 USB 总线类似,USB 3.0 是一种通用电缆总线,支持主机设备和各种可同时访问的外围设备之间的数据交换。

8.4.4.33 UFS

通用闪存存储 (UFS) 接口是一种基于标准的串行接口引擎。设备内部有一个 UFS 模块 - UFS0。 UFS 模块包括一个带有集成 M-PHY 的 UFS 2.1 主机控制器 (HC)

逻辑框图

最后

以上就是要减肥哑铃最近收集整理的关于【TDA4系列】芯片资源:处理器Processor Subsystems 与 加速器和协处理器Accelerators and Coprocessors8.1 概述8.2 Processor Subsystems8.3 Accelerators and Coprocessors8.4 Other Subsystems逻辑框图的全部内容,更多相关【TDA4系列】芯片资源:处理器Processor内容请搜索靠谱客的其他文章。

发表评论 取消回复