计算机系统结构复习(四):Pipelining流水线

- 流水线相关概念与特点

- 流水线的相关概念

- 流水线主要特征

- 流水线的分类

- 指令级与部件级

- 线性与非线性

- 静态与动态(有大题)

- 流水的5个阶段:通过时间与排空时间

- 三种冲突:结构冲突、数据冲突、控制冲突

- 结构冲突

- 数据冲突

- 控制冲突

- 编译时调度的四种策略

- 延迟分支策略

- 停顿及其原因

- 数据冲突的种类:RAW,WAR,WAW

- 性能:时空图

- 吞吐率

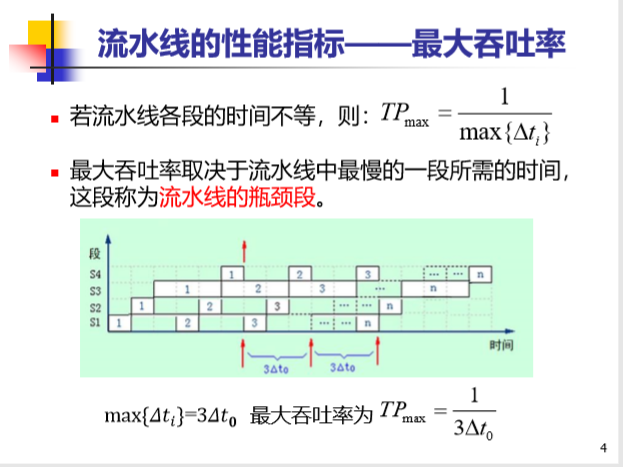

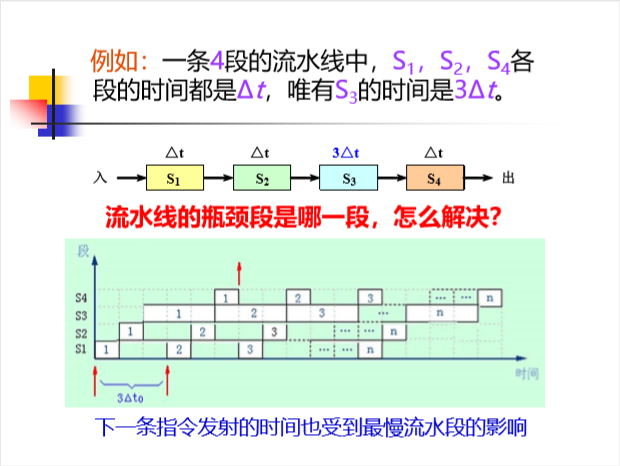

- 最大吞吐率

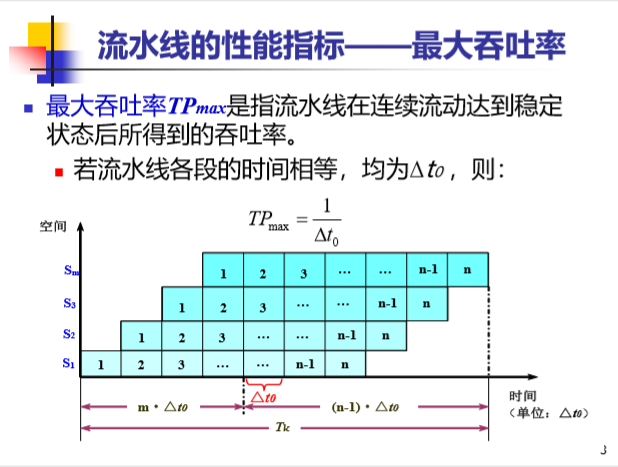

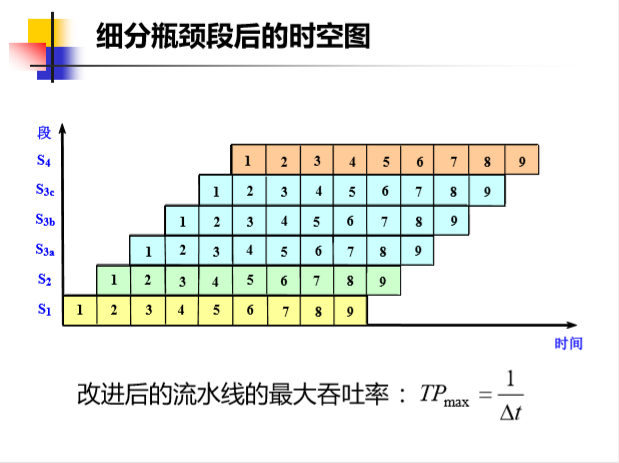

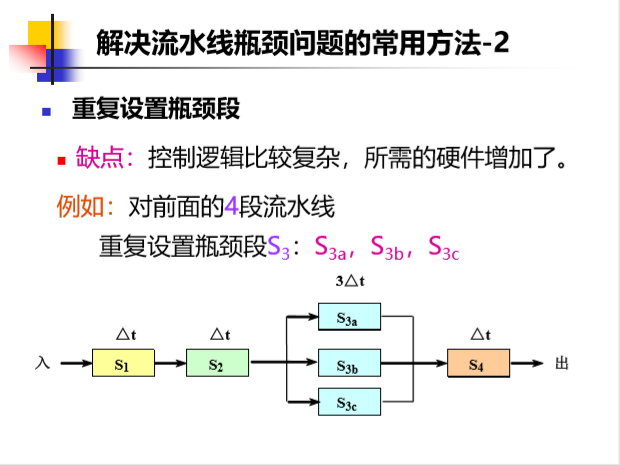

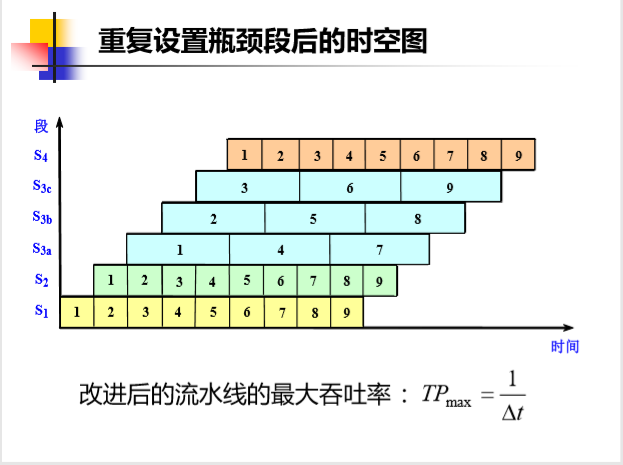

- 解决流水线瓶颈问题

- 细分瓶颈段

- 重设瓶颈段

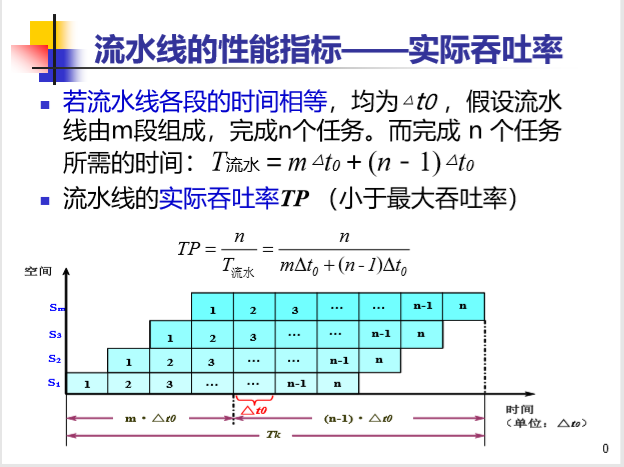

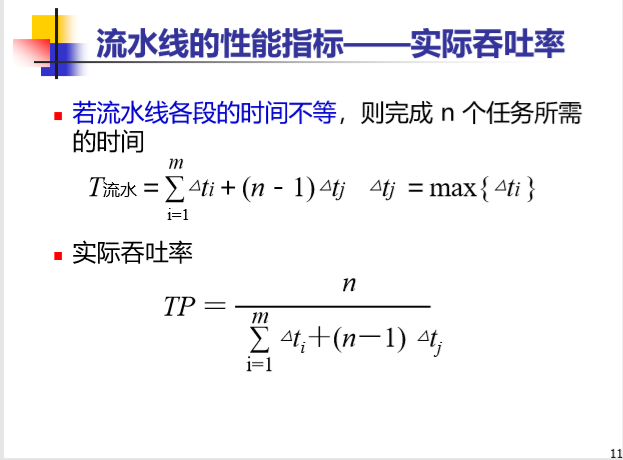

- 实际吞吐率

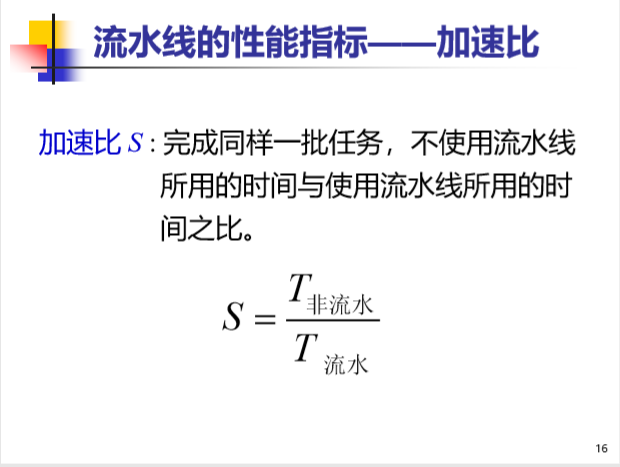

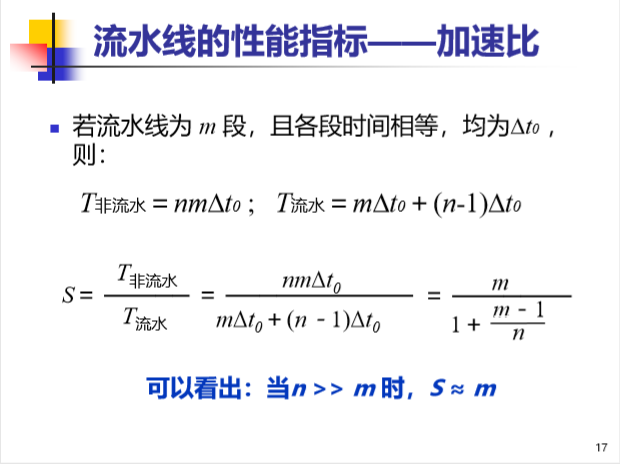

- 加速比

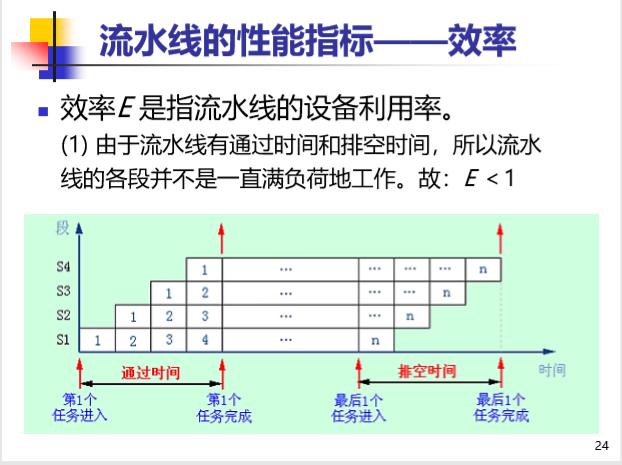

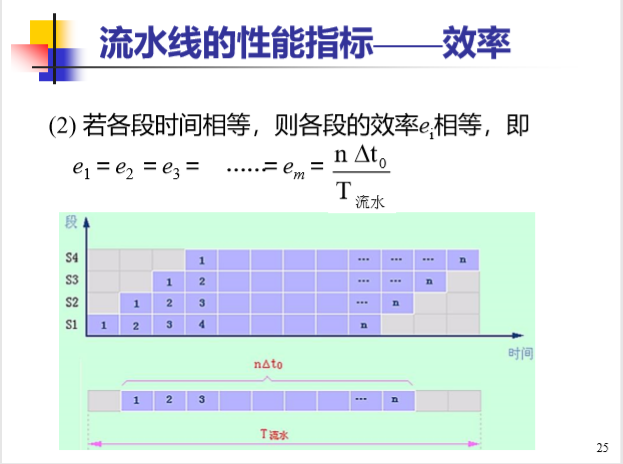

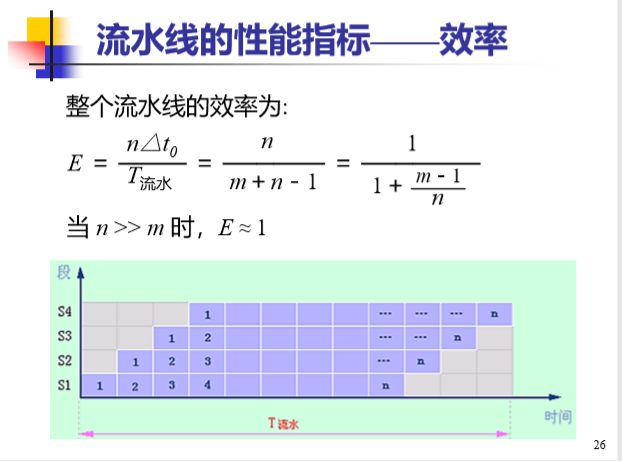

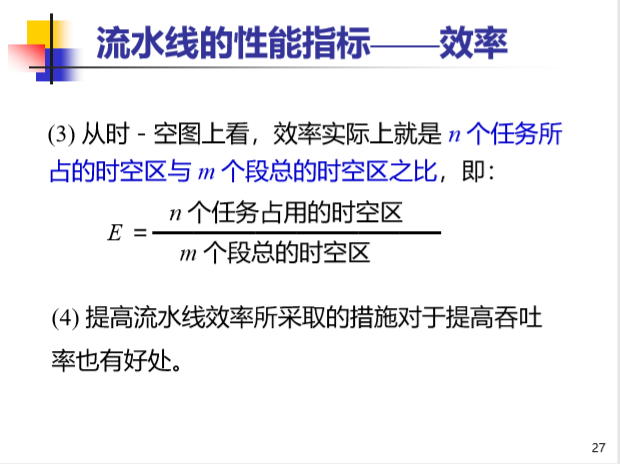

- 效率

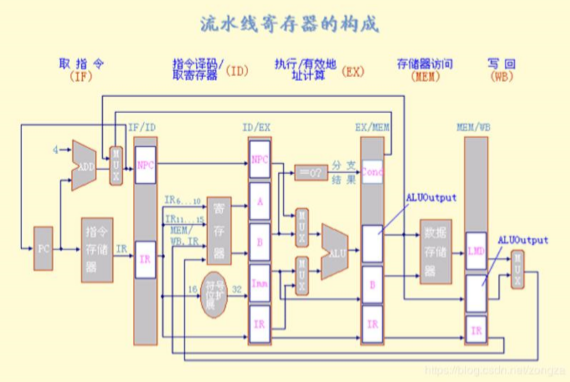

- MIPS五段流水组成

流水线相关概念与特点

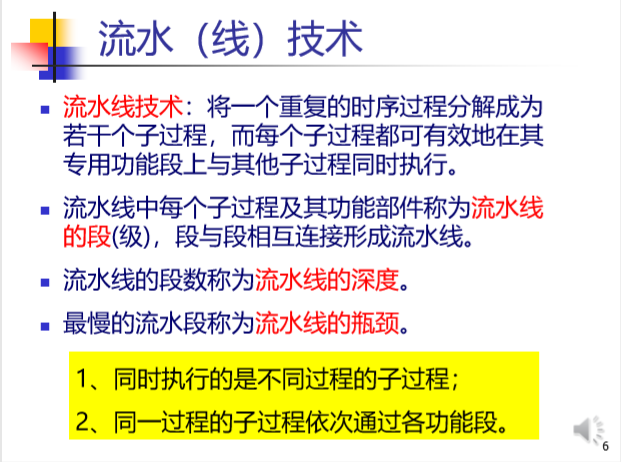

流水线的相关概念

流水线主要特征

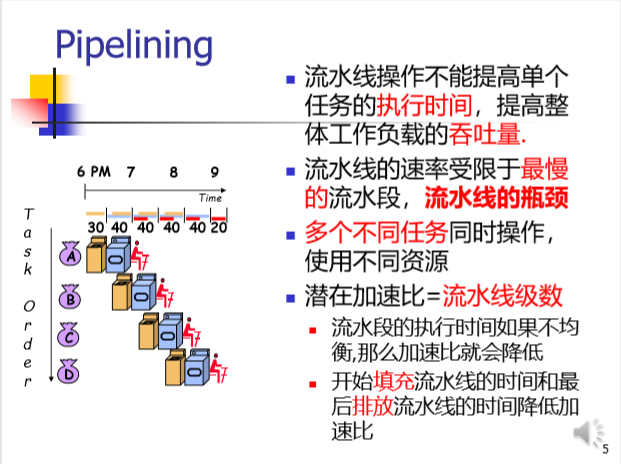

流水线通过使多个不同任务在不同资源上同时操作,来提高任务执行效率;

指令沿流水线移动一次的时间间隔就是一个机器周期;

流水线操作不能提高单个任务的执行时间,提高整体工作负载的吞吐量;

流水线的速率受限于最慢的流水段,该段称为流水线的瓶颈;

流水线的潜在加速比等于流水线的级数;

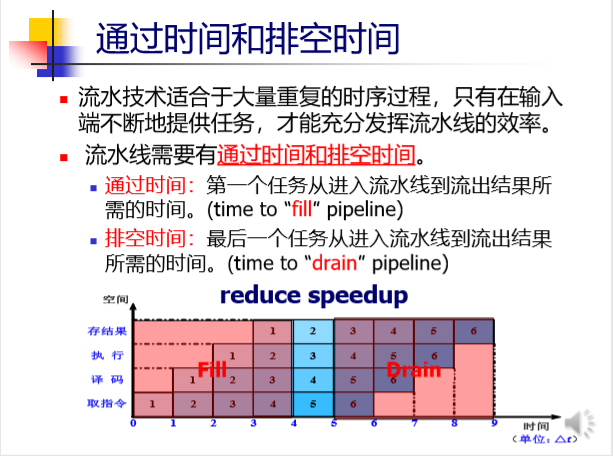

流水线有通过时间和排空时间。

流水线设计的目的在于平衡各段的长度。

流水线的分类

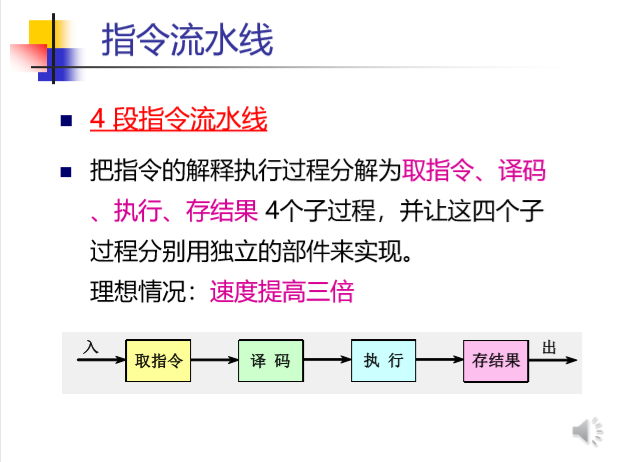

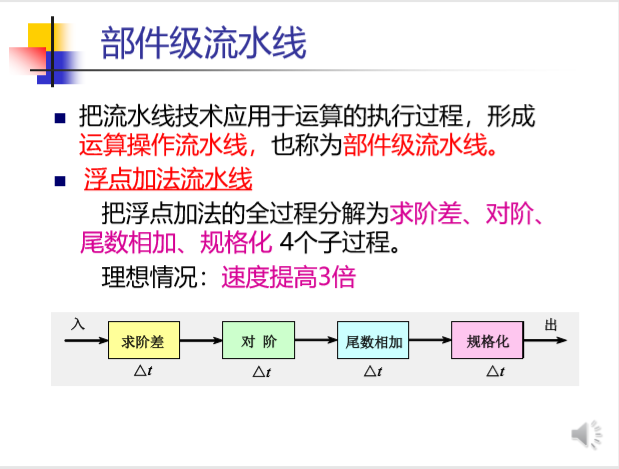

指令级与部件级

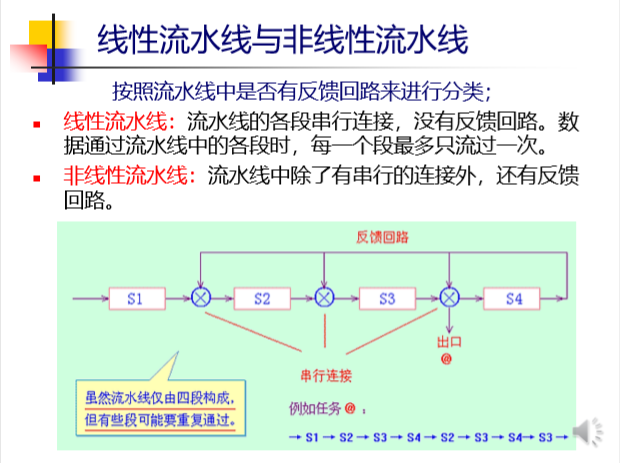

线性与非线性

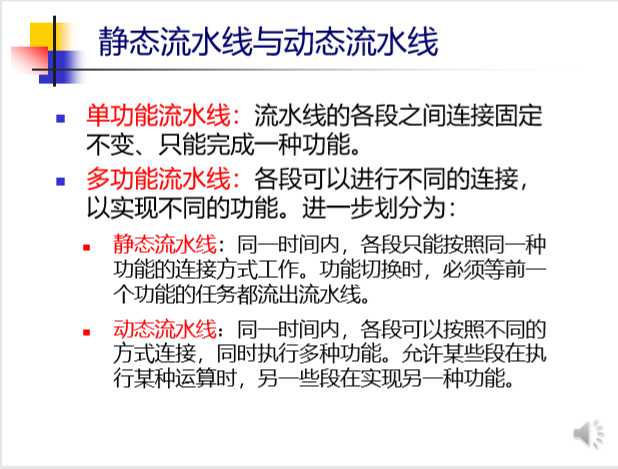

静态与动态(有大题)

流水的5个阶段:通过时间与排空时间

IF(取指令)-> ID(指令译码/取寄存器[针对分支转移指令])-> EX(执行/有效地址计算)-> MEM(存储器访问load或store)-> WB(写到寄存器,如 load 或者ALU 的计算结果)。

以RISC为例,每条指令长度4字节,每条指令执行时间至少是5 cycles。

流水线的通过时间: 从任务开始到稳定工作状态(段被填满)所需要的时间

流水线的排空时间:从稳定工作状态结束到最终任务 结果所需要的时间

三种冲突:结构冲突、数据冲突、控制冲突

结构冲突

原因: 因硬件资源竞争引起的冲突(某些功能部件没有充分流水或是某些资源没有充分重复设置)

<img src"https://img-blog.csdnimg.cn/20200831212550199.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzQzMDgwNjA5,size_16,color_FFFFFF,t_70" width= “50%”>

解决方法:

通过提高成本来重复设置部件或者改进硬件,使其充分流水。

比如指令cache和数据 cache 分离的方法(上图结构冲突由于两个指令同时需要访问 cache 引起 load 读数 据,Instr 3取指令)

数据冲突

原因:指令在数据流中重叠执行时需要用到前面 指令的结果产生的冲突

解决方法:

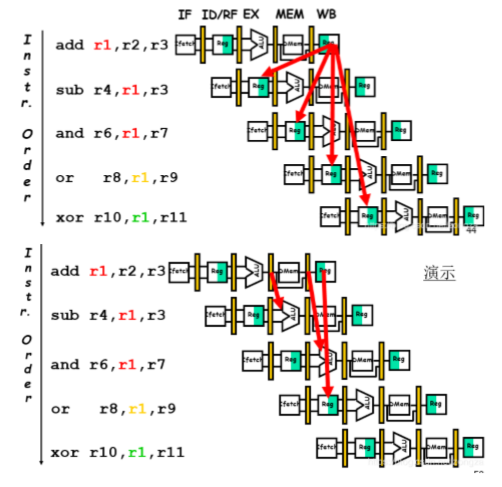

1.使用旁路技术解决数据冲突

定向(旁路)技术:使用流水线寄存器组直接向后面 的指令传递结果—— ALU输入的位置。

2. 编译器调度调整可能冲突的指令距离。

注意:

load指令和其他ALU指令不同,在使用定向解 决load和其后指令的冲突时仍有可能冲突。

因为 load 必须得等到 mem 段才能得到真正的数据,其他的ALU指令可能在 Ex 阶段就能算出结果,load必须访存。如上右图,这时候需要旁路 +Stall 一起用。

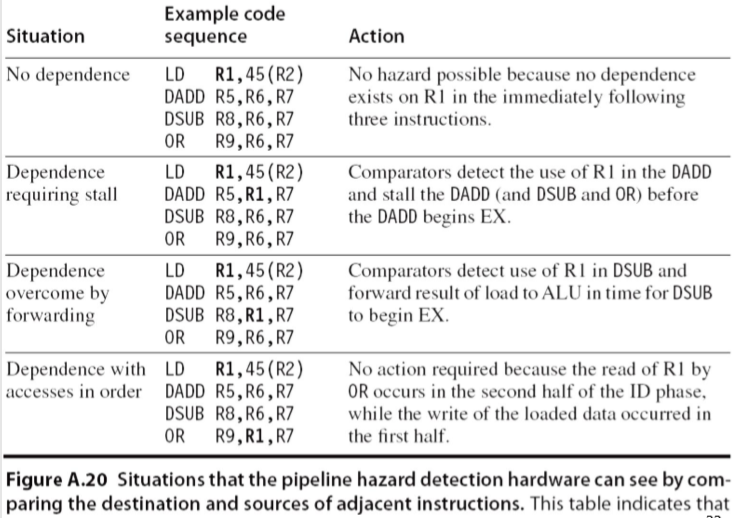

下图表显示了当 Load 指令与其他指令产生数据冲突时的解决方法。Load 的下一条指令只能 stall+forward, 下第二条指令可以forward,下三条指令无需操作(无冲突) 前半周期写回,后半周期读。

控制冲突

原因:流水线遇到分支指令或者其他改变PC值的指令所遇到的冲突。

解决方法:

1.编译时的分支预测

2.将分支判断与目标地址计算部件提前到ID段,将三个时钟周期(IDEXMEM)的暂停压缩为一个的办法。

3.使用分支延迟槽,选择适当的指令填充到其中,避免控制冲突引起的暂停。

编译时调度的四种策略

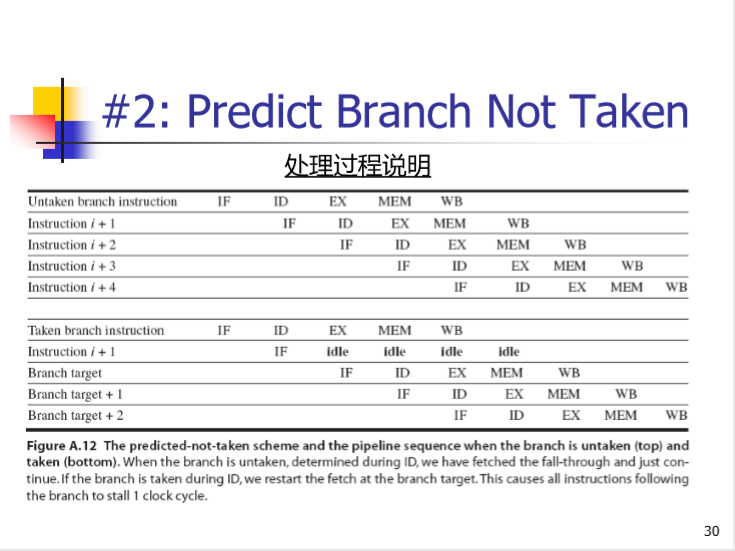

1.stall一直到mem段出结果

2.预测分支失败:沿失败的分支继续处理指令,即允许分支 指令后的指令继续在流水线中流动。如果确定分支失败,流水线正常流动;否则,将分支之后的指令作废(idle),按 分支目标地址重新执行。下图是在ID段计算跳转地址,预测失败(分支指令执行)只停顿一个时钟周期。如左下图所示。

3. 预测分支成功:沿成功的分支继续处理指令。

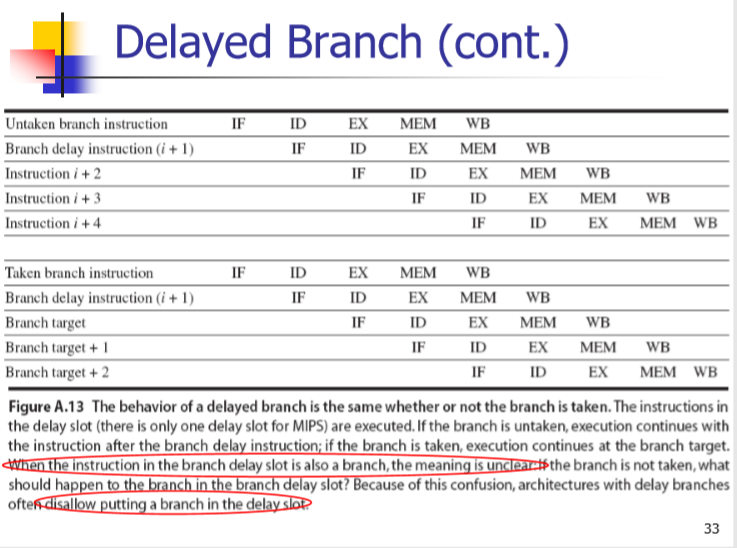

4. 延迟分支,使用编译器进行指令静态调度,调到延迟槽中。 MIPS用的是只有一条指令的延迟槽,这种方法和方法2、3几乎没区别,只是槽里的指令不会被idle,也可以不是第 i+1 条指令。如右下图所示。

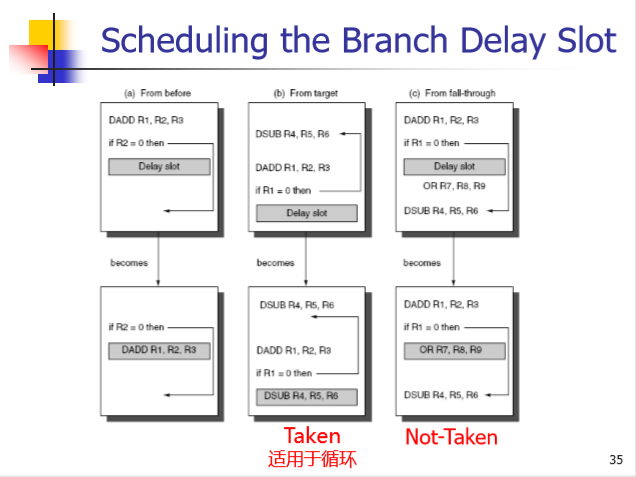

延迟分支策略

从前调度(最常用):把位于指令之前的一条独立的指令移到延迟槽。当无法使用从前调度则使用后两种。

从目标处调度:把目标处的指令复制到延迟槽, 同时修改分支指令的地址(箭头处)。

从失败处调度

后两种方法在使用时要保证猜测错误时延迟槽中的指令不会影响程序的正常运行。

停顿及其原因

Stall停顿:当发生冲突时,往往需要使某些指令推后 执行,从而使流水线出现停顿。

当一条指令被暂停时:在该指令之后流出的所有指令都要被暂停; 在该指令之前流出的指令则继续执行。

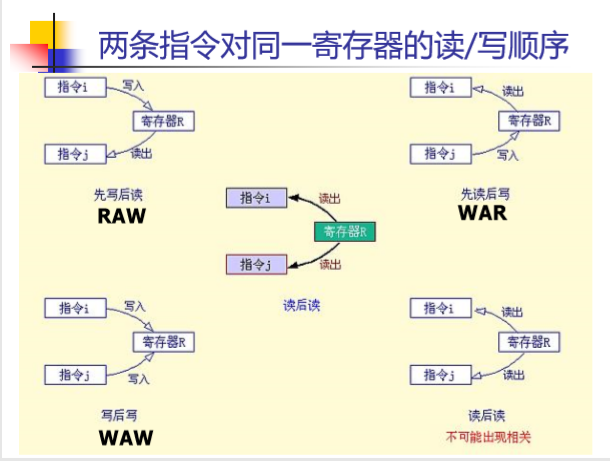

数据冲突的种类:RAW,WAR,WAW

MIPS五级流水中只会出现RAW冲突。

WAR和WAW又称为名相关(修改变量名即可解决冲突)

RAW:真相关

WAW:输出相关

WAR:反相关

性能:时空图

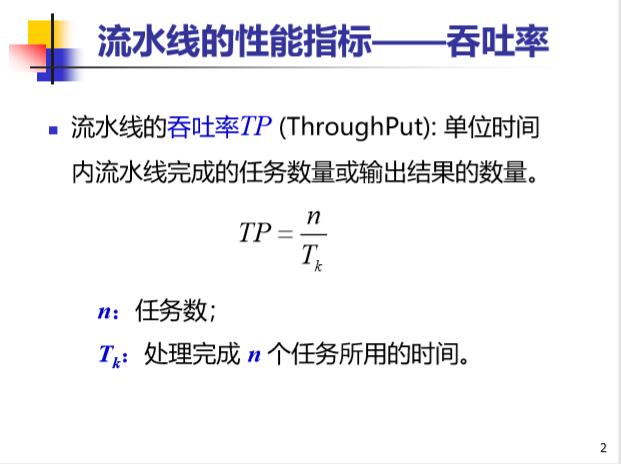

吞吐率

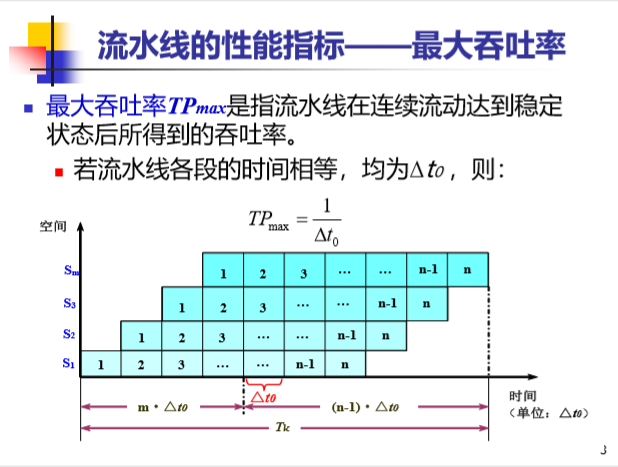

最大吞吐率

解决流水线瓶颈问题

细分瓶颈段

重设瓶颈段

实际吞吐率

加速比

效率

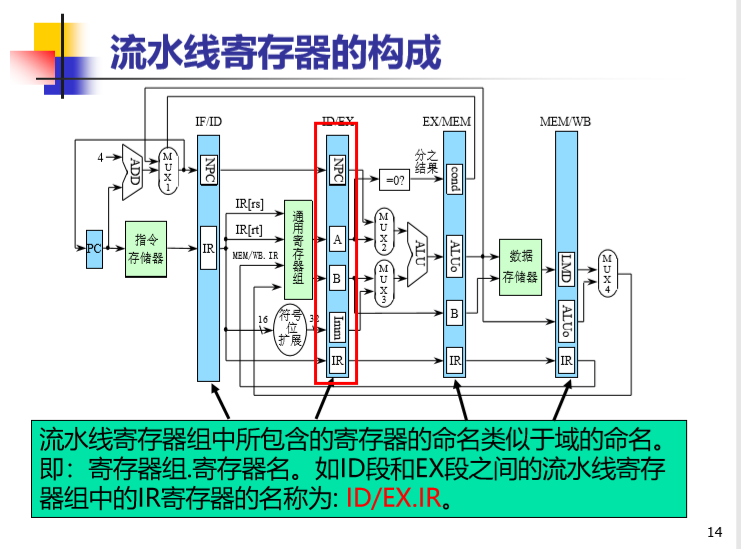

MIPS五段流水组成

每个流水段的操作:

IF段:根据PC值取指令存入IR,PC+4获取下一条指令地址,若分支指令条件为真,则用分支目标地址填充PC;

ID段:指令译码,同时根据指令格式和类型,取得通用寄存器中的数据或者立即数,送至流水线锁存器A、B;

EX段:

ALU指令:针对不同指令进行以寄存器或者立即数为操作数的数逻运算;

LOAD/STORE指令:进行基地址+偏移量的有效地址计算;

分支指令:进行分支条件判断;进行分支目标地址的计算;

MEM段:

ALU指令:数据传送,不做实质性操作;

LOAD/STORE指令:根据计算得到的有效地址,到内存中读数据或者将数据写到内存中;

WB段:

ALU指令:针对不同指令,将计算结果写回到通用寄存器中;

LOAD指令:内存取回的数据写回到通用寄存器中。

最后

以上就是轻松帅哥最近收集整理的关于计算机系统结构复习(四):Pipelining流水线流水线相关概念与特点流水的5个阶段:通过时间与排空时间三种冲突:结构冲突、数据冲突、控制冲突停顿及其原因数据冲突的种类:RAW,WAR,WAW性能:时空图MIPS五段流水组成的全部内容,更多相关计算机系统结构复习(四):Pipelining流水线流水线相关概念与特点流水内容请搜索靠谱客的其他文章。

发表评论 取消回复