RRU原理详解,光口子系统+Low-Phy

- CPRI与eCPRI

- CPRI协议

- eCPRI协议

- O-RAN

- Low-Phy

- MIMO多天线技术

- OFDM正交频分复用技术

- FFT与IFFT

- MIMO技术的实现

- 数据通道

- 数字混频(Mixer)

- FIR滤波器

- FIR滤波器串并行结构

- DUC(数字上变频)滤波器

- DDC(数字下变频)滤波器

- CFR(Crest Factor Reduction)算法

- DPD(Digital Pre-Distortion)算法

- 数字预失真DPD与PA(功率放大器)

- JESD204B接口协议

- 模拟信号模块

- DAC数模转换器

- LNA

- ADC模数转换器

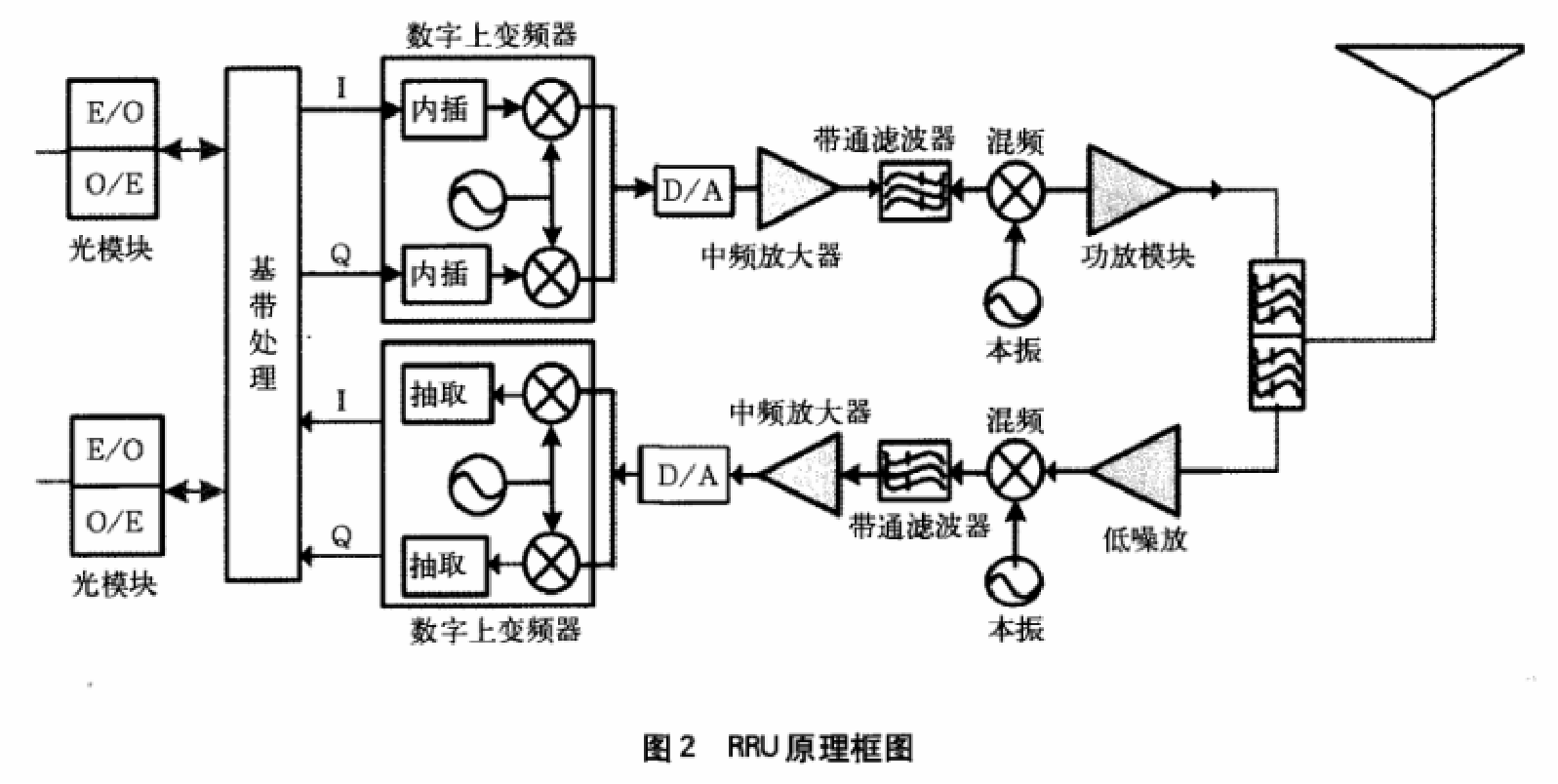

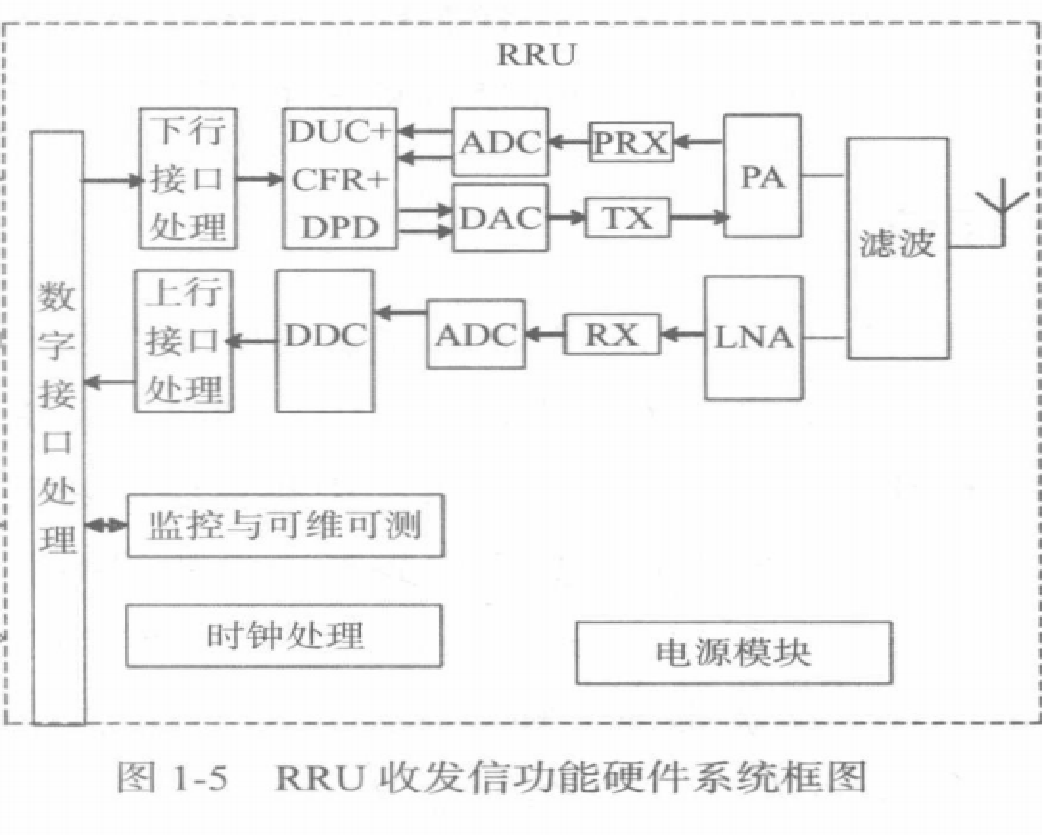

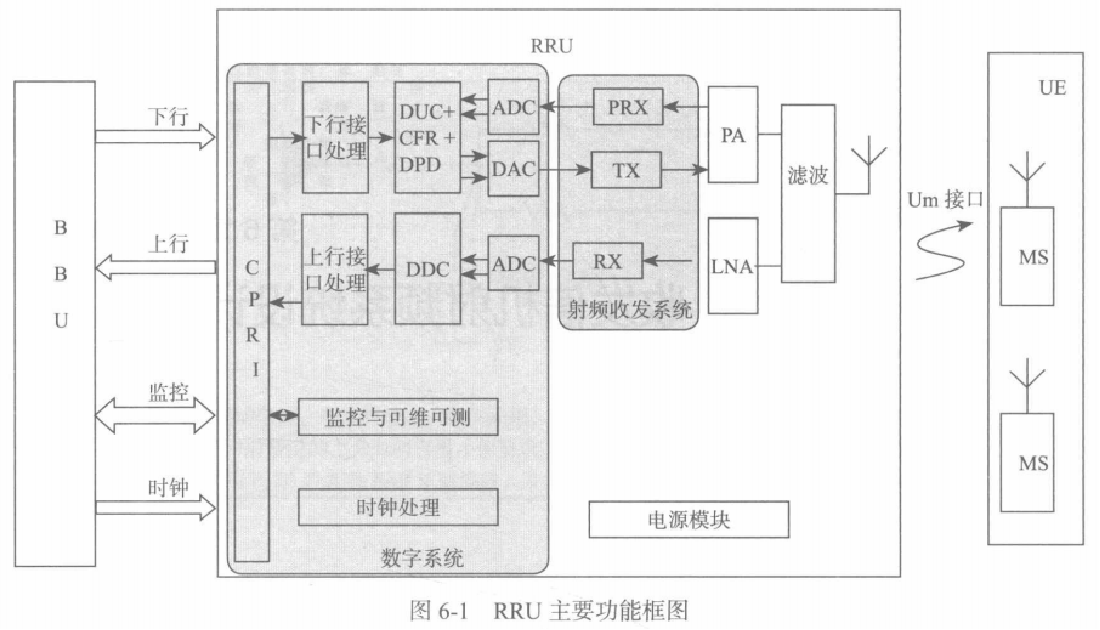

关于RRU系统的框架与基本原理

CPRI与eCPRI

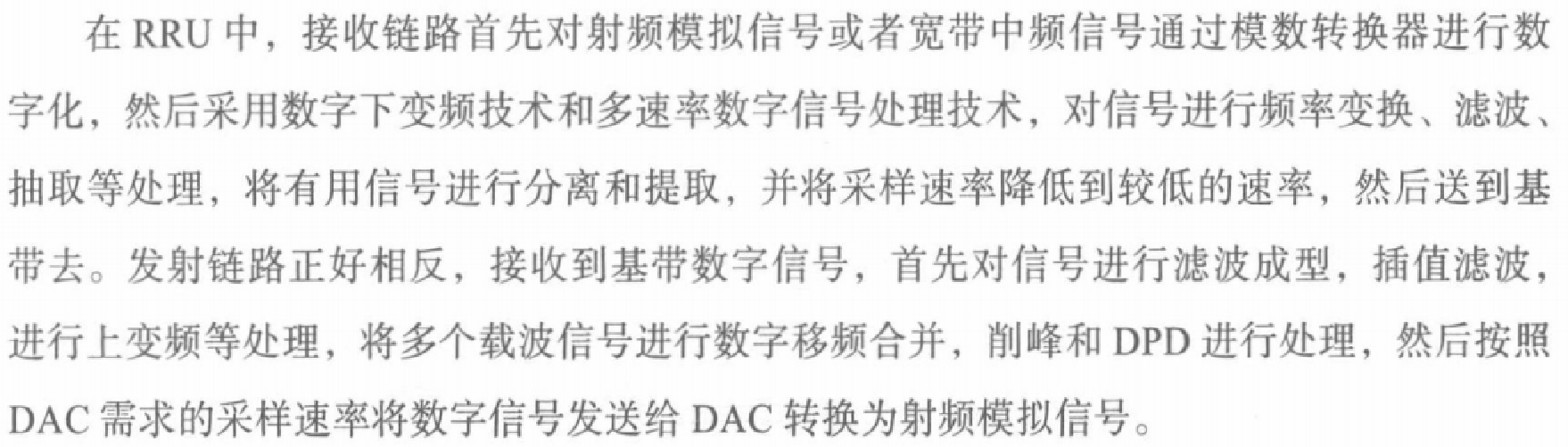

CPRI协议

接口标准:

1、上行中,CPRI支持I和Q各4到10位的采样宽度;在下行中,支持I和Q各8到20位的采样宽度。

2、在用户面(L1)支持的传输速率至少为200Kbit/s,另外协议规定控制面每AxC(天线载波)至少支持25Kbit/s。

3、在RRU中,为产生本地时钟的主要参考时钟,必须同步于从端口的位时钟。CPRI保证RRU完成时钟同步必须小于10s。

4、线位速率:最小线位速率是614.4Mbit/s,所有线位速率都是以基本码速率3.84Mbit/s为基础的。

CPRI的链路层定义了一个同步的帧结构。帧结构中最重要的概念是基本帧和超帧。基本帧的频率是3.84MHz,每个基本帧包含16个时隙,根据线路速率的不同,时隙的大小分别是1B,2B,4B。

定义超帧的目的是为CPRI协议增加控制和同步功能。每256个基本帧构成一个超帧(一个无线帧由150个超帧组成)。这个控制结构中,逐级嵌套的256个控制字按每4个字一组编为64个子信道。子信道序号Ns=0~63,每个子信道里的控制字序号Xs=0~3,一个嵌套里的控制字序号X=Ns+64×Xs,即每个子通道内的相邻时隙,相互间隔是64个基本帧长度。

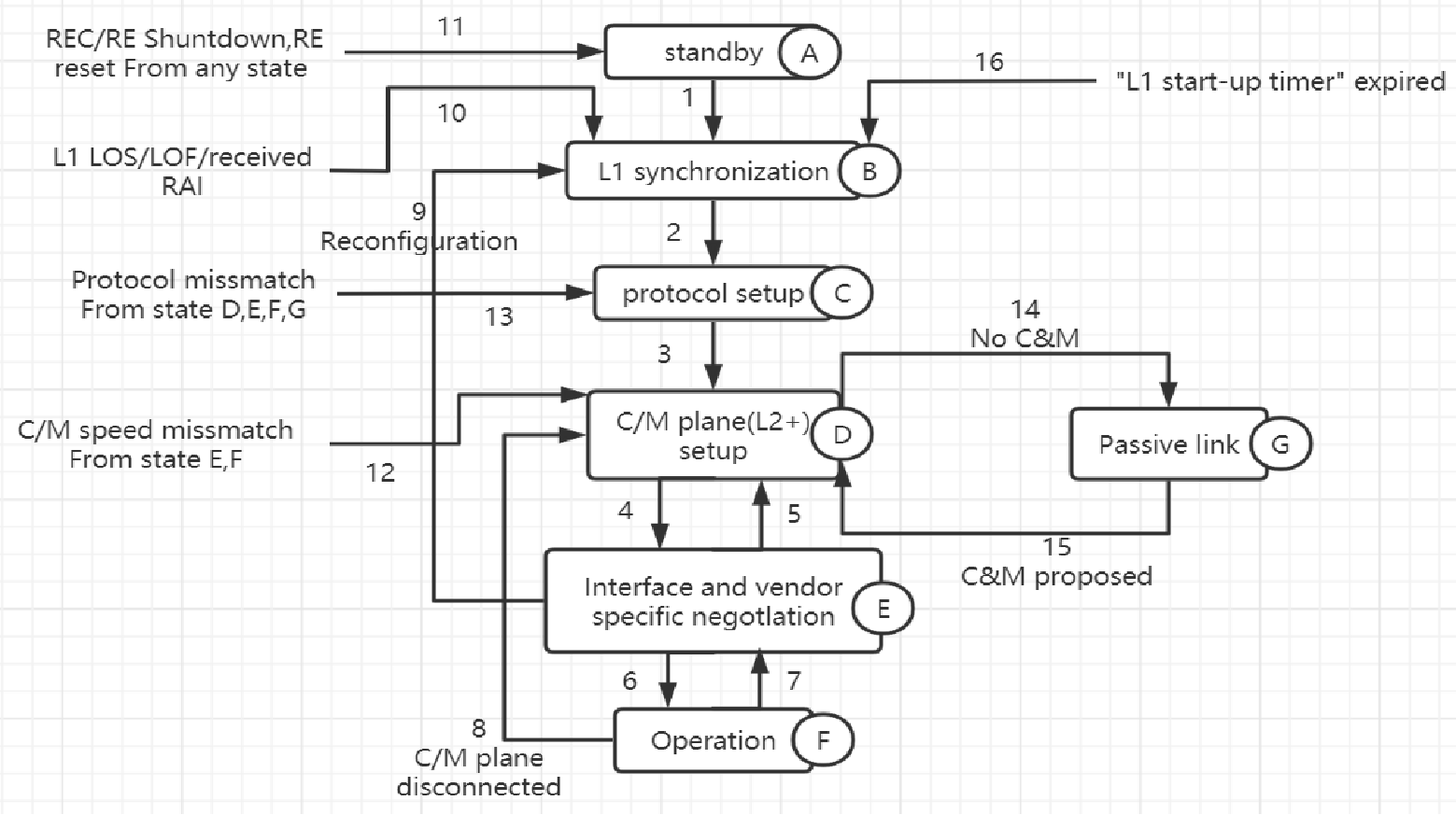

下图是CPRI的状态机转换图:

CPRI协议的不足:

(1)CPRI数据量过大

每一个天线数据的采样都会比编码成15+15=30bit的IQ数据。导致BBU与RRU之间需要传输高带宽的数据。

一根9.8G的光纤,在没有IQ压缩的情况下,只能承载2个4T4R的20M小区。1个4T4R的50M小区, 1个2T2R的100M小区, 1个1T1R的200M小区。

(2)无法支持5G的大规模阵列天线的场景

比如64天线的100M小区,需要32跟9.8G的CPRI, 很显然,这是很不现实的,CPRI已经无法无法胜任5G的应用场景。

(3)虽然CPRI协议是标准协议

CPRI并没有对承载的L3层协议进行规范,3GPP也没有对齐进行规范,导致不同厂家的BBU与RRU无法互联互通。

(4)CPRI协议虽然标准协议,但并不通用。

为了克服上述(1)和(2)的缺点,引入的eCPRI协议。(enhanced CPRI)

为了克服上述(3)和(4)的缺点,指定了5G O-RAN前传接口。

正因为如此,所以才有改进出eCPRI的机会。

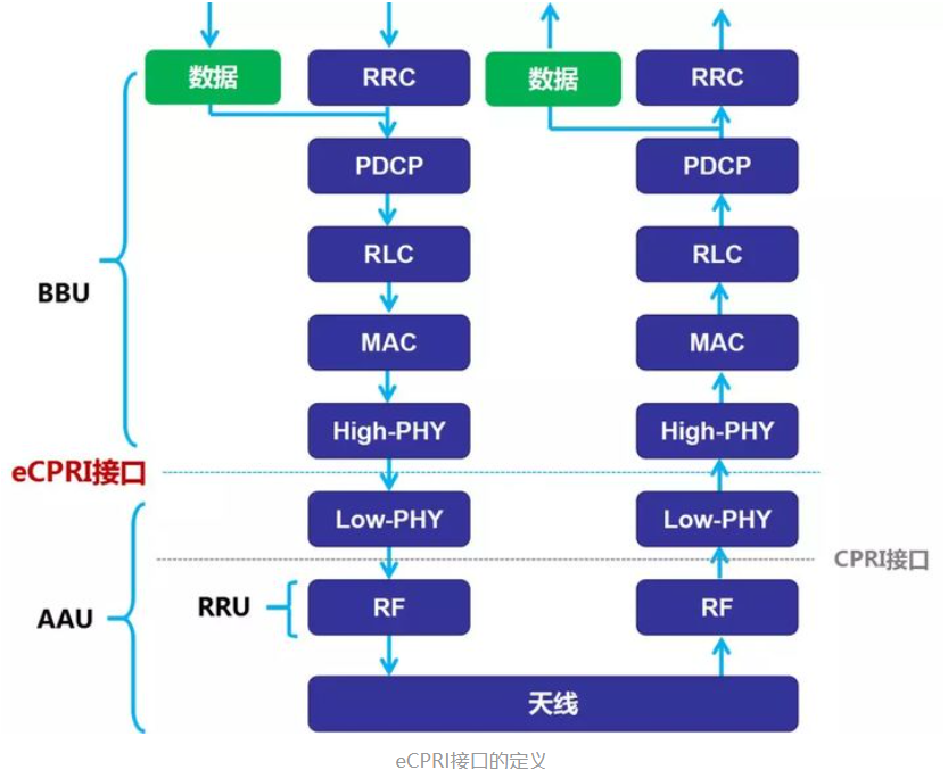

eCPRI协议

eCPRI的设计思路很简单,既然通信协议栈上传输的数据会层层加码,越到物理层数据量越大,那就如上图所示,把在BBU上处理的数据上移一层(High Phy往上的BBU处理),下面的交给RRU去处理(Low Phy往下的RRU处理),这样BBU和RRU之间的数据量就少了,代价是RRU的复杂度提升。

eCPRI:具有如下的特点:

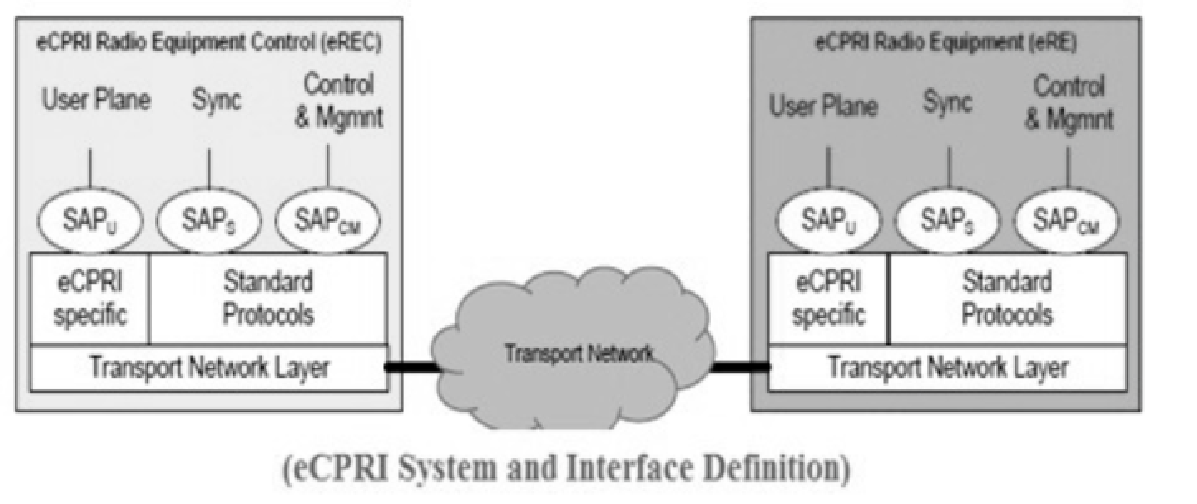

该网络由eCPRI节点组成,包括 eRECs / eREs,传输网络( transport network(fronthaul network) )和其他网络元素,例如用于定时的GM / BC和用于网络管理的EMS / NMS。

不支持物理级别的主端口/从端口分类。

•SAP_S:PTP和同步以太网的主服务器通常不是eREC。

•SAP_CM:某些M-plane可能由EMS / NMS管理。

eCPRI层位于传输网络层之上,传输网络(fronthaul network)可能包括一些本地网络,例如 eREC / eRE供应商提供的本地交换机。

eCPRI支持以下的逻辑连接:

• 点对点

•指向多点

•多点到多点

eCPRI节点需要实现适当的传输网络层协议,以支持冗余,安全性和QoS等功能。

一般来说大家都选择承载在MAC层帧之上,这种方案,通常处于低延时的考虑,因此这种情形下,eCPRI协议的解析,与CPRI协议类似,通常由FPGA专用的eCPRI IP核来完成。

eCPRI协议中上下行链路:

1、向下:eCPRI协议是封装在UDP、TCP协议之上,也可跳过TCP/IP协议栈,直接承载在MAC以太网帧之上。在实际实现时,为了降低PHY_High与PHY_Low之间的延时,通常把eCPRI协议直接封装在MAC层以太网帧之上。

2、向上:提供了与CPRI协议一样的三个服务访问点:

User Plane(用户面)数据:在这里就是PHY_High与PHY_Low之间的IQ手机用户数据,是通过eCPRI协议进行封装的。

Sync(同步面):这里是PHY_High与PHY_Low之间的同步,是RRU与DU之间时钟同步,该服务主要是标准的IEEE1588协议提供。

控制与管理协议:控制协议是PHY_High与PHY_Low的信令消息。管理协议主要只对RRU的OAM(操作、维护、管理)数据,它通过标准的HTTP或ssh协议承载。而控制协议,主要用于PHY_High与PHY_Low之间的信令控制,可以通过eCPRI协议承载,也可以通过标准UDP或TCP承载,通常情况下,会通过eCPRI协议来承载。

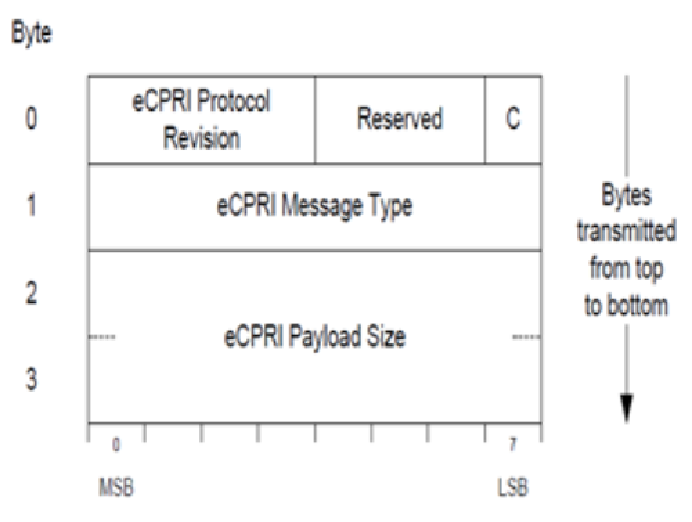

eCPRI协议的消息头结构:

Revision:协议版本

C: 串联指示,0表示eCPRI的数据净荷eCPRI message中终止; 1表示eCPRI的数据净荷还没有传输结束,后续的eCPRI message中继续传输与本数据净荷为一体的数据。C标志位的引入,为eCPRI协议传输大于65535字节的数据净荷提供了技术保障,可以这样说,只要双方的内存空间和延时需要允许,eCPRI可以传送任何字节大小的数据净荷。

eCPRI Message Type:eCPRI协议类。

eCPRI Paylod size:16bit,指明本message中,eCPRI净荷的大小。

进入5G时代,鉴于运营商的利益考虑,各个运营商对基站制造商的黑盒子表示不太接受,因为5G需要的基站数量巨大,而以前由于黑盒子的情况(以前的基站设备对运营商来说是黑盒子),导致你的设备需要从同一个制造商来采购成套的,可以理解为被套死。因此提出了一个叫O-RAN的协议规范。

O-RAN

O-RAN:开放无线接入网联盟(协议规范), 其主要的宗旨就是在5G的规范的基础之上,制定未开放接口的规范,推动无线接入网向开放化、白盒化、开源化方向放发展。

eCPRI作为无线接入网RAN中DU与RU之间的标准接口,称为fronthual接口,这是O-RAN关注一个重点:

(1)eCPRI协议与CPRI协议类似,只是传输层协议,并没有定义其业务访问点之上的应用层协议规范,如IQ数据格式,实时控制面数据格式, 因此需要新的规范了约束这些应用接口, O-RAN的作用就体现出来了。

(2)OAM管理面和1588同步面都从eCPRI服务中剥离出去了,它们可以通过标准的TCP/IP协议栈进行传输,不一定需要eCPRI来承载,因此OAM管理面和1588同步面的协议规范,无法被eCPRI协议所规定, O-RAN的作用由体现出来了。

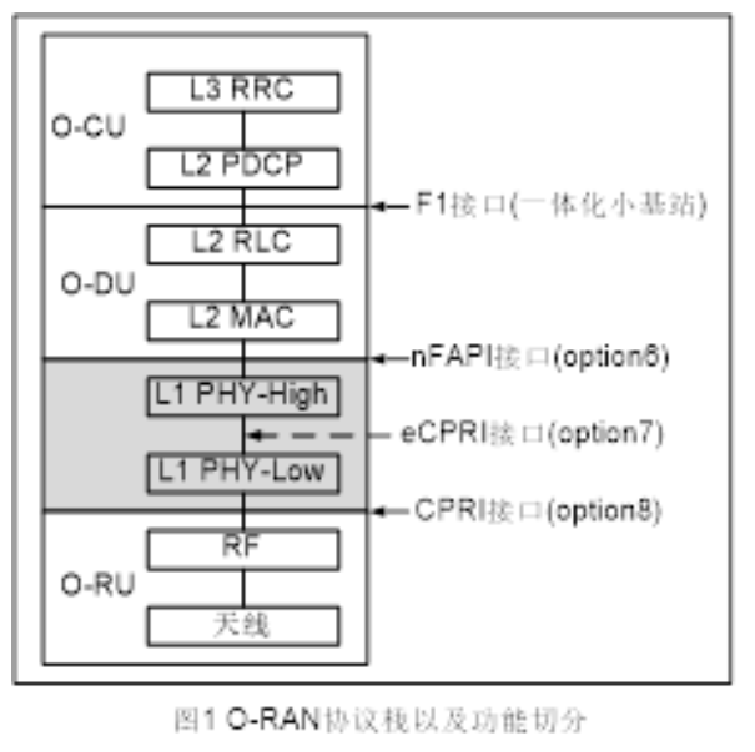

(3)eCPRI协议是O-RAN多个前传接口规范之一,如图所示:

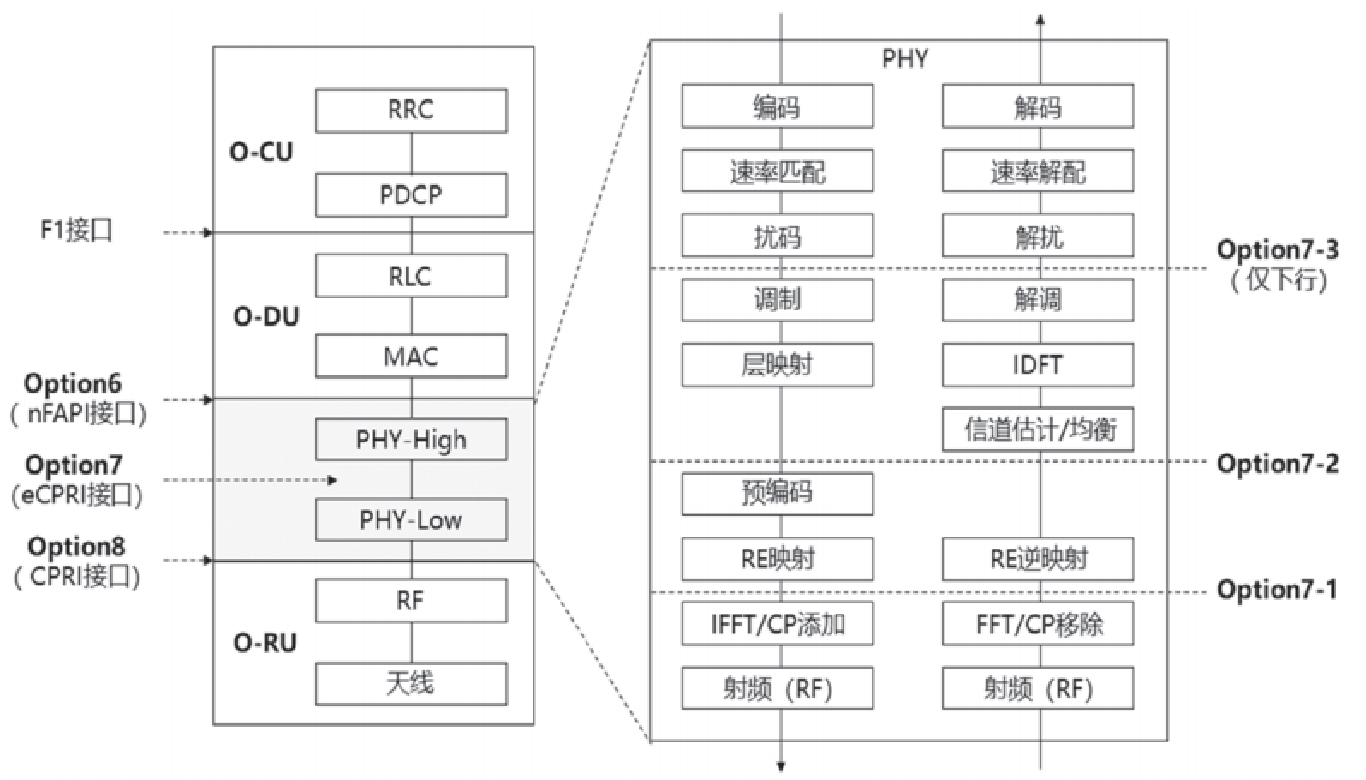

O-RAN将基站系统划分为O-CU(控制单元)、O-DU(分布单元)、O-RU(射频单元),其中,O-CU 和 O-DU 之间的高层分离接口沿用了 3GPP F1 接口,O-DU 与 O-RU 之间的底层分离接口根据协议栈分离点的不同,存在多种划分方案,包括 Option6(即nFAPI 接口)、Option7(即 eCPRI 接口)和 Option8(即CPRI 接口)。

其中,Option7 最显著的特点是将物理层划分为 PHY-High 和 PHY-Low,可通过压缩技术来降低O-DU 和 O-RU 之间所需的前传带宽需求。Option7 又可进一步细分为 Option7-1、Option7-2 和 Option7-3。

因为O-RAN将Option7分为3个子接口,因此又可以提到有关Low-Phy的东西了。(这一部分很难,数学理论很多很杂,我只描述一个大概,不会做太深入的讲解)。暂时不会提High-Phy,我暂时没有接触过这方面。

Low-Phy

Low-Phy包括哪些处理呢?

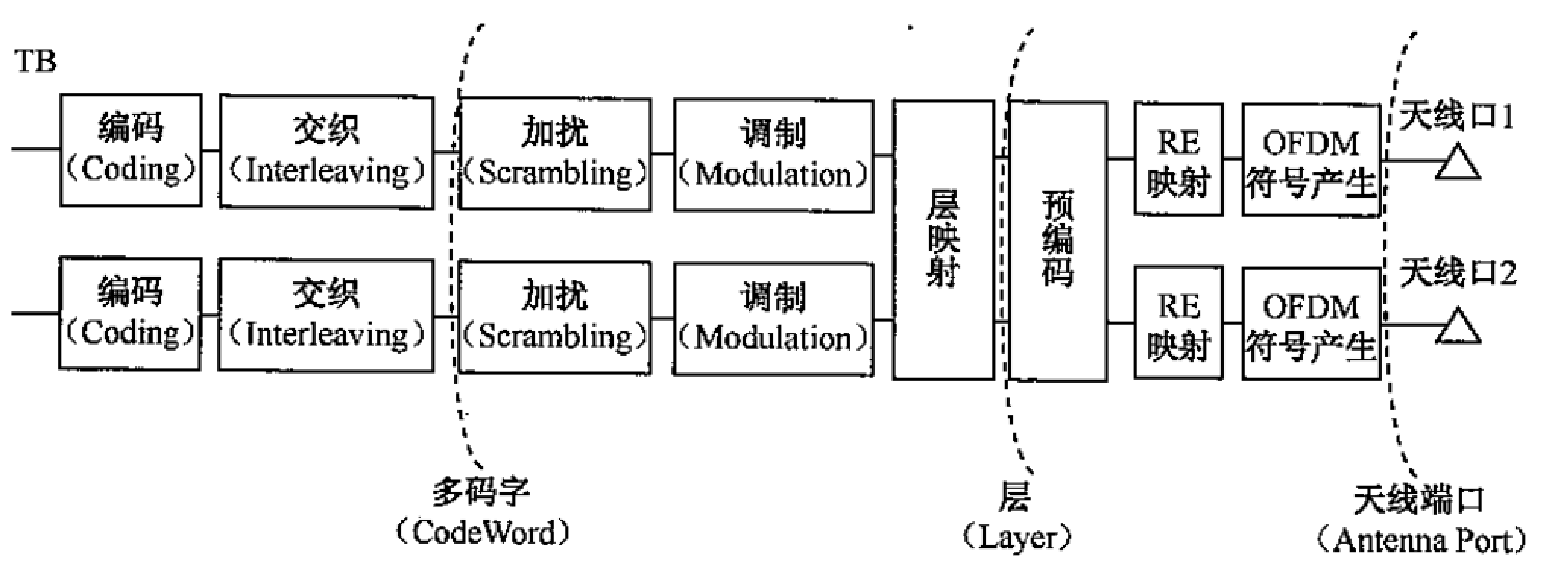

预编码矩阵,MIMO”层“到逻辑天线端口映射:对映射到MIMO各层的数据进行预编码,并完成对逻辑天线端口的映射,逻辑天线端口的数目可以大于等于MIMO的“层数”。

信道估计与信道均衡:MIMO技术采用多天线收发。由于天线之间的物理位置差异,收发双方通过多根天线之间的位置关系产生了多种不同的收发路径效果,如果这多种路径效果最终能很有效的结合起来互相弥补不足,则可以达到更好的传输质量。

RE时频资源映射RE mapping:把数据映射到一定带宽的载波的各个子载波的时频资源上。

数字波束赋形Digital Beamforming:通过控制各自子载波的相位权重,自控各个子载波的波束赋型。

快速傅里叶变换FFT与逆变换IFFT以及循环前缀处理:OFDM多址复用。

CPRI物理端口映射:把IQ AxC格式的时域OFDM符号,映射到不同的CPRI物理端口上。当BBU与RRU之间有多条CPRI连接的时候,这个映射就很重要。

MIMO多天线技术

最早的多天线技术是一种接收分集技术。多条接收通道同时处于深度衰落的可能性比单天线通道处于深度衰落的可能性小很多。接收分集可以提高无线传输的可靠性,基站侧布置多个接收天线实现上行接收分集较为容易。但终端侧布置多个天线会提高手机复杂度和成本,实现较困难,那能不能在基站侧实现发射分集(多天线发射相同的数据流)来提高下行传输可靠性呢?人们尝试这样做,但发现多天线发送相同的数据流,他们是相互干扰的,甚至会相互抵消,起不到分集的作用。想要实现发送分集,必须解决发送天线之间无线链路的正交性问题。有了OFDM技术后,多天线正交性的问题最终被攻克,于是MIMO技术成熟。

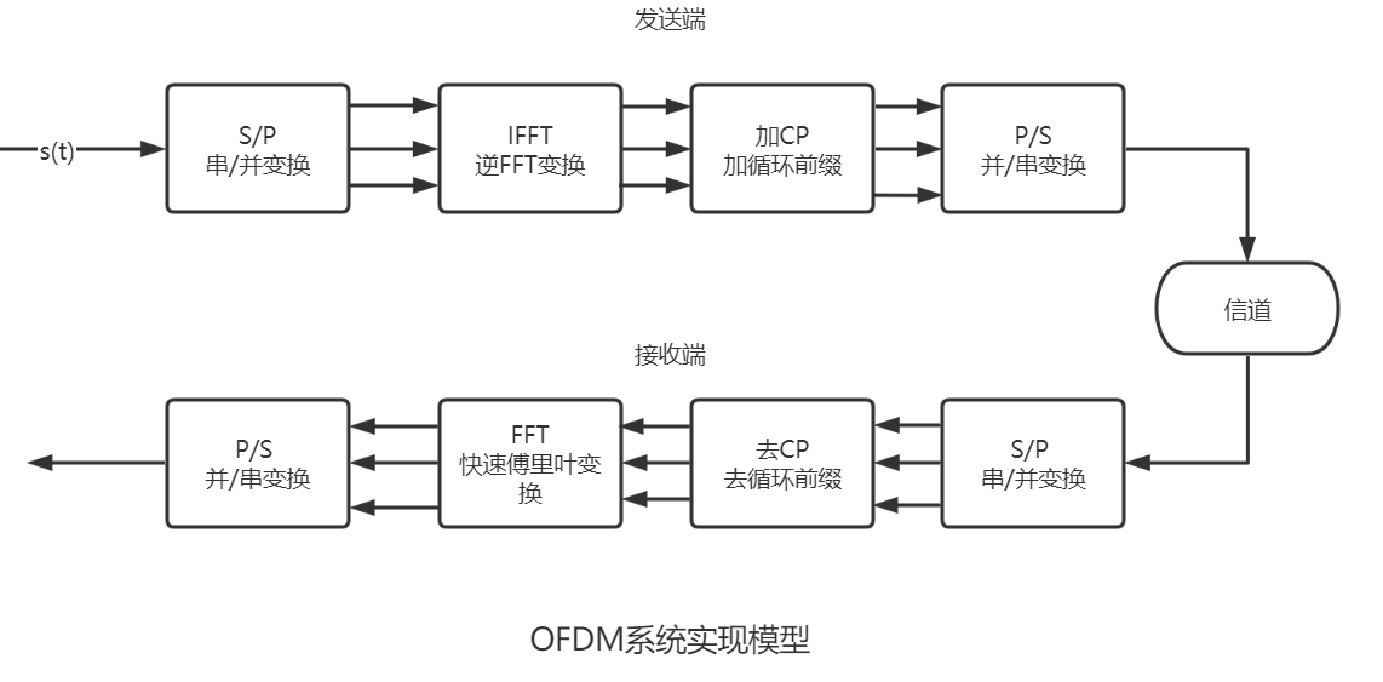

OFDM正交频分复用技术

OFDM技术:将高速信息数据流通过串并变换,分配到速率相对较低的若干子信道中传输,每个子信道中的符号周期相对增加,这样可减少因无线信道多径时延扩展所产生的时间弥散性对系统造成的码间干扰。另外,由于引入保护间隔,在保护间隔大于最大多径时延扩展的情况下,可以最大限度地消除多径带来的符号间干扰。如果用循环前缀作为保护间隔,还可避免多径带来的信道间干扰。

与FDM的区别:采用N个重叠的子频带,子频带间正交,因而在接收端无需分离频谱就可将信号接收下来。

优点:正交的子载波可以利用快速傅利叶变换(FFT/IFFT)实现调制和解调。对于N点的IDFT运算,需要实施N^2次复数乘法,而采用常见的基于2的IFFT算法,其复数乘法仅为(N/2)log2N,可显著降低运算复杂度。

在OFDM系统的发射端加入保护间隔,主要是为了消除多径所造成的ISI。其方法是在OFDM符号保护间隔内填入循环前缀,以保证在FFT周期内OFDM符号的时延副本内包含的波形周期个数也是整数。这样时延小于保护间隔的信号就不会在解调过程中产生ISI。由于OFDM技术有较强的抗ISI能力以及高频谱效率,2001年开始应用于光通信中,相当多的研究表明了该技术在光通信中的可行性。

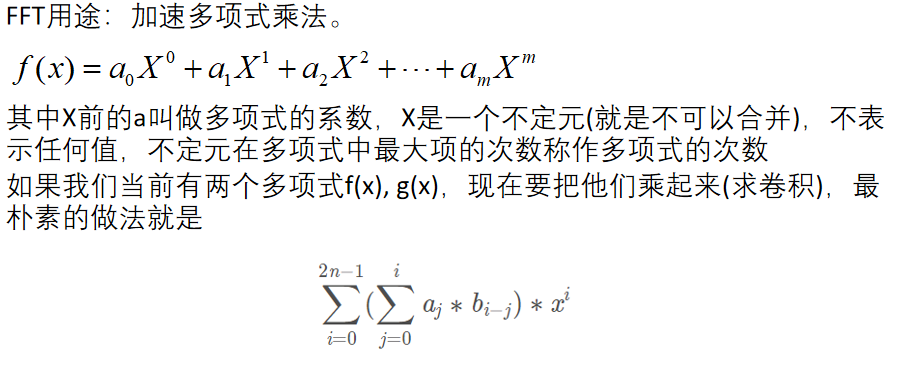

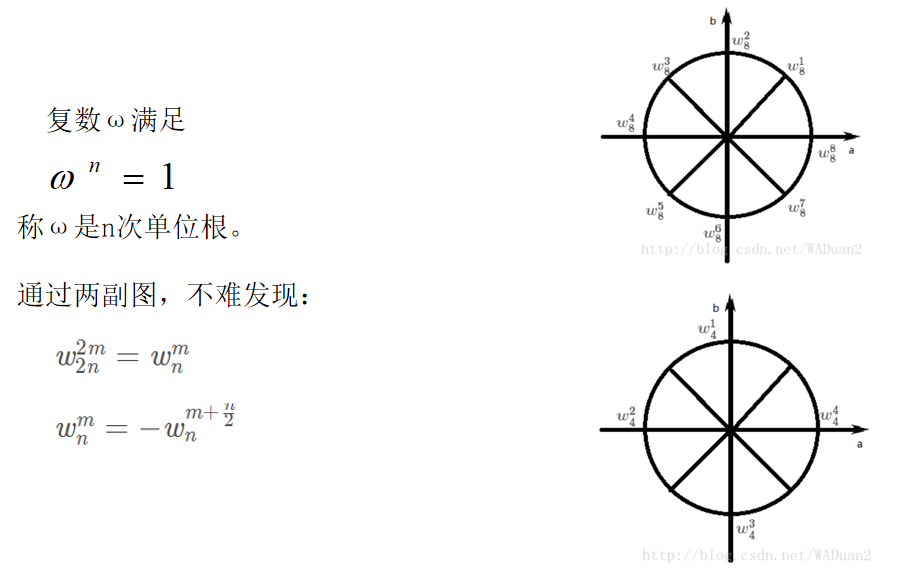

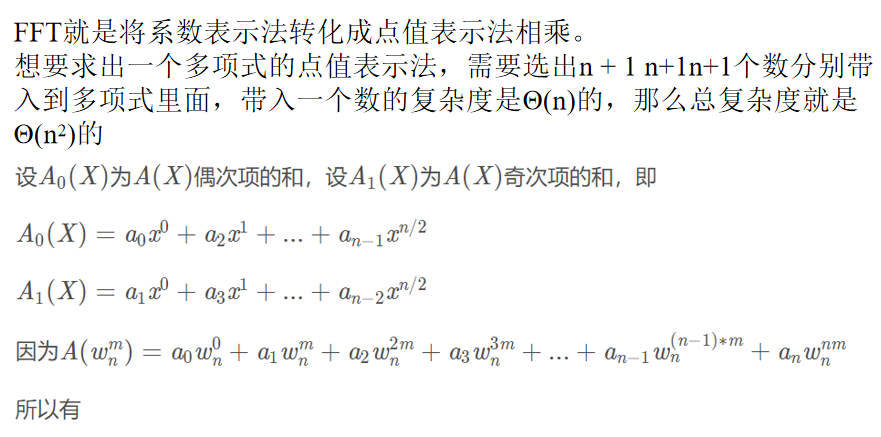

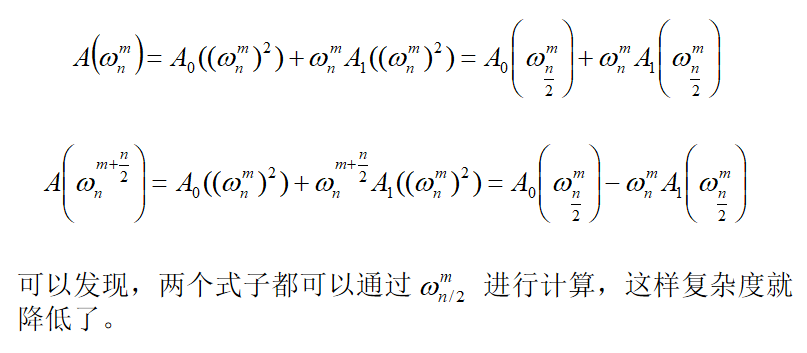

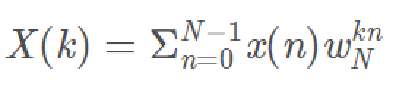

FFT与IFFT

我们从系数表示法转换成点值表示法只是为了计算卷积的时候减小时间复杂度,但最后对我们有帮助、便于分析的仍然是系数表示法。所以在对点值表示法的多项式进行卷积之后,仍需要将其再次转换回系数表示法。

这种转换方式称为逆快速傅里叶变换。

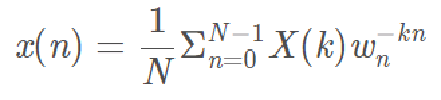

如果说FFT用公式来表示是

则IFFT用公式来表示就是

FFT和IFFT的作用就是减少卷积运算的时间复杂度。

MIMO技术的实现

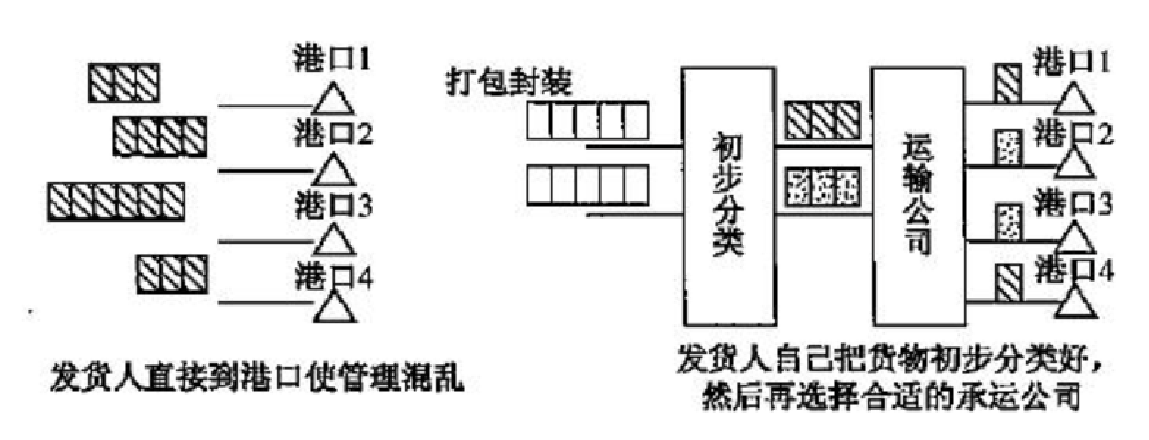

把货物运送的港口的过程分为三个步骤:

步骤一:打包方式的选择(类似传输块TB的形成);

步骤二:根据货物的种类和去往的目的地进行初步的分类(类似层映射);

步骤三:运输公司的选择(预编码矩阵的选择)。

运输公司确定好之后,由运输公司选择港口,而发货方无须关心由哪个港口发送。

预编码是将层数据映射到不同的天线端口,不同的子载波上,不同的时隙上,以便实现分集或复用的目的。预编码过程就是空时编码的过程。从编码调制后的数据发送到天线口的过程。以公司发货过程为例,层映射就是将自己的货物初步分类,而预编码过程则是运输公司安排不同的发货方式。

预编码后的数据已经确定了天线端口,也就是说确定了空间维度的资源;在每个天线端口上,将预编码后的数据对应在子载波和时隙组成的二维物理资源(RE)上。接下来生成OFDM符号,插入CP,然后从各个天线端口发送给出去。

在接收端,通过多天线接收机将接收下来的信号,从OFDM的时频资源读取相应的数据,经过预编码与层映射逆过程,然后解调、去扰、去交织、解码,最后恢复出原始信息比特。

数据通道

数字混频(Mixer)

NCO产生方法一:查表法

将正弦值计算出来,按顺序存在表里,用相位累加值作为查表地址进行取值。将值输出与信号采样值相乘,实现移频。

优点:最有效,最简单

缺点:需要一个较大的容器存储正弦值。

NCO产生方法二:CORDIC算法

做加减以及移位实现移频。

通过一系列固定、与运算基数相关的角度不断偏摆以逼近所需要的角度。旋转后需进行一次模校正运算。

作用:产生离散的正弦波,用于后期与采样信号进行混频;简单的NCO就是通过查表法产生(存储一个周期的正弦离散值)。位宽表示产生信号精度,离散值精度比较高,得出的波形更平滑。

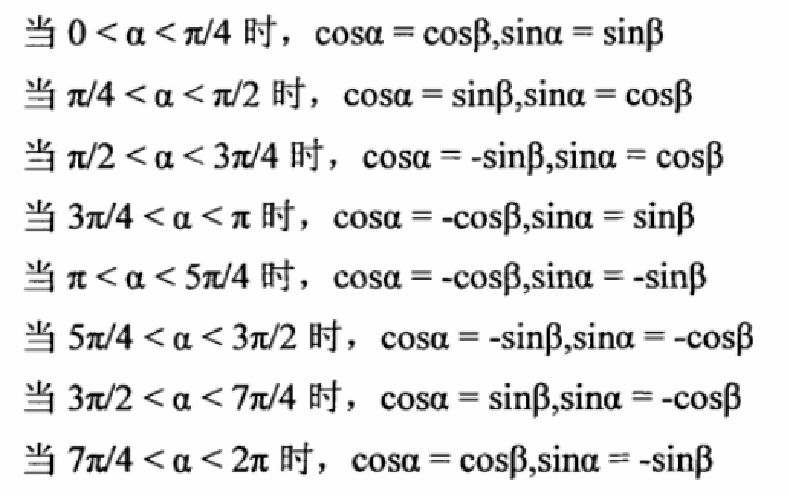

坐标旋转法:只涉及移位和加减法

因为累加器的输出角度范围[0,2π],但是CORDIC的计算范围是

[-π/2,π/2]利用三角函数的对称性,[0,2π]八分圆将角度范围映射到[0,π/4]。当α在1、3、5、7的八分圆时,β=ɵ(八分圆的绝对角度值);当α在2、4、6、8的八分圆时,β=π/4-ɵ。

最后可能需要补8个顶点。

FIR滤波器

FIR滤波器的几种实现方法先说一下:

窗函数法:用一个窗函数去乘理想单位取样响应得到,在时域内将单位取样响应加权截尾得到其逼近函数抽头。

但是没有解决在给定抽头的情况下如何设计一个最佳滤波器的问题。

由于没有精确对应抽头的窗函数,因此当不满足要求时,时通过适当调整窗函数或抽头,然后进行重复直至得到符合预期的结果。

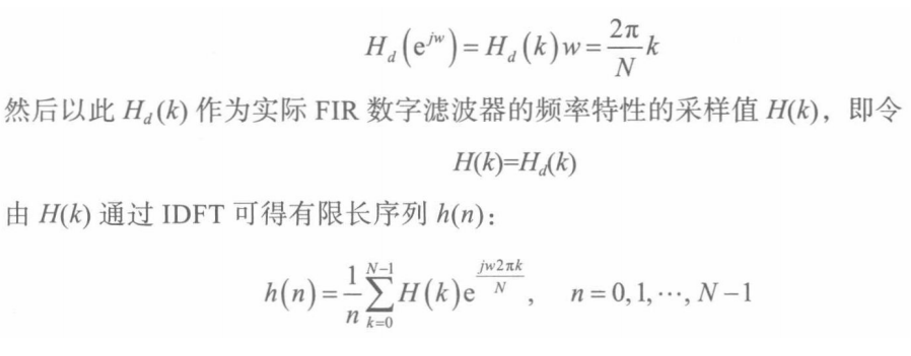

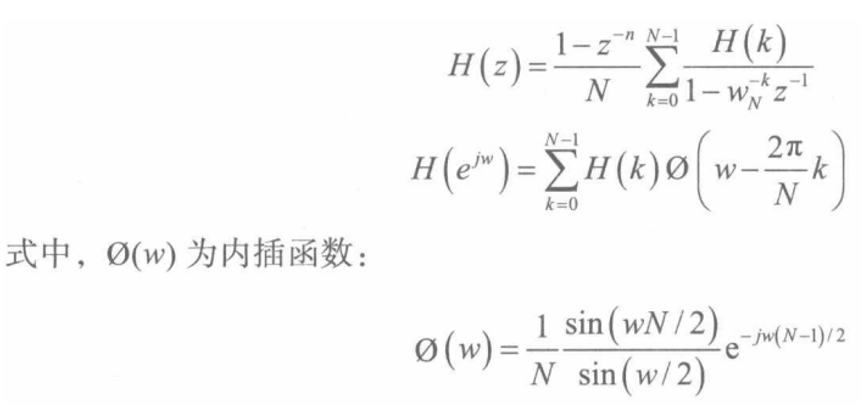

频率采样法:从频域出发,将给定的理想频率响应加以等间隔采样。

取样点内插值对滤波结果有较大影响,这种情况下需要另外做优化设计来解决。

最大误差最小化法(等波纹逼近):这种设计法与前两种比较可以使滤波器的最大逼近误差均匀分布。阶数相同时,这种设计法使滤波器的最大逼近误差最小,通带最大衰减最小,阻带最小衰减最大;指标相同时,这种设计法使滤波器阶数最低。

等波纹逼近法的设计在于找到滤波器的系数向量h(n),使得在通带和阻带内的最大绝对值幅度误差为最小。

用Hd(ω)表示希望逼近的幅度特性函数(必须满足线性相位约束条件),ε(w)为加权误差函数,W(ω)为幅度误差加权函数。

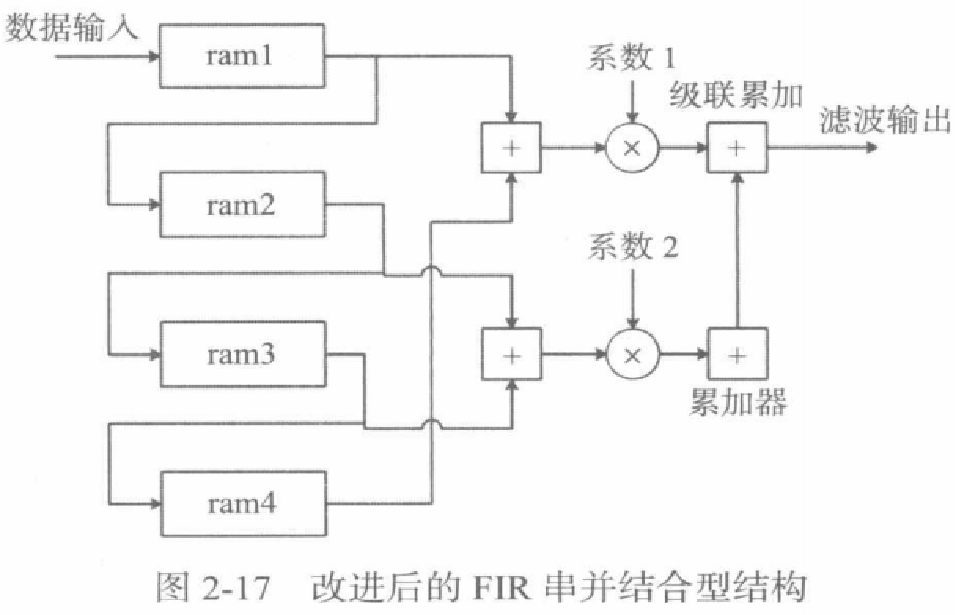

FIR滤波器串并行结构

在保证计算速度的条件下,减少资源的使用,但需要利用RAM和读写地址相互配置来实现各种顺序的数据输出。

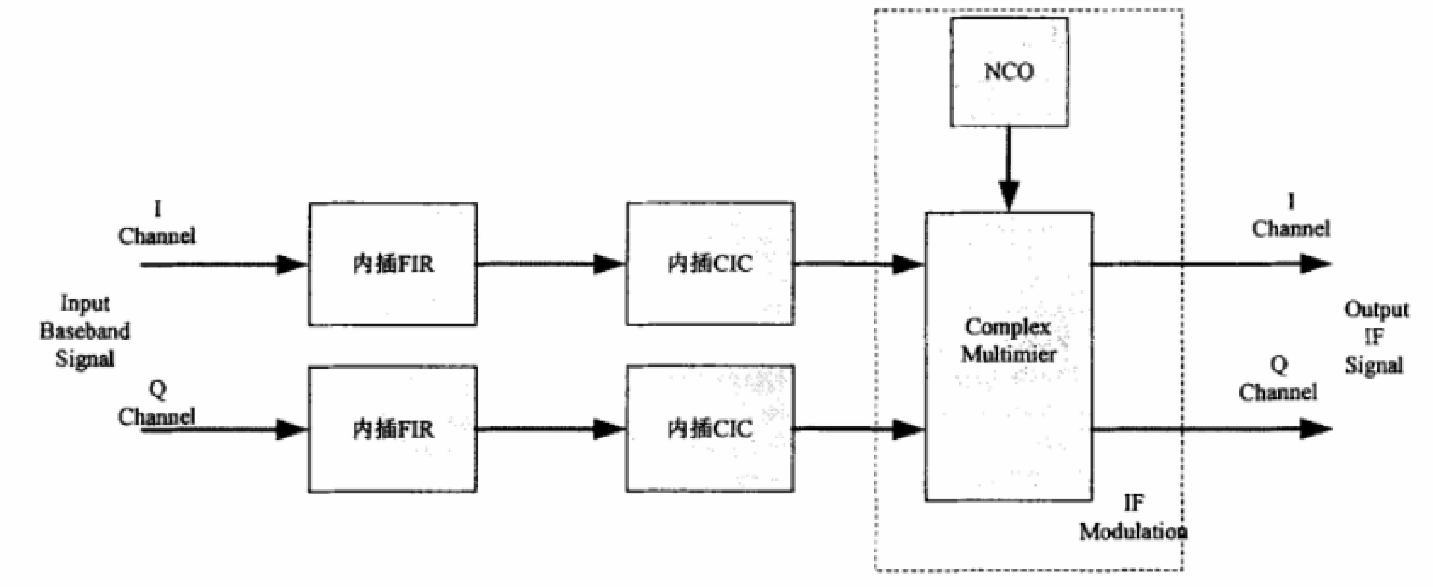

DUC(数字上变频)滤波器

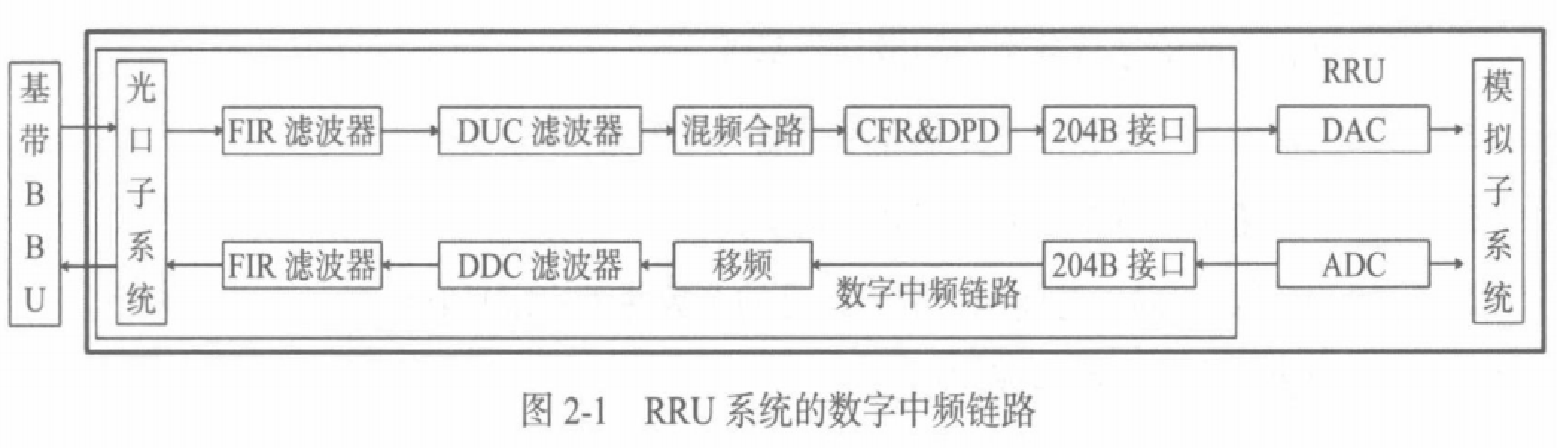

数字上变频DUC(Digital Up Converter),无线电发射链路中,数字信号经过转换成模拟信号,模拟信号经过混频后得到比原始信号高的期望的射频中心频率,然后信号经过放大到适当的功率电平,最后经过限制带宽后经天线发射出去。这种混频频率向上变化的方式叫做上变频。

数字上变频的实现方法一般为将I/Q两路基带信号,通过内插滤波,变为较高速率的基带信号,再通过数字混频器分别对两路信号进行调制输出中频信号。完成对输入信号的频谱搬移,生成调制后中频信号。

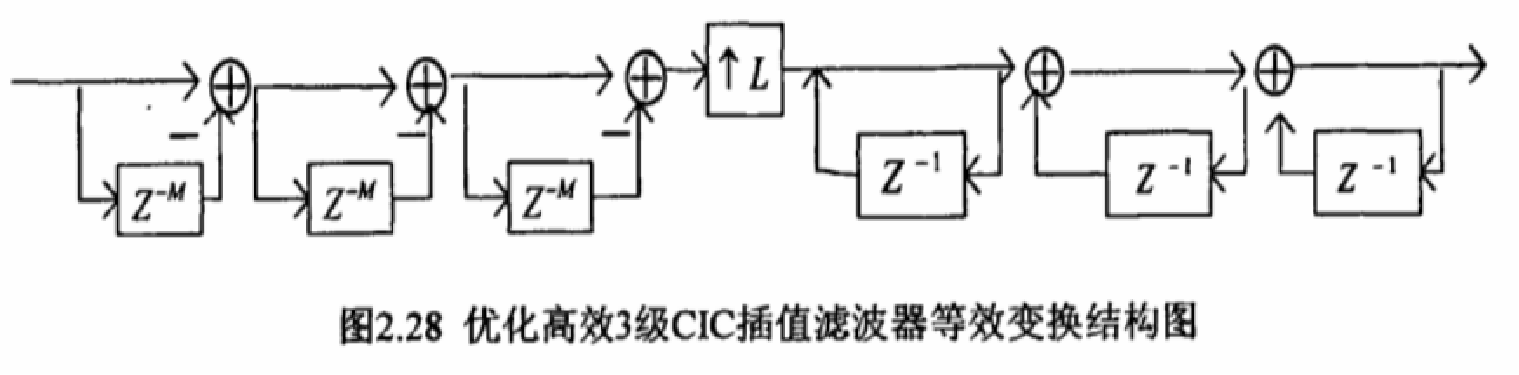

由于内插后,频谱的周期会变成原来的1/T,因此在数字坐标轴上会产生重复的波形,称为镜像。所以对序列进行内插时,要想保持原始的频谱特性不变,需要添加低通FIR滤波器以消除镜像频谱。

对于插值器来说,为了提高效率,通常将积分器放在梳状滤波器之后,使积分器工作在高采样频率,而梳状滤波器则工作在插值前的低采样率下。

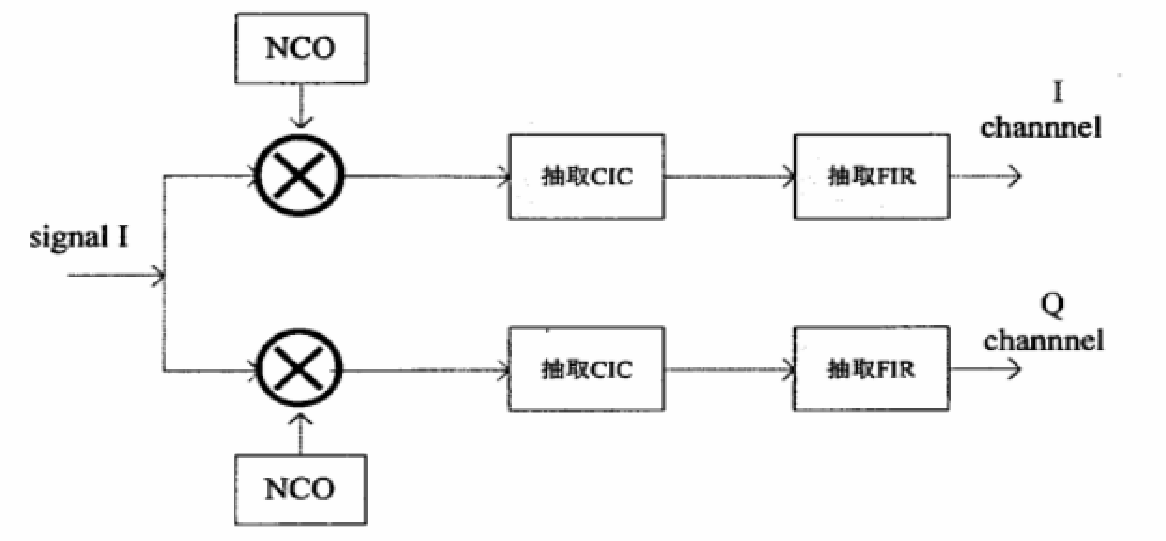

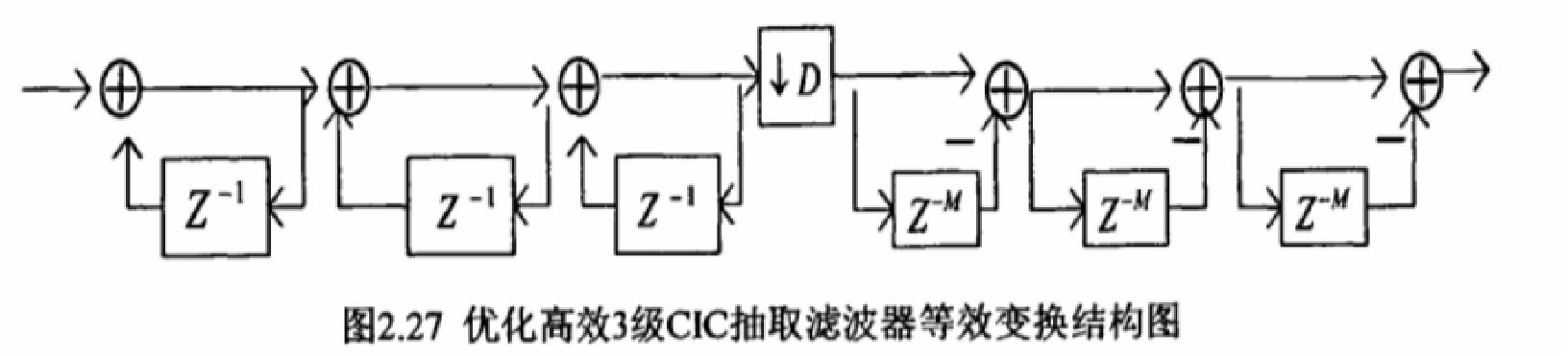

DDC(数字下变频)滤波器

DDC的主要目的是经过数字混频将AD采集的中频(IF)数字信号频谱下变频到基带信号,然后完成抽取滤波恢复原始信号,它包含采样、正交变换、数字滤波、抽取算法。主要的电路模块由四部分组成:数控振荡器NCO、数字混频器、抽取、数字滤波器。

DDC主要由数字控制振荡器(NCO) 、混频器(mixer) 、滤波器(filter)等部分组成 , DDC是将中频信号与数字控制振荡器产生的载波信号进行混频 ,再经过低通滤波器得到基带信号 ,实现了下变频功能。

数字下变频的基本原理就是把输入信号与本地振荡信号相乘, 将射频信号通过混频, 搬移到中频段, 再进行 ADC采样。

DDC的核心是将中频 A /D 采样信号与 DDC中的数字控制振荡器 (NCO )产生的本地数字中频载波信号进行混频 ,将中频信号下变频到基带。

为了抗混叠,在抽取前会加上低通滤波器,当抽取倍数为2时,添加的滤波器一般为半带滤波器。半带滤波器是一种特殊的低通FIR滤波器,这种滤波器由于通带和阻带相对于Nyquist频率的一半对称,因而有近一半的滤波器系数为零,同时,一般在设计时,都会选择系数为2的抽取因子,这样可以会大大减少滤波器的运算量。后面的低通滤波器主要的作用就是为了防止抽取滤波器进行频率抽取造成的频谱混叠。

实现高效抽取时,通常将后面的抽取器提到梳状滤波器之前,使得积分器工作在高采样率下,而梳状滤波器工作在抽取后的低采样率下。

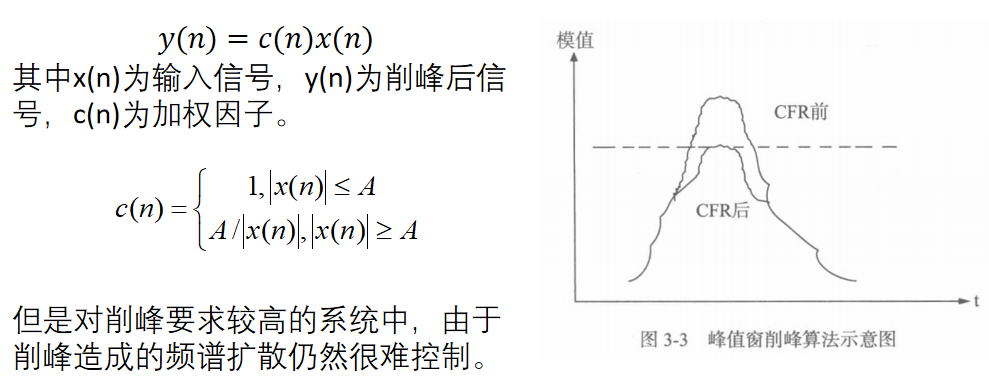

CFR(Crest Factor Reduction)算法

峰值窗削峰

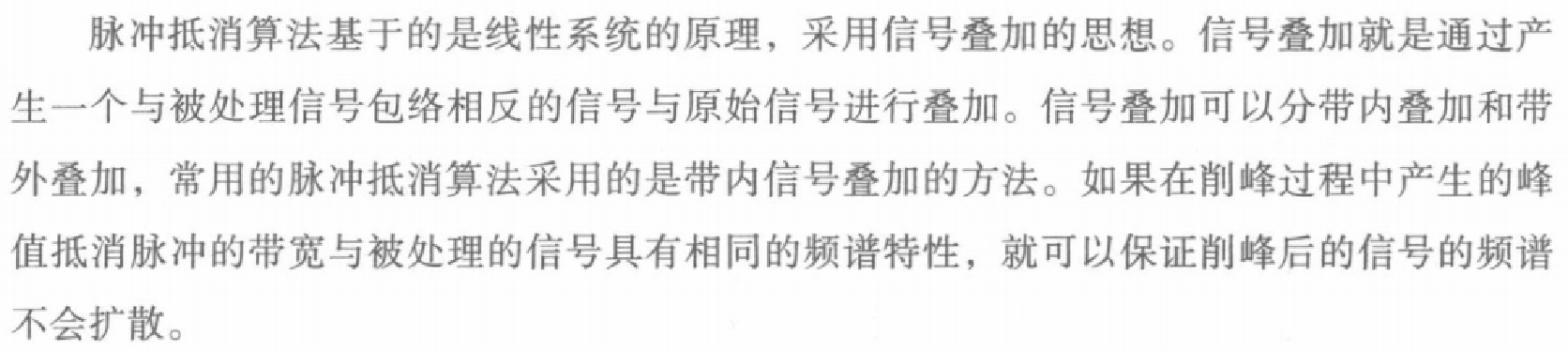

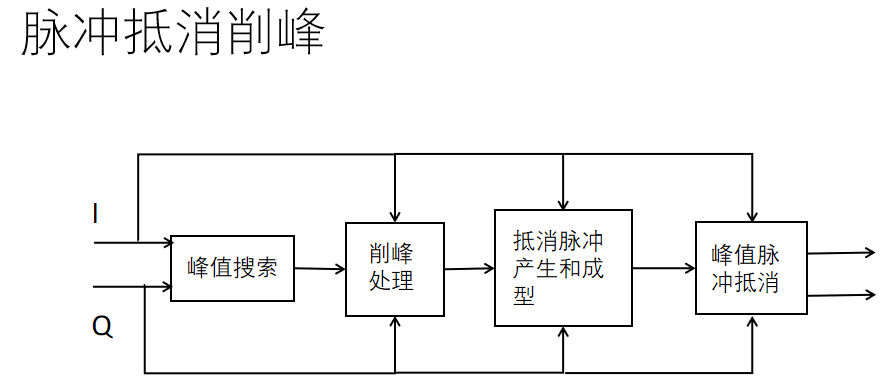

脉冲抵消削峰

1、峰值搜索主要完成对信号包络峰值的判断

2、削峰处理模块主要完成对原始信号的削峰功能

3、抵消脉冲产生和成型模块完成抵消脉冲的产生和抵消脉冲的成型

4、峰值脉冲抵消模块完成最终的峰值抵消处理

脉冲成型主要是通过滤波器实现的:

1、滤波器在固定频点的频响是否有足够的抑制

2、滤波器的通带和止带跟输入信号的频谱相关

3、根据削峰的性能、EVM等要求,确定滤波器的抑制

4、硬件资源开销和性能的综合设计优化

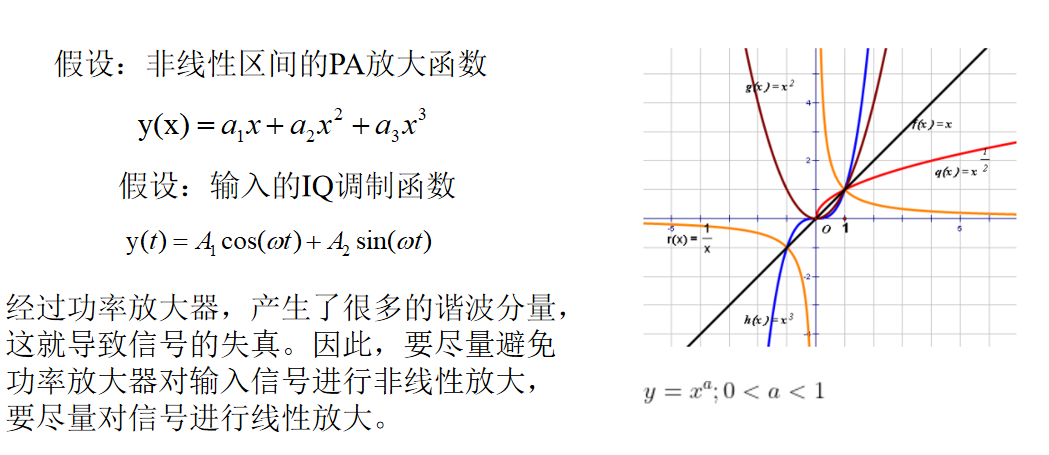

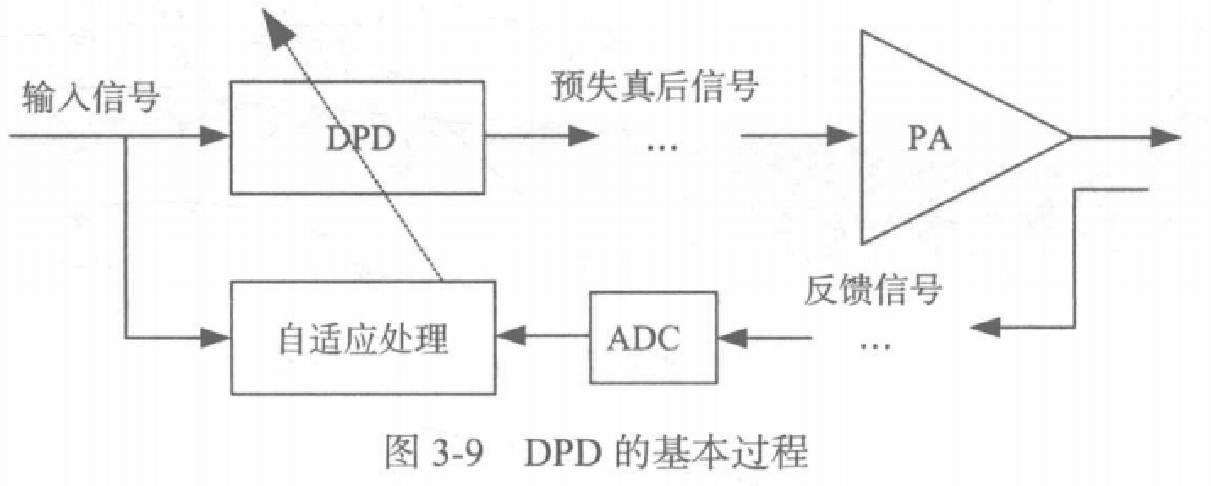

DPD(Digital Pre-Distortion)算法

服务对象:射频功率放大器

作用:改善功放的线性,提高发射信号的质量

关键技术:反馈信号处理、数据预处理技术、预失真模型建立、预失真参数求解等。

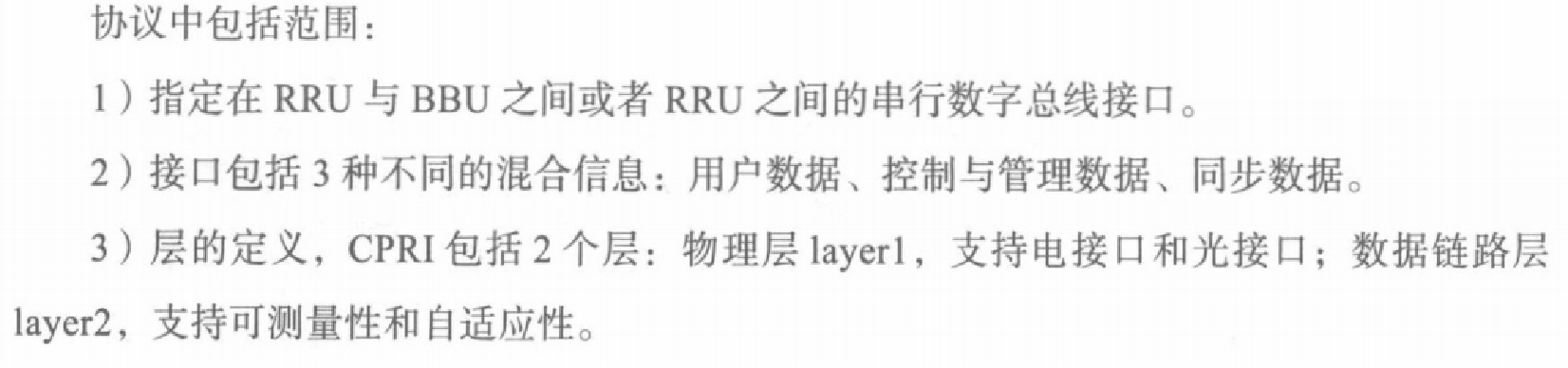

DPD在数字域对功放的失真进行预处理,通过在数字域建立起功放的逆模型,最终信号通过数字预失真器和功放后失真被抵消,从而达到改善功放失真的目的。

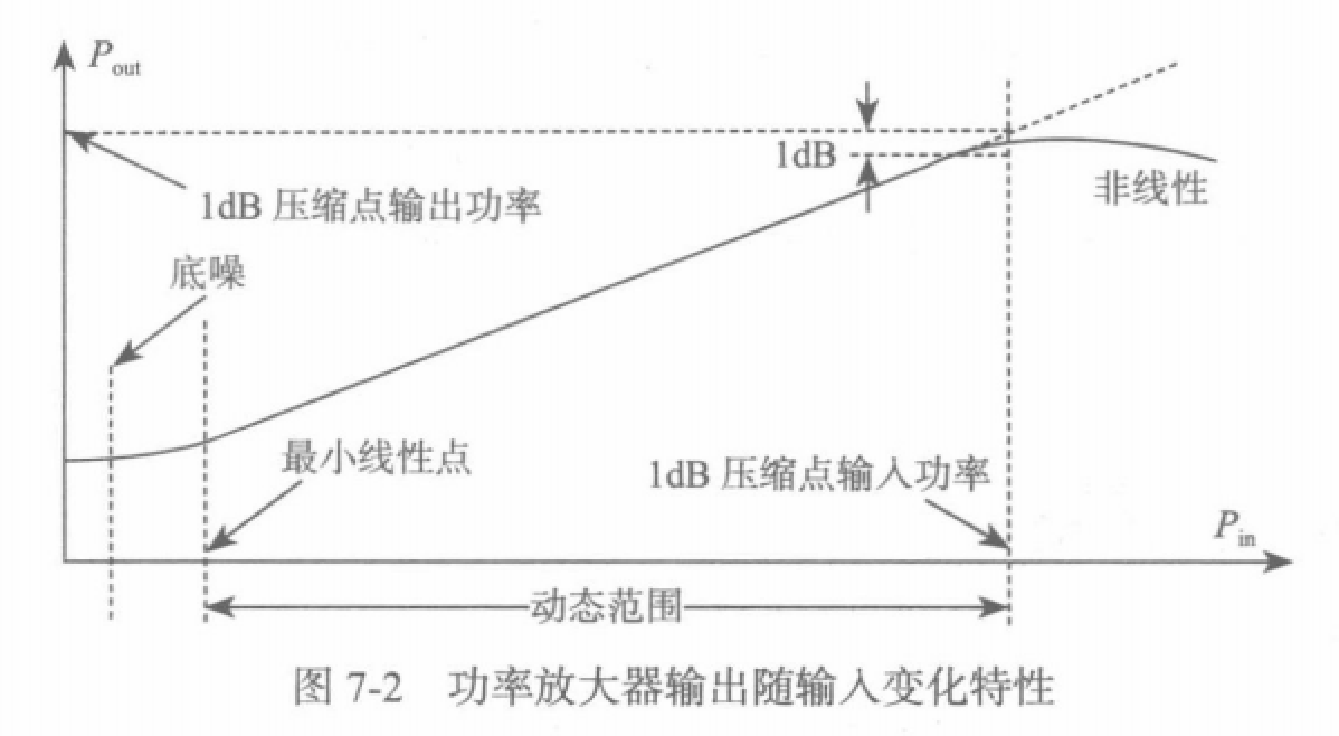

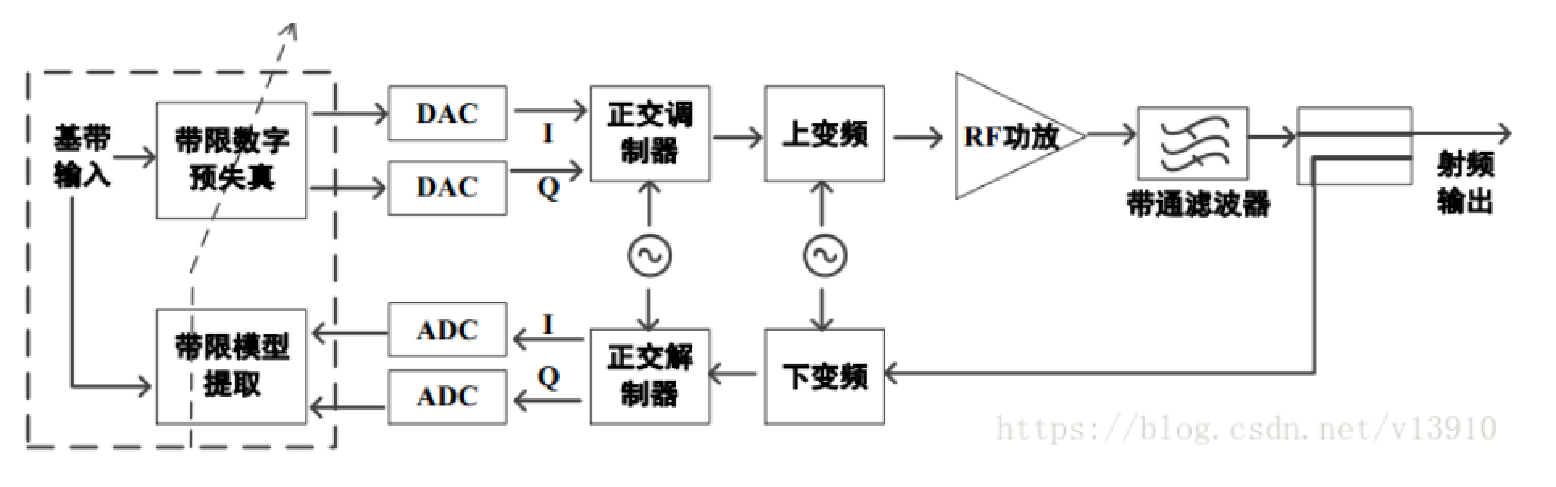

数字预失真DPD与PA(功率放大器)

为什么要通过数字预失真技术,使一个正常的信号失真呢?

当功率放大器的输入功率加大到某一值后,输入和输出之间不再是线性关系。此时再增加输入信号的功率,虽然可以增大输出功率,输出功率的增加远低于输入功率的增加,即输出功率效率下降。

更重要的是,在非线性区,输出信号与输入信号不再是线性放大的关系,导致信号失真!

要尽量避免功率放大器对输入信号进行非线性放大,要尽量对信号进行线性放大。

如果直接让信号工作在线性区,确实不会引起这些问题。但是实际的通信系统面临如下的问题:信号的幅度变化较大,峰均比(信号峰值与信号均值的比值)比较高,这就意味着即使信号均值落在线性区,信号的峰值也有可能落在非线性区。

如果信号峰值和均值都落在线性区,这功率放大器的利用率就很低,大部分时间工作在低功率区,对功率放大器是很大的浪费,功率放大器的线性区间越宽,价格越贵,并且价格相差很大。

移动通信系统中,要增加信号的覆盖区,需要增大发射功率。

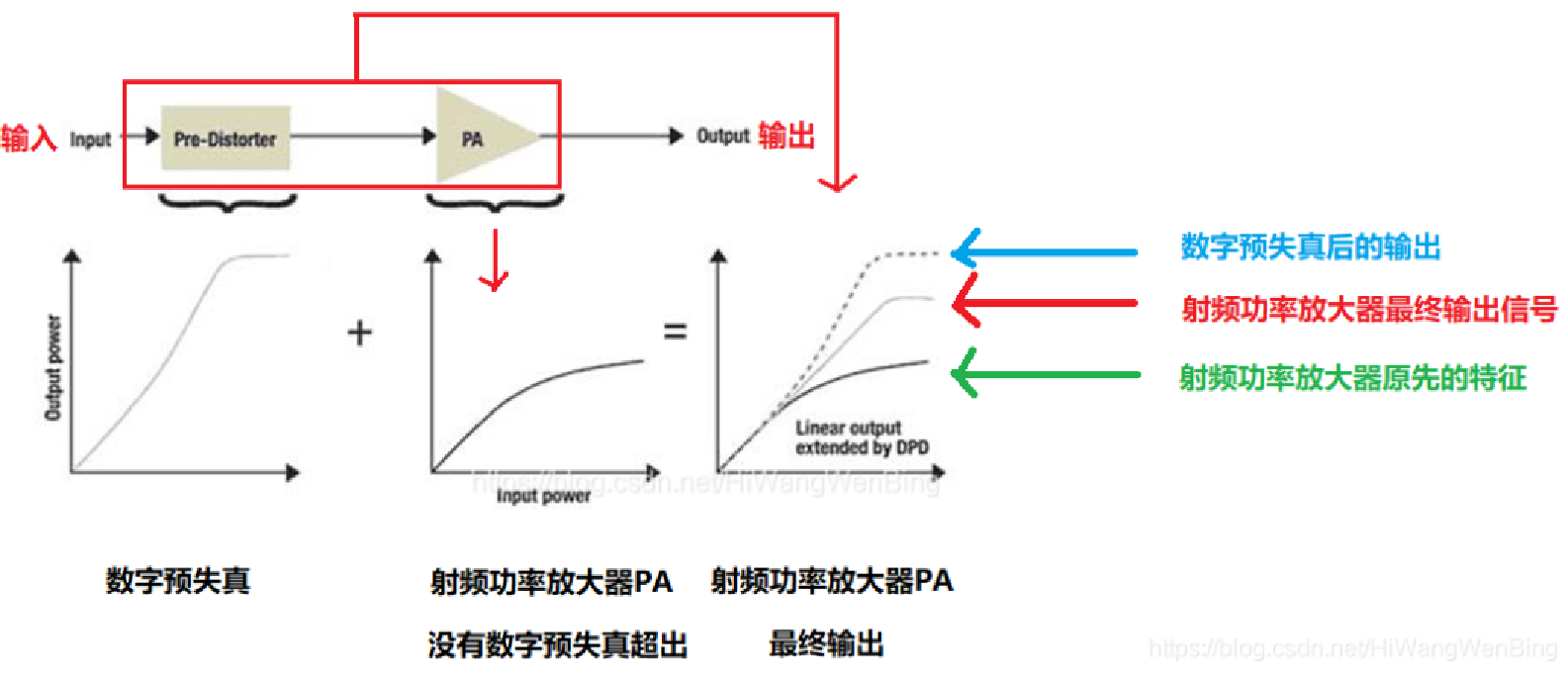

所以在系统中加入了数字预失真DPD和削峰CFR。

采集功放输出后的中频信号,并与输入信号进行处理,得到功放的预失真参数,并对输入信号进行预失真处理,提高功放的线性指标。DPD数学模型和参数需要完全匹配当前PA的模型,当PA变化后,DPD数学模型或参数也需要相应的改动。

下图是反馈链路的详细系统框图

图中提到了一个带限模型,这里说一下带限系统是个什么样的东西。

“带限”系统就是带宽有限制的系统,在射频通信系统中,影响带宽的一个重要的因素就是DAC,即数模转换器。

ADC需要对模拟信号进行数字采样,而采样就涉及到采样频率,采样频率与模拟信号的带宽直接的关系。举例,假如输入信号带宽为100MHz,5阶模型对应的带宽就是500MHz,根据奈奎斯特采样定理,则ADC采样率需要达到1G。

“带限”系统中,在DPD与功率放大器PA之间,增加了一些组件,如DAC功能模块,会导致系统的输入信号的带宽受到了极大的限制,不可能无限带宽。如LTE的带宽为20M, 5G NR的带宽在400M等。

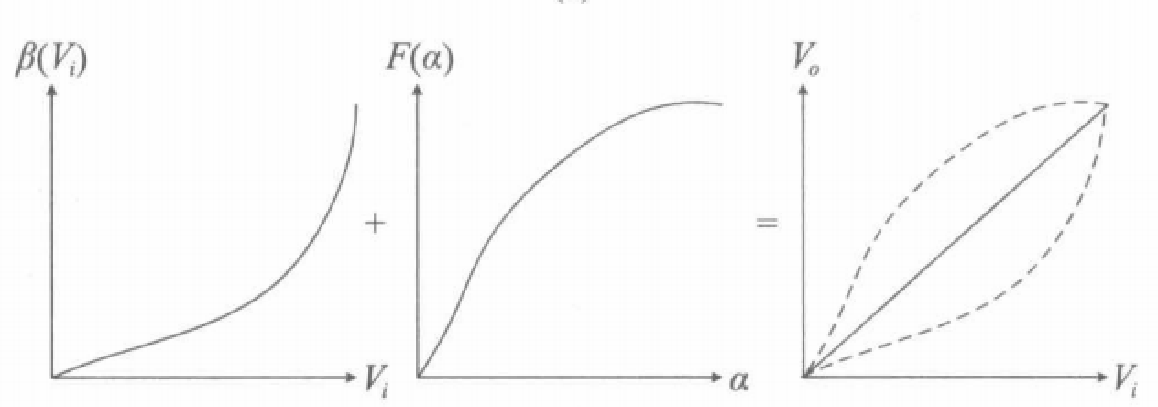

理想的DPD效果图如下:

将功放输入信号首先通过功放特性F(α)的反函数β(V)进行预失真处理,通过预失真使得功放失真得到抵消,从而提高功放输出的线性指标。

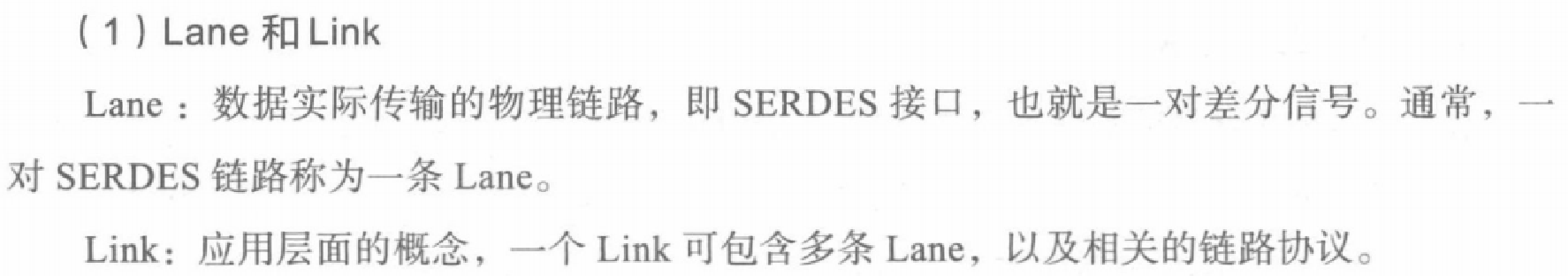

JESD204B接口协议

子类1使用SYSREF同步,子类2使用SYNC进行同步。只有子类1和子类2支持确定性延迟–发送端到接收端之间的链路延迟固定。

SYNC接口:在subclass1中,主要用于接收端发起同步请求,SYNC信号应与接收器件的帧时钟同步,SYNC为低电平有效。

SYSREF:在subclass1中,SYSREF用于确定一个统一的Device Clock,使本地的多帧时钟与帧时钟相位与Device Clock对齐。

链路同步步骤:

1、代码组同步(CGS)

2、初始化链路同步(ILAS)

3、正常数据传输

完成链路同步所需的信号有系统参考时钟(设备时钟)、至少一组CML物理信号连接(a lane)以及同步信号(SYNC~和可选的SYSREF)。以上所需的信号根据JESD204B子类的不同会不一样:

1,子类0需要设备时钟、lanes、SYNC~

2,子类1需要设备时钟、lanes、SYNC~、SYSREF

3,子类2需要设备时钟、lanes、SYNC~

代码组同步阶段(CGS):

1、Rx通过驱动SYNC拉低向TX发出同步请求。

2、Tx连续传输/K28.5/字符(10位/字符)。

3、当Rx接收到至少4个连续的/K28.5/符号没有错误,然后Rx驱动SYNC引脚拉高。否则同步失败,链接保留在CGS阶段。

4、当所有的接收端器件撤销同步请求后,发送端器件仍继续发送/K/码,直到下一个LMFC边界(本地多帧时钟)。

5、CGS阶段结束,ILAS阶段开始。

初始通道同步(ILAS):

1、在JESD204B中,发送模块捕捉到SYNC~信号的变换,在下一个本地多帧(LMFC)边界上启动ILAS。

2、ILAS主要对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据流中的位置。

3、ILAS由4个多帧组成。每个多帧最后一个字符是多帧对齐字符/A,第一,三,四个多帧以/R字符开始,以/A字符结束。接收器以各通道的最后一个字符/A对齐接收器内各通道内各多帧的末尾。

4、这些特定的控制字符只用于初始通路对齐序列中,而不用在数据传输的任何其他阶段。CGS和ILAS阶段不加扰。

5、RX模块中的FIFO吸收信道偏移。

lane同步:

发射时,lanes信号的同步是指:在SYNC信号没有拉高之前会缓存到一个类似寄存器的缓存器中,且当SYNC拉高后根据缓存情况(所有线的多帧的第一个帧开头都缓存下来后),在确定性延时结束后且,在SYNC拉高后的第一个LMFC时一起发送数据(从多帧的一个帧的帧头开始往外发)。

接收时,lanes信号的同步是指:在SYNC信号没有拉高之前会缓存到一个类似寄存器的缓存器中,且当SYNC拉高后根据缓存情况(所有线的多帧的第一个帧开头都缓存下来后),在确定性延时时间满了后在LMFC时接收到第一个多帧的第一个帧的帧头开始算是有效数据。

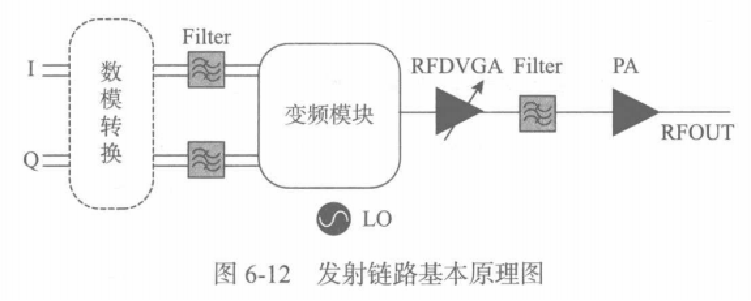

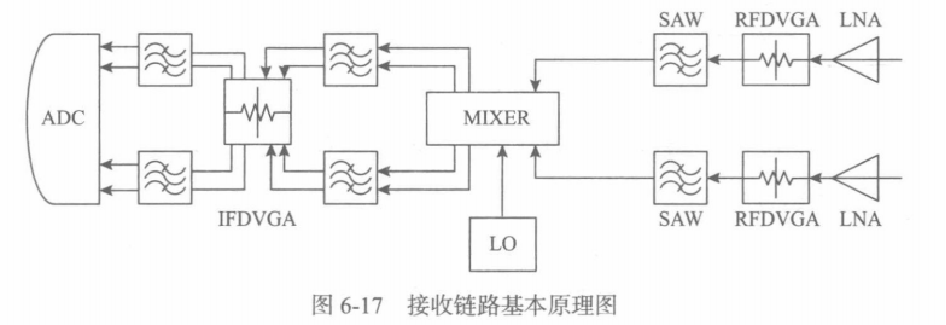

模拟信号模块

发射机:BBU下发信号经过数模转换模块转换成模拟信号,再经过滤波、变频、放大、增益控制完成模拟小信号处理后,传输给PA模块,再次滤波后经由天线发射信号。

接收机:主要对天线接收到的信号进行滤波、放大、模拟混频、模数转换,经FPGA处理后再传送给基带。

DAC数模转换器

DAC引用于RRU系统下行链路中,在接收到数据信号后,通过内部FIFO缓冲,读出后进行内插、滤波、NCO调制和IQ校准等,最终进入DAC模块转换为模拟输出。

根据发射机不同的架构,DAC输出的模拟信号也有不同,同时会具有一定的移频作用。

在DAC模块中将数字信号转换为模拟信号后,此时已经是类似电信号的模拟信号了,信号通过TX(发射机)传输到PA(功率放大)模块进行放大处理,再对信号进行滤波处理,然后与天线信号一起进入上行链路。首先要通过LNA(Low Noise Amplifier, 低噪声功率放大器),再通过RX(接收机),然后传入ADC模块将模拟信号转化成数字信号。

LNA

低噪声放大器(LNA)位于射频接收机的前端,是接收机的第一级有源电路。由级联系统的噪声可以知道,第一级电路的噪声系数会直接加到系统的总噪声系数上,所以LNA的噪声系数需要设计得尽可能低;同时为了提高接收机的接收灵敏度(无线通信增加距离),LNA需要提高足够大的增益;另外,为了减少信号放大过程中的失真,LNA需要有良好的线性度;而且通常LNA和天线之间会有一个视频无源滤波器进行滤波,该滤波器的性能对于它的负载阻抗非常敏感,所以为了得到良好的滤波特性,LNA的输入阻抗应该匹配到前级滤波器的输出阻抗。

ADC模数转换器

ADC属于RRU系统中收发信板接收通道和反馈通道的重要组成部分,ADC模块的主要作用是将模拟信号转换为数字信号输出。

根据发射机不同的架构,DAC输出的模拟信号也有不同,同时会具有一定的移频作用。

最后

以上就是积极斑马最近收集整理的关于RRU原理详解以及eCPRI+Low-Phy(一篇文章让你搞懂RRU---呕心沥血之作)CPRI与eCPRIO-RANLow-Phy数据通道DUC(数字上变频)滤波器DDC(数字下变频)滤波器CFR(Crest Factor Reduction)算法DPD(Digital Pre-Distortion)算法数字预失真DPD与PA(功率放大器)JESD204B接口协议模拟信号模块的全部内容,更多相关RRU原理详解以及eCPRI+Low-Phy(一篇文章让你搞懂RRU---呕心沥血之作)CPRI与eCPRIO-RANLow-Phy数据通道DUC(数字上变频)滤波器DDC(数字下变频)滤波器CFR(Crest内容请搜索靠谱客的其他文章。

发表评论 取消回复