龙芯3A4000处理器解读

关于3A4000的处理器结构简单做一下自己的相关分析,希望可能通过此次深入分析,更加了解处理器的结构.

文章目录

- 龙芯3A4000处理器解读

- 简介

- 3号(3A)硬件结构

简介

龙芯3A4000是一款四核处理器,采用28nm工艺制造.

目前市场上基于3A4000的PC大多数工作频率在1.8G,笔记本因考虑功耗问题,工作频率在1.5G,支持动态调频调压.

下面简要介绍与梳理下3A4000处理器内部大体构造: 未打勾的尚未理解

- 片内集成4个64位四发射超标量;GS464V(微结构)的处理器核;

- 片内集成8MB的共享Cache,分成4个体模块,每个体模块2MB,具体什么结构,下面会有结构图梳理;

- 通过目录协议维护多核及I/O DMA访问的Cache一致性;

- 片内集成2个72位带ECC的DDR4控制器;

- 片内集成2个16位的HyperTransport控制器 (简称HT);

- 每个16位的HT端口拆分成两个8路的HT端口使用;

- 片内集成2个I2C, 1个UART, 1个SPI, 16路GPIO接口.

本章重点介绍从硬件层次依照芯片架构分析多级互联以及分析端口访问.: 路漫漫其修远兮,吾将上下而求索!

3号(3A)硬件结构

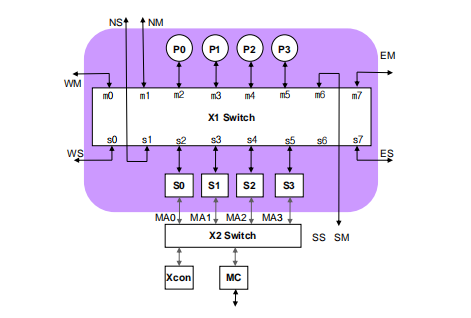

上图为3A的结点内结构:

- 在每个结点中, 最多 8*8 的X1交叉开关通过4个master端口连接4个Gs464V处理器核,通过4个slave端口连接统一编址的4个interleave共享Cache块(共8M),

- X2交叉开关通过4个master端口连接4个共享Cache,至少一个slave端口连接一个内存控制器,至少一个slave端口连接Xconf(用于配置本结点的X1和X2的地址窗口),还可以根据需要连接更多的内存控制器和IO端口等.

- 下面以3A4000芯片基于多级互联实现的真实结构为例进行 分析梳理:

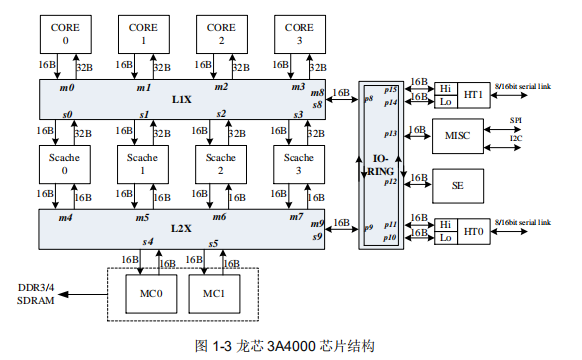

上图为龙芯3A4000芯片结构设计,基于3A硬件结构,我们对比设计需求:

- 第一级互联采用55的交叉开关,master端除了连接4个Gs464V微结构的处理器核心作为主设备,从设备除了4个共享Cache模块外,还有一组主从端口用做了IO端口用来连接IO-RING.(一个master.一个slave). 我们上述说了3A使用了88的交叉开关,目前3A4000上X1使用了5*5,master端还有3个端口,是不是可以挂载4+3=7个处理器核心呢?如果给IO端口拿走,是不是可以采取8个处理器核心呢?

- 第二级互联采用5*3的交叉开关,master端连接4个共享Cache模块,slave端目前有两个DDR3/4内存控制器,以及依旧和X1一样有一组IO端口连接IO-RING. IO: (Input and output).

- 关于IO-RING呢,不是很了解,但是我猜测应该是像SIO那样的设备或控制器,可以扩展出一堆IO,并且RING环可以轮流处理吧,在此IO-RING的介绍是,包含8个端口,根据上图可以看出分别连接了4个HT控制器,MISC模块,SE模块与两级交叉开关,正好8个端口.

- 对于龙芯平台,HT是极其重要的, IO-RING端口连接的HT控制器分别用作实现多路互联以及连接7A桥片的功能.: 4个HT控制器分成两组,每组控制器由lo/hi组成,hi/lo公用16位HT总线,所以可作为两个8位的HT总线使用,也可由lo独占16位HT总线. HT总线内集成一个DMA控制器,控制器负责IO的DMA控制器并负责片间一致性的维护.

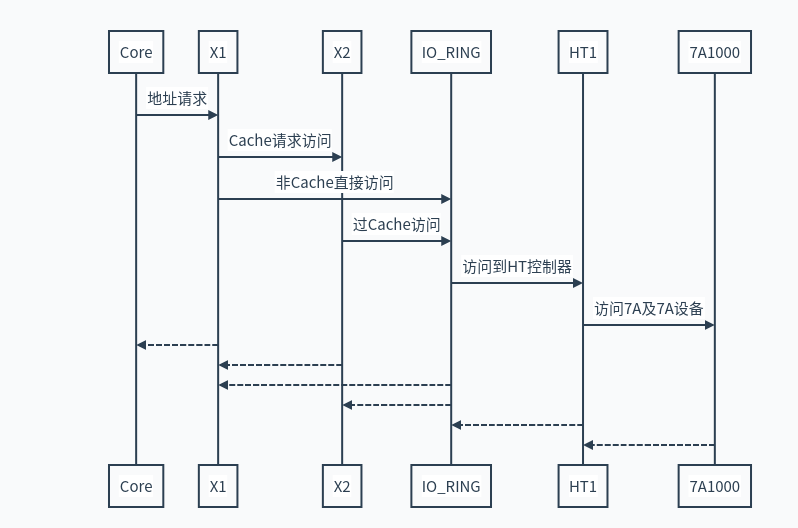

根据上述结构及描述分析,假设想访问一个设备,你应该知道数据是怎么流通的了.

目前龙芯的7A1000桥片挂载在HT1(即IO-RING连接的第二组HT控制器)上,那么如果想访问7A桥片是如何发送请求的呢?

这里面掺杂着X1和X2的路由设置,因为你得知道master端口发送来的请求是送往那个slave端口的,所以需要配置窗口以便正确命中端口.

下一次分析: 有关窗口命中及从软件层次Core如何通过一个特定的地址访问到7A设备的某个控制器

更多资料请进入资源界面进行3A4000及7A1000手册下载.

最后

以上就是知性蜜粉最近收集整理的关于龙芯3A4000处理器解读①龙芯3A4000处理器解读的全部内容,更多相关龙芯3A4000处理器解读①龙芯3A4000处理器解读内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复