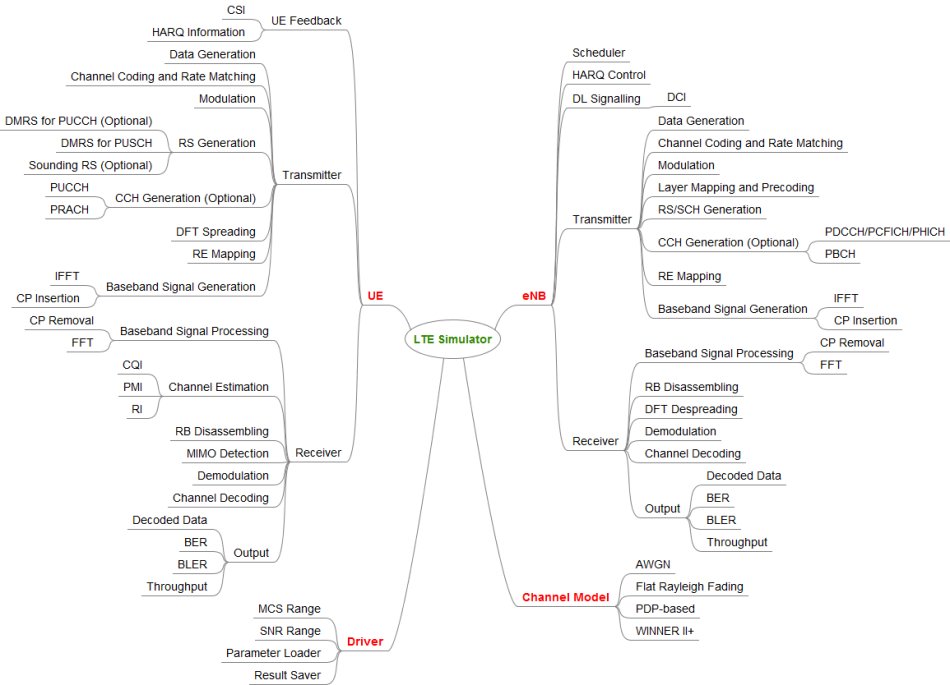

see attached picture, there are 4 modules:

(1) eNB: including tx/rx, scheduler and harq control sub-module,and also deal with DL signalling(DCI via PDCCH)

(2) UE: including tx/rx and feedback sub-module.

(3) channel model

and (4) driver: including the input MCS/SNR range, and theparameter loading module and the result saving module.

the main reference 3GPP specs are:

(1)36.211/212/213: PHY layer spec

(2)36.331: RRC spec

(3) 36.321/322/323: L2 spec

(4)36.101/104: UE/eNB RF

(5) 36.306: UE capability

etc.

最后

以上就是迷你黑裤最近收集整理的关于overall architecture of Vienna link-level simulator的全部内容,更多相关overall内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复