边缘检测,下降沿检测

代码:

reg gate_fs_d0 ; // 用于采集基准时钟下gate下降沿

reg gate_fs_d1 ; //

//边沿检测,捕获信号下降沿

assign neg_gate_fs = gate_fs_d1 & (~gate_fs_d0);

//打拍采门控信号的下降沿(被测时钟下)

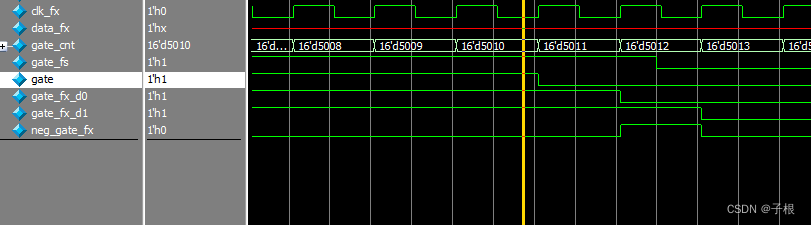

always @(posedge clk_fx or negedge rst_n) begin

if(!rst_n) begin

gate_fx_d0 <= 1'b0;

gate_fx_d1 <= 1'b0;

end

else begin

gate_fx_d0 <= gate;

gate_fx_d1 <= gate_fx_d0;

end

end信号图:

上升沿检测:

//采输入场同步信号的上升沿

assign pos_vsync = (~cam_vsync_d1) & cam_vsync_d0;

always @(posedge cam_pclk or negedge rst_n) begin

if(!rst_n) begin

cam_vsync_d0 <= 1'b0;

cam_vsync_d1 <= 1'b0;

end

else begin

cam_vsync_d0 <= cam_vsync;

cam_vsync_d1 <= cam_vsync_d0;

end最后

以上就是感动水杯最近收集整理的关于【FPGA】一些检测写法边缘检测,下降沿检测上升沿检测:的全部内容,更多相关【FPGA】一些检测写法边缘检测内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复