1、高速接口测试 用ibert

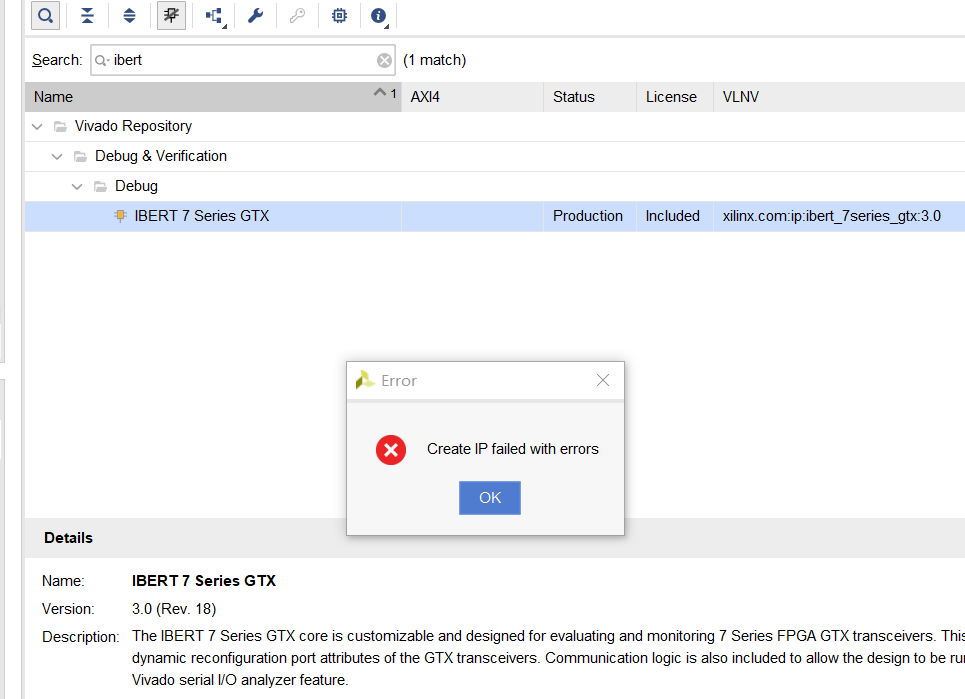

2、vivado2019.1无论如何修改片子,在例化ibert时都会报错,放弃vivado,在ise中ibert调试。

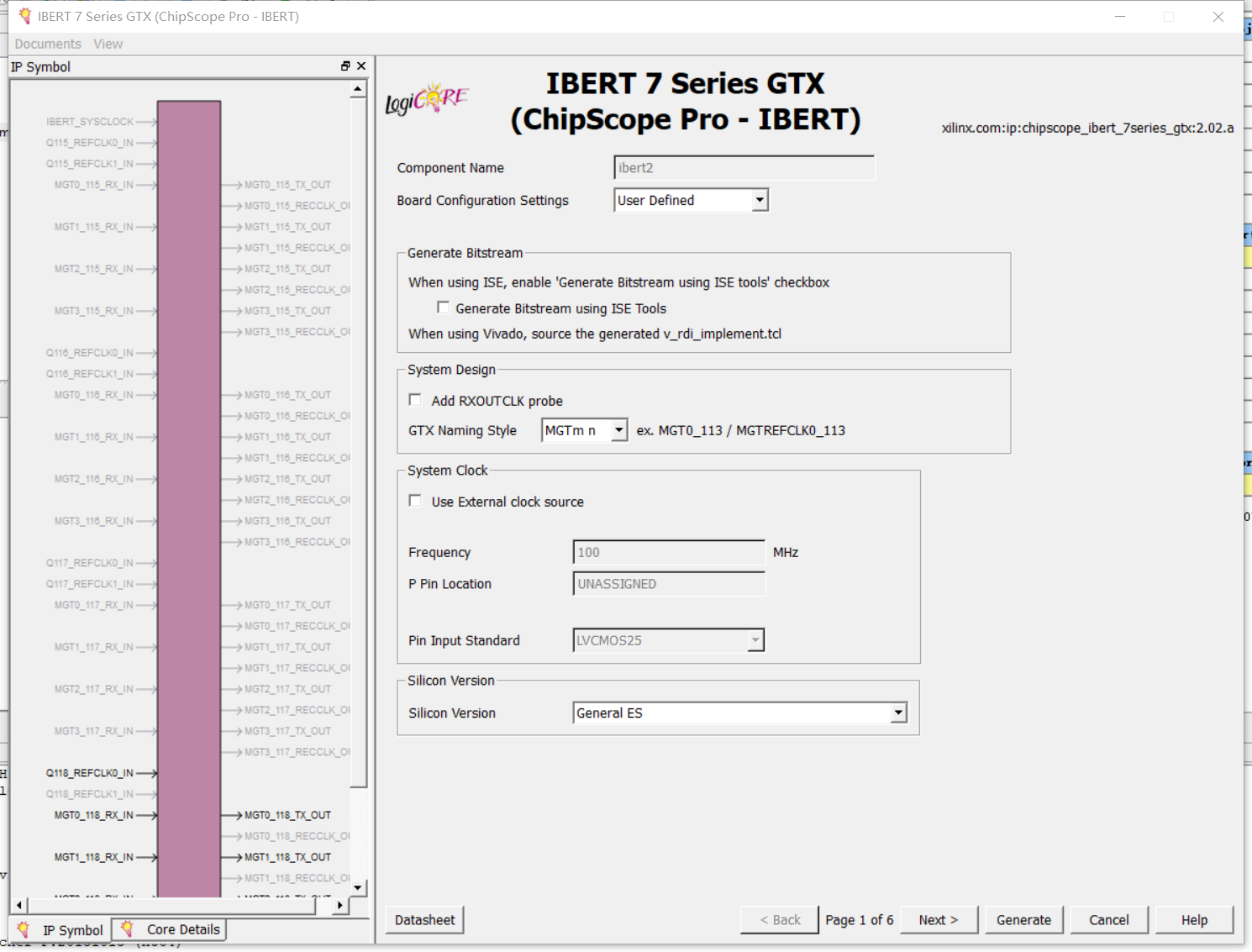

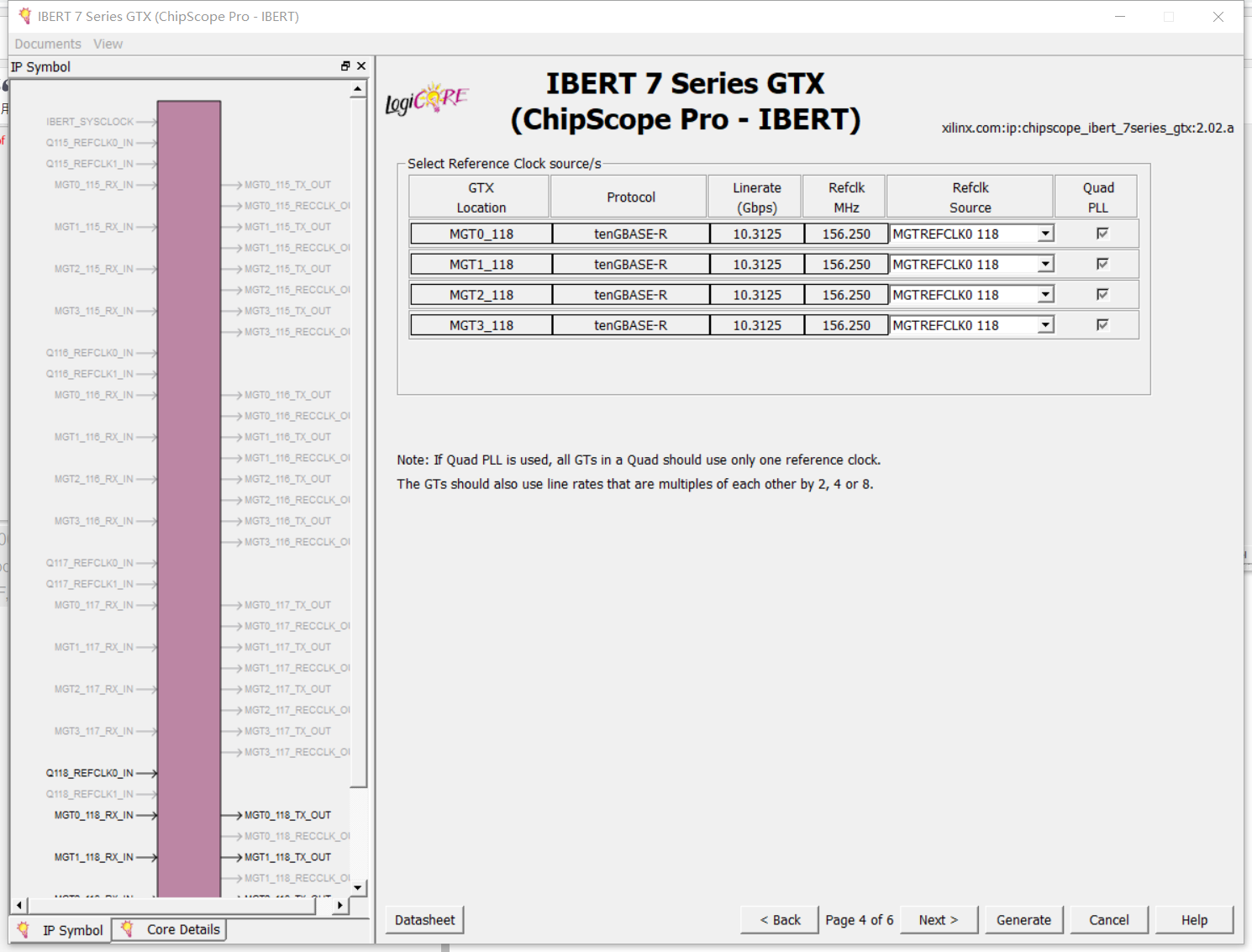

3、(1)

(2)

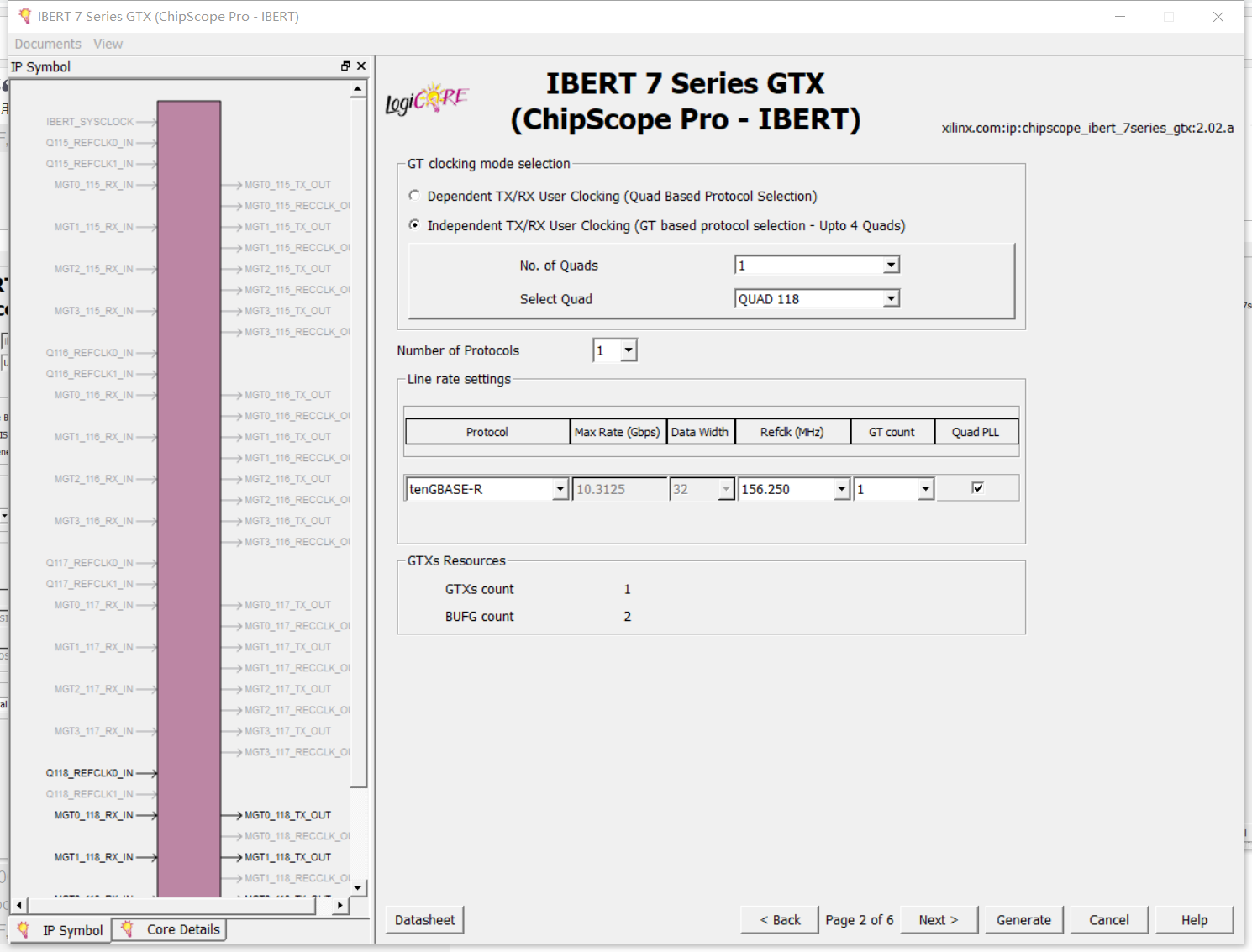

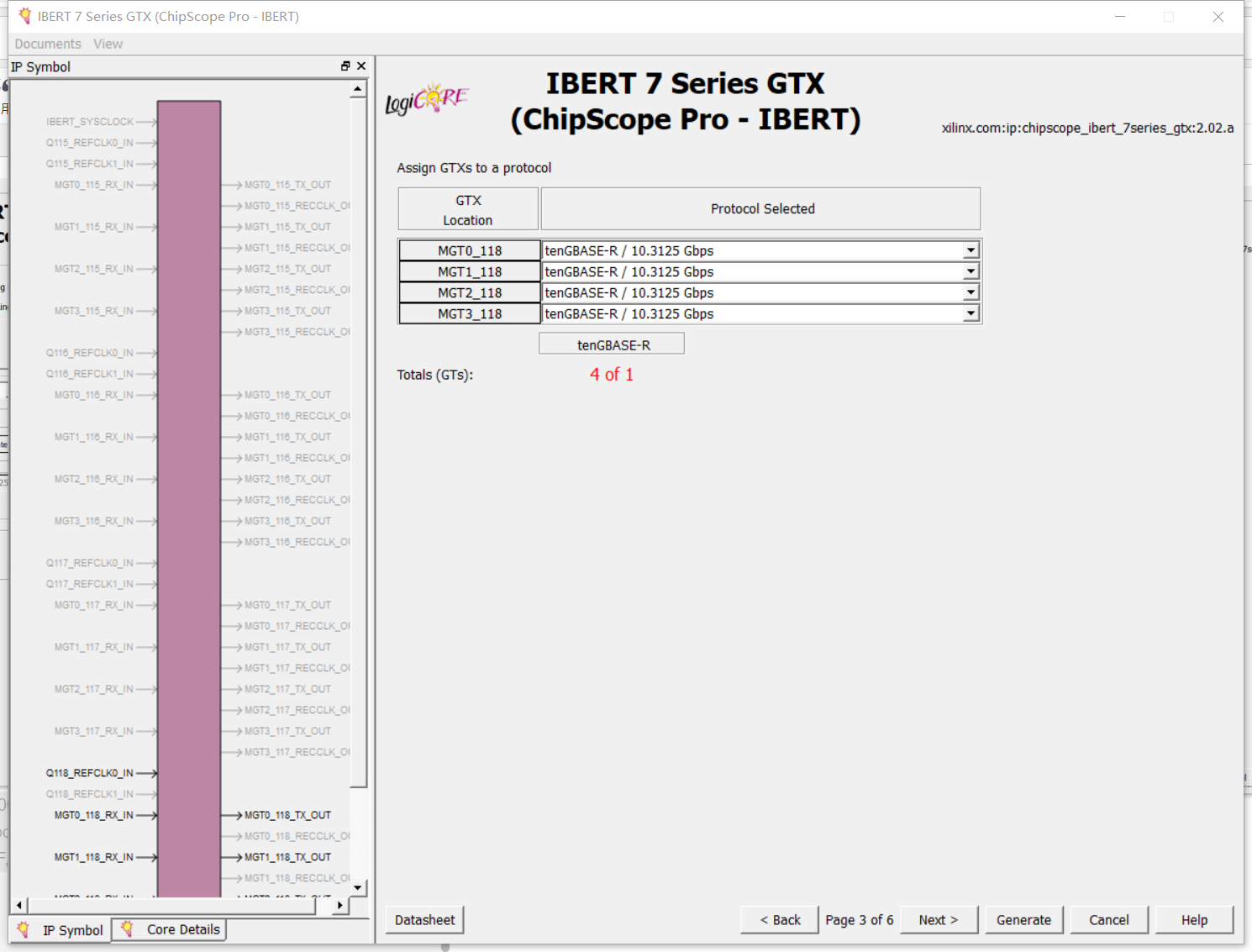

(3)

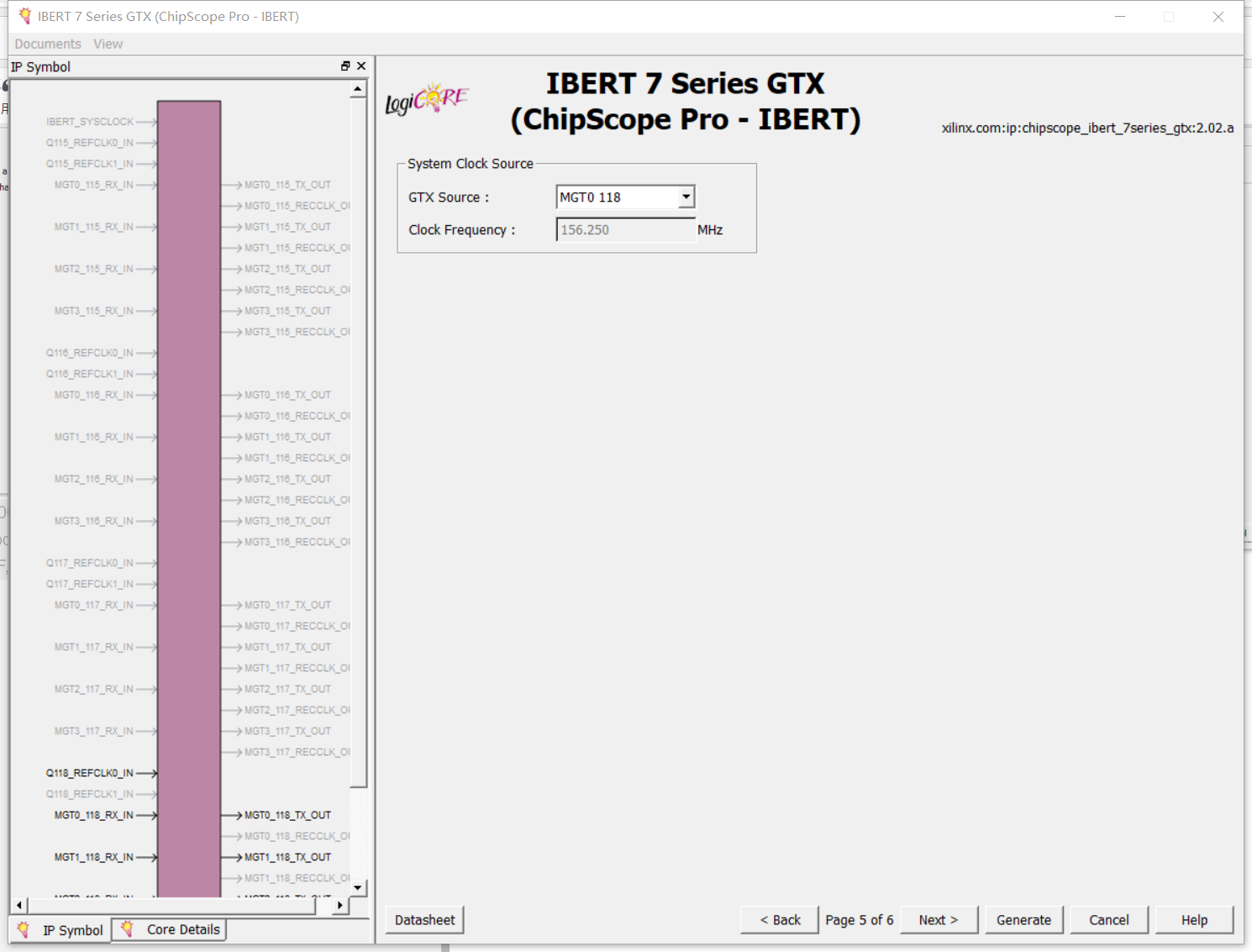

(4)

(5)

(6)等待生成完成后,关闭ISE.

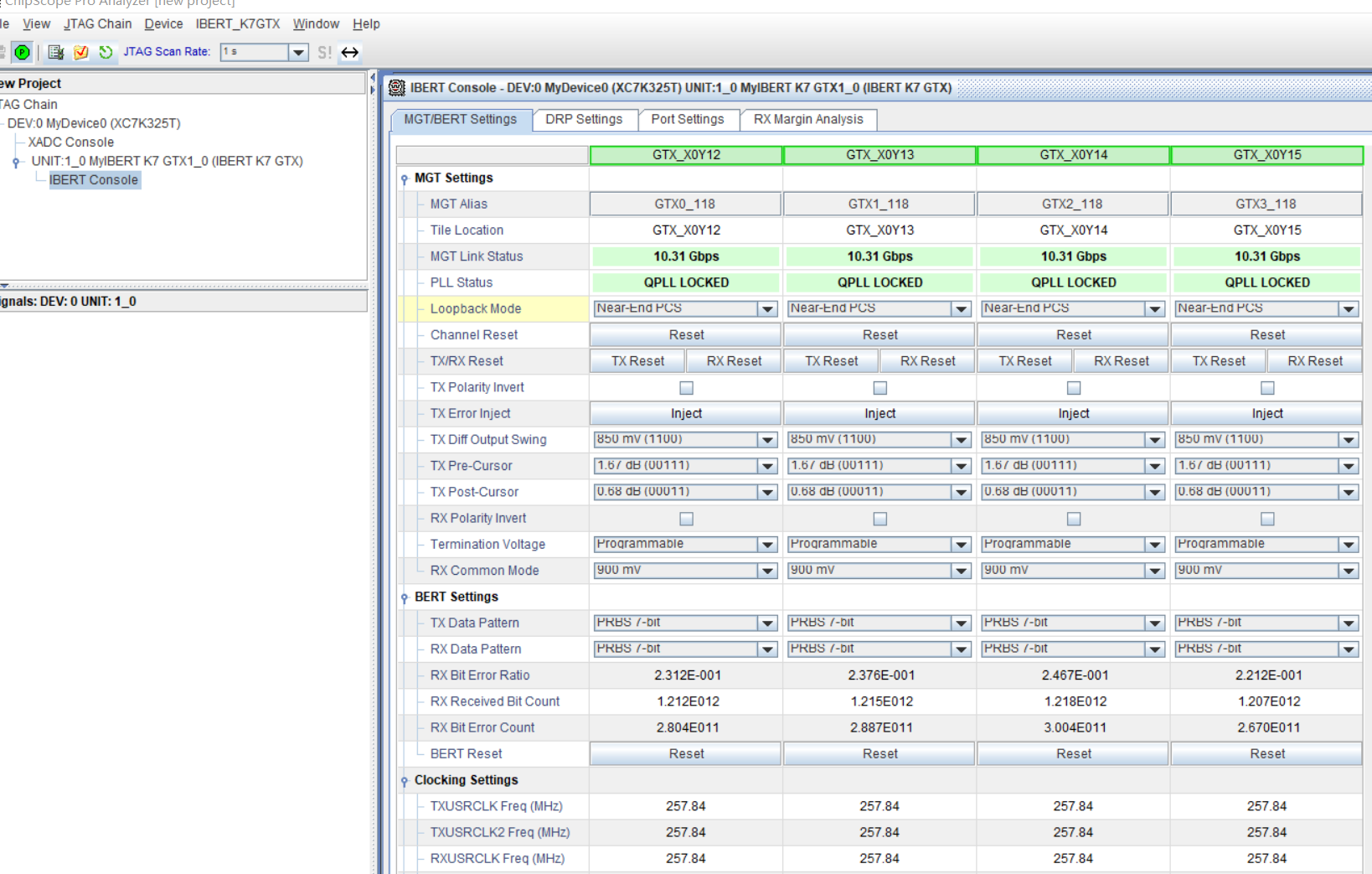

4、打开chipscope,下载example_IBERT.bit.

5、在ibert console中可以修改属性,对gtx高速接口进行测试比如回环,眼图分析等,测试比较简单,不做过多介绍。

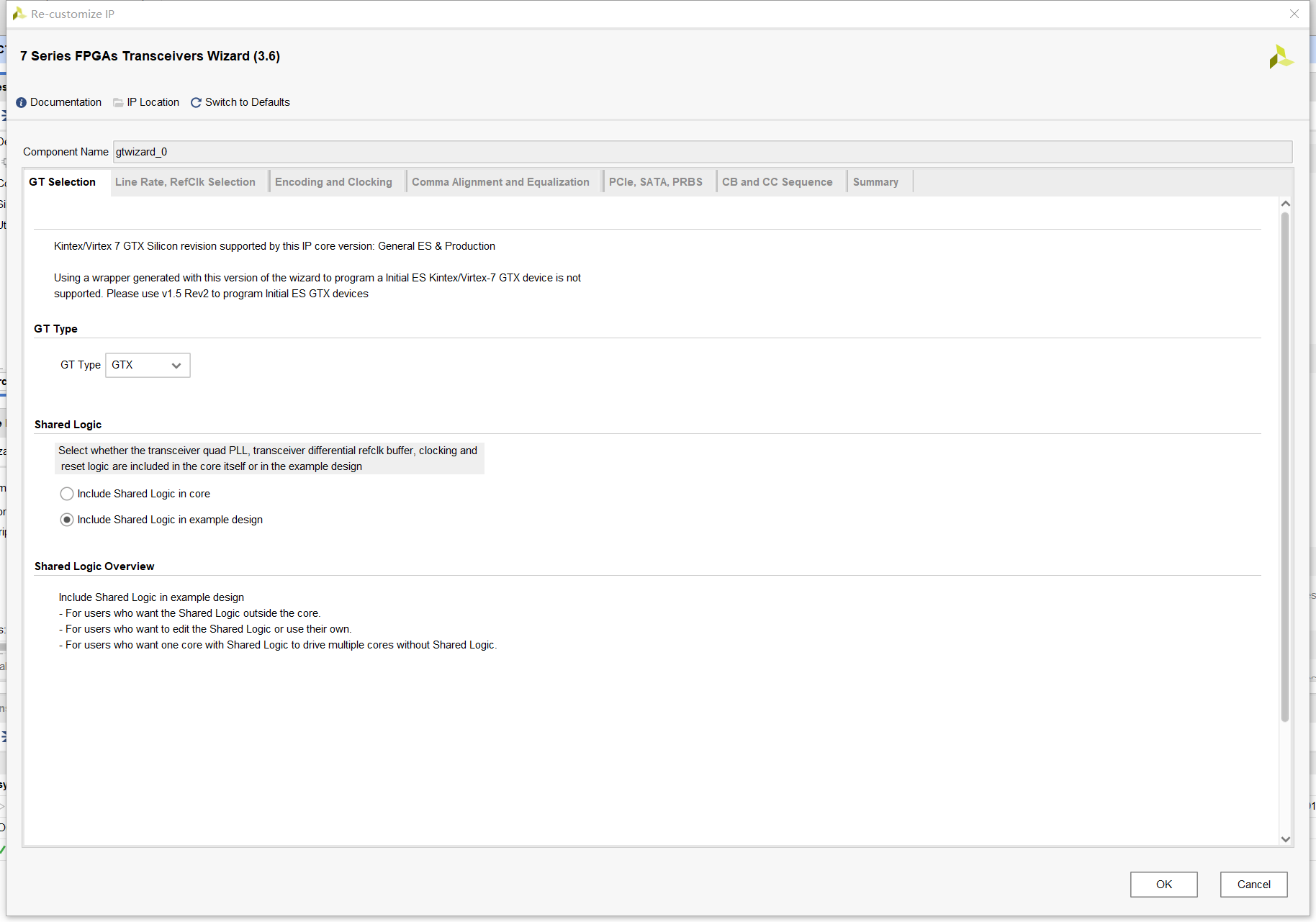

6、GTX测试,VIVADO新建GTX工程,选择 7 series FPGA Transceivers Wizard

(1)

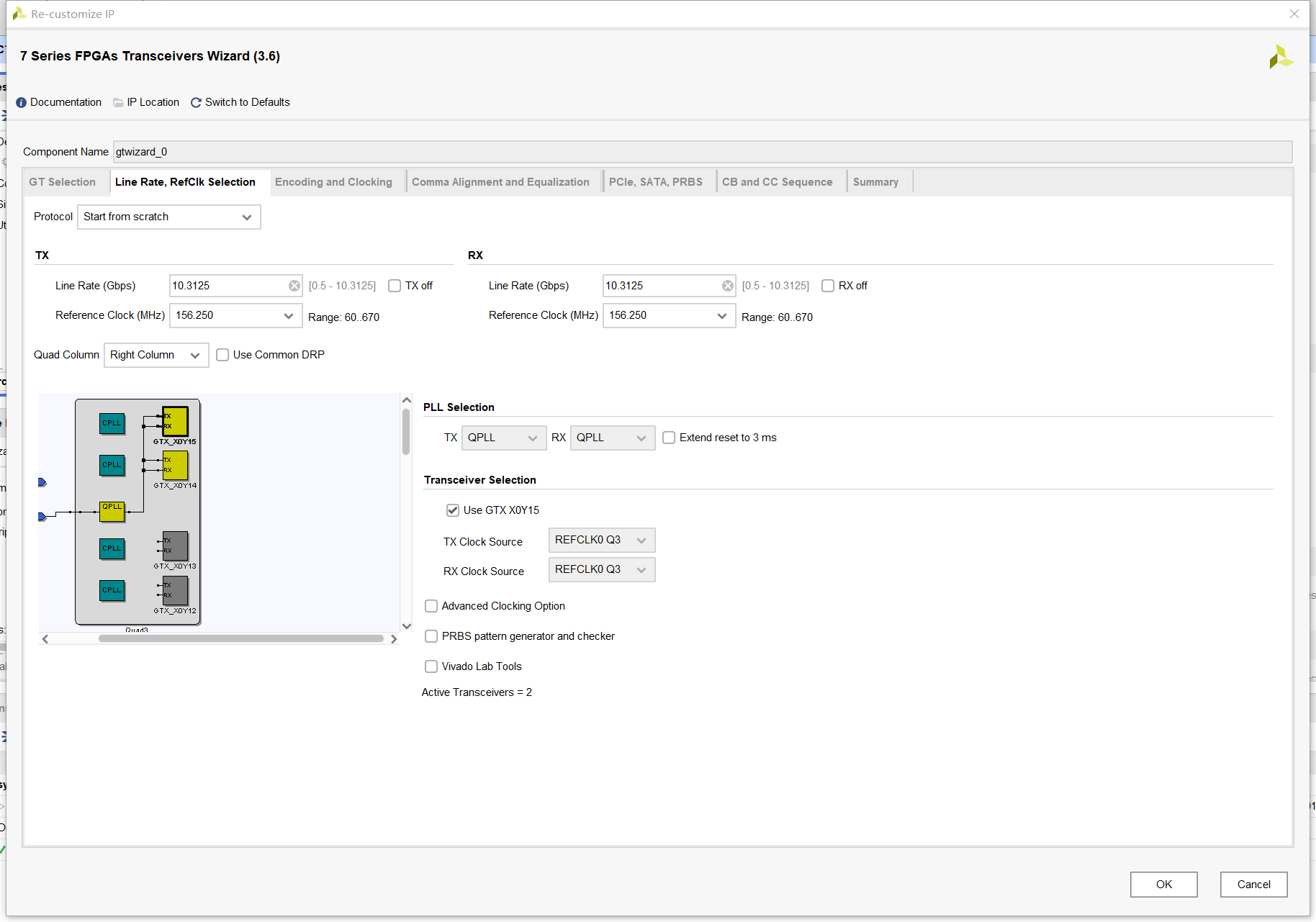

(2)以为我要用万兆网,所以先速率选择10.3125G,选择正确的GTX收发器和时钟,此处正确选择后,约束文件中可直接用系统生成xdc。

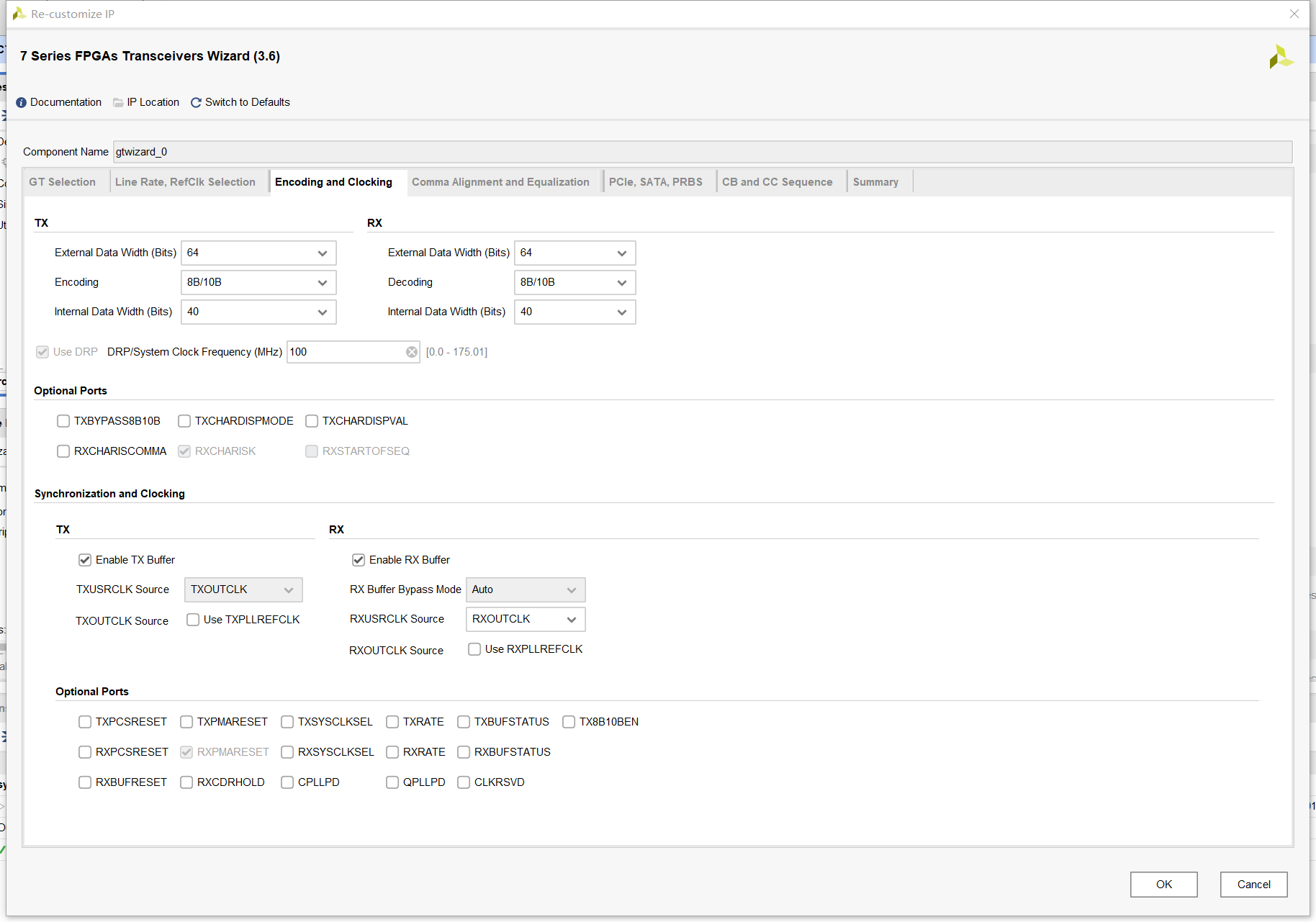

(3)

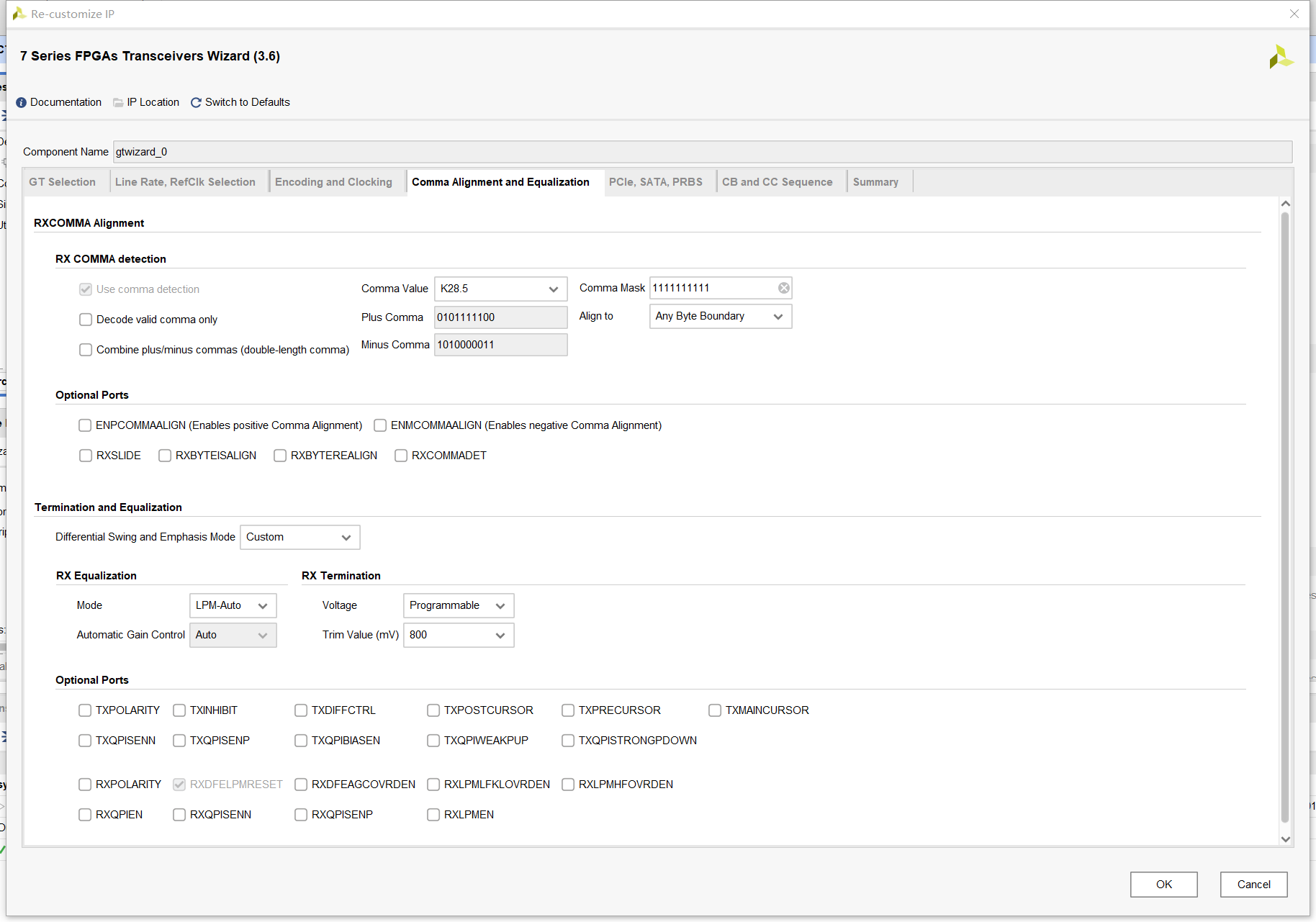

(4)

(5)其他默认即可

(6)生成IP后,右键点击选择生成example design

(7)修改顶层,删除check后的结果指示信号。DRP接口需要时钟,例化一个时钟IP核,输出100M时钟,给DRP时钟引脚,添加一个外部按键信号,连接按键信号与数据生成模块的复位信号,功能就是当按键触发时,生成数据模块开始工作或者停止工作,方便观察信号。在生成数据和控制信号前加(* dont_touch=“true” *)防止信号被优化,其余不做更改。

(8)新建约束文件debug,并设置为目标文件,使以后的约束均在此文件中做修改。打开例程中的约束文件,添加DRP时钟来源的约束,增加按键信号的输入,删除check后的结果指示信号的约束,保存。

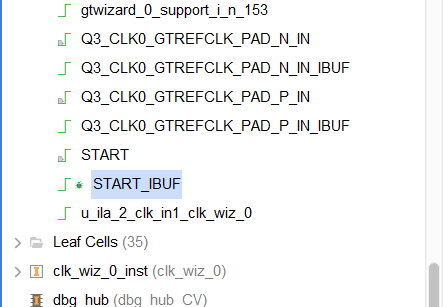

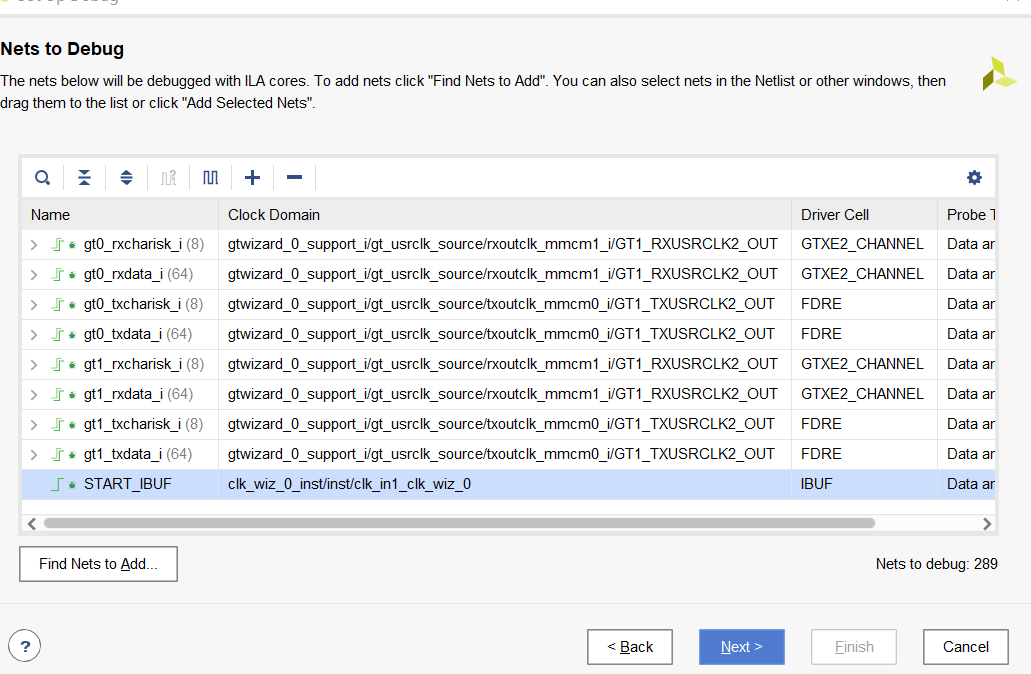

(9)综合,添加抓取信号,此处需要注意的是,start信号需要用自由时钟也就是上电就有的时钟去抓取,最好用drp的那个时钟去抓取,当值debug时,发生找不到时钟的问题。

(10)生成bit,下载。

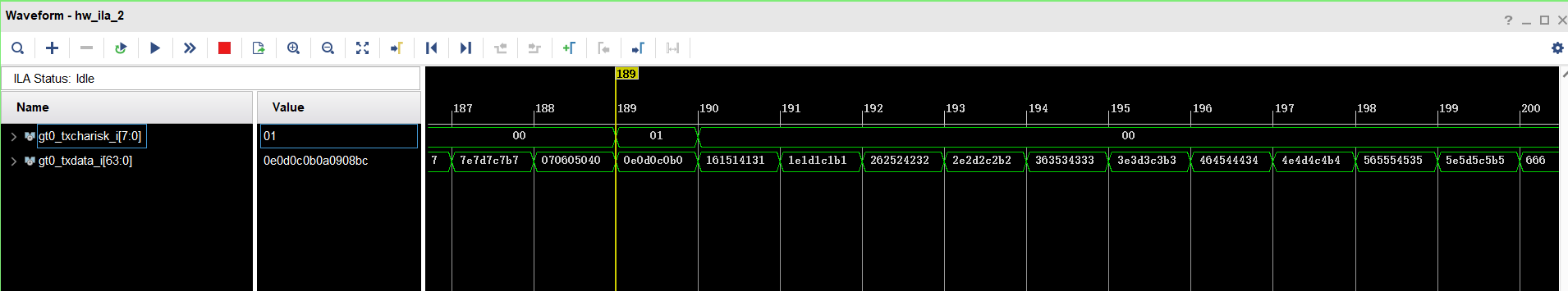

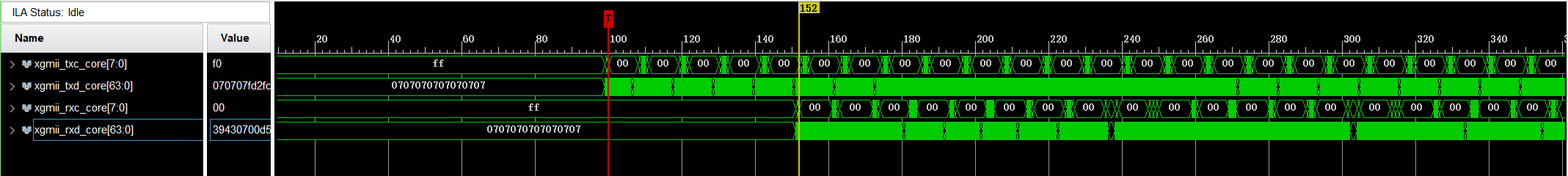

(11)外部环回光纤,发送端,通过gt0发送数据和COMMA码

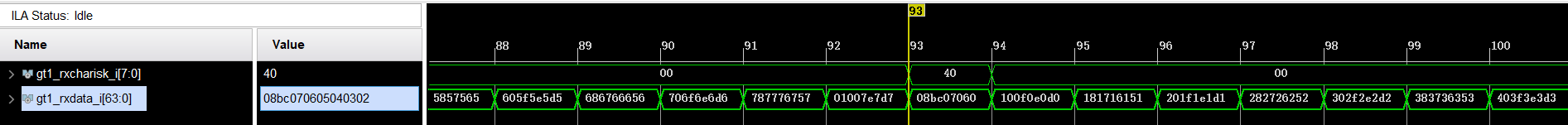

(12)外部环回光纤,接收端,通过gt1接收数据和COMMA码

(13)GTX在工作10.3125时,也是正常的。

7、例化ten_gig_eth_pcs_pma的IP核,xilinx公司在10GBASE_R的模式下此IP是免费的,同时由于我的板子是K7,也仅仅支持此模式。xilinx 10的mac是收费的,由于是点对点传输数据,则可以不用mac中那么复杂的功能,仅仅接用物理通道,实现数据的收发即可,所以可以自行编写一个简单的mac。

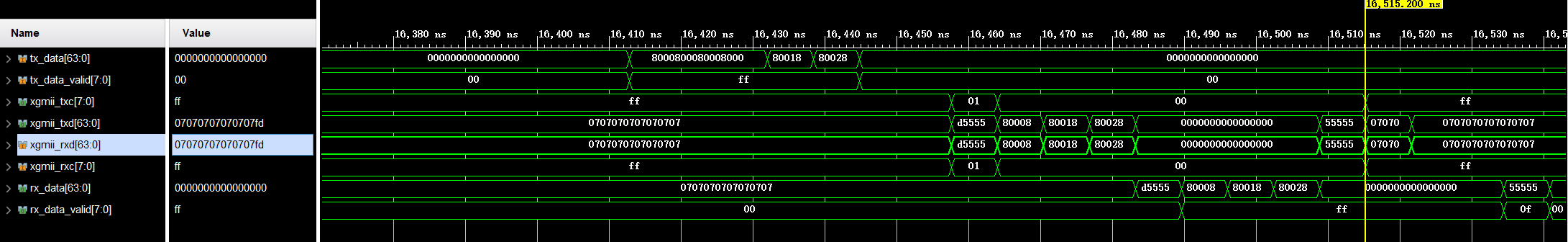

8、简单mac仿真,模块gmii环回。

9、上板测试,光纤回环,也能正确收到数据

10、调试成功。

最后

以上就是畅快咖啡最近收集整理的关于基于FPGA的万兆网调试的全部内容,更多相关基于FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复