经过两次面试后,对MCDF做一次全面的深入总结。

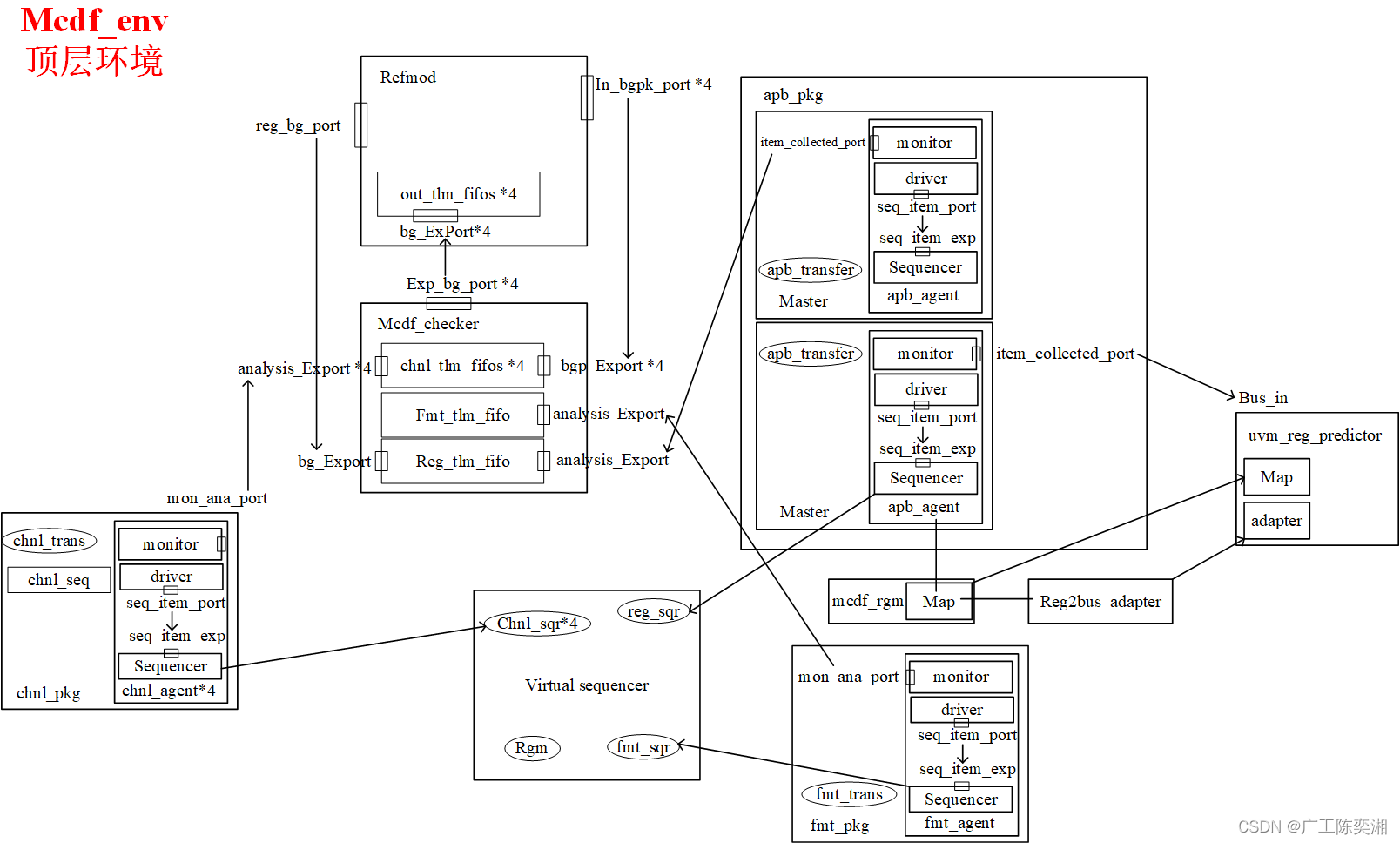

目前进度:硬件部分的node,fifo,寄存器,formatter,MCDF顶层,APB接口,TB接口

软件部分的chnl_pkg,fmt_pkg,apb_pkg,mcdf_rgm_pkg,mcdf_pkg

目录

硬件RTL部分

slave_node

FIFO

arbiter

param_def

寄存器接口

整形器formatter

顶层MCDF

接口打包信号

APB接口

tb中的接口

tb后续

软件部分

chnl_pkg

fmt_pkg

mcdf_rgm_pkg

apb_pkg

apb_test

apb_slave

硬件RTL部分

slave_node

首先是slave_node,就是一开始的channel,为了限制篇幅,具体的解析都写在注释里。

这里的功能是作为FIFO的上行端,按输入输出两端的信号拉高或拉低相应的信号,包括wait,奇偶校验位错误,freeslot,valid,fetch等。

这里还有的疑问如下:

fetch_i是哪里来的信号?由于是读信号的一个条件,且是上行端的数据,猜测是reg的信号

freeslot_o 是哪里的信号?输出端是fifo,在这里没有相应的编码。

奇偶校验位这里是放在最低位,详细看:

电力电子转战数字IC20220527day11(1)——奇偶校验_广工陈奕湘的博客-CSDN博客_缩位异或

module slave_node (

clk_i , //

rst_n_i , //

// From uplink

data_i , //

data_p_i , //奇偶校验位

valid_i , //

slv_en_i , //

wait_o , //

parity_err_o , //

// 输出端

data_o , //

freeslot_o , //

valid_o , //

fetch_i ,

parity_err_clr_i //寄存器来的清除奇偶校验位错误信号

);

input clk_i ; //

input rst_n_i ; //

// IO with driver

input [31:0] data_i ; //

input data_p_i ; //

input valid_i ; //

input slv_en_i ; //

output wait_o ; //

output parity_err_o ; //

// IO with Arbiter

output [31:0] data_o ; //

output [ 5:0] freeslot_o ; //

output valid_o ; //

output fetch_i ;

// IO with register

input parity_err_clr_i ;

reg parity_err_r ;//定义一个reg来assign给parity_err_o

wire parity_err_s, wait_s, fifo_full_s, fifo_wr_s, fifo_rd_s, fifo_empty_s;

assign parity_err_s = valid_i && ^{data_i,data_p_i} ;

//奇偶校验,对数据进行缩位异或后,如果和奇偶校验位不同则出1,此时若valid还拉高就是出错了,error拉高

always @ (posedge clk_i or negedge rst_n_i)

begin : Parity_Err

if (!rst_n_i) begin

parity_err_r <= 1'b0;

end else begin

// 若err_s为1出现数据校验错误,err_r拉高,若clear信号拉高则清楚err信号,拉低

if (parity_err_s ) parity_err_r <= 1'b1 ;

if (parity_err_clr_i) parity_err_r <= 1'b0 ;

end

end

assign parity_err_o = parity_err_r;

assign wait_s = fifo_full_s || parity_err_r ;

//满了或者出现error则要wait

assign fifo_wr_s = valid_i && !parity_err_r && !wait_s && slv_en_i ;

//写信号,有效且校验位正确且不满且enable

assign fifo_rd_s = fetch_i && !fifo_empty_s;

//读信号,不空且fetch则可读

assign wait_o = !slv_en_i || fifo_full_s || parity_err_r ;

//什么时候wait拉高?enable为低,fifo满了,奇偶校验错了

//硬件DUT信号的连接,左边是下一个代码段的fifo

//空满读写分别对应fifo的

sync_dff_fifo inst_fifo (

.clk_i(clk_i ),

.rst_n_i(rst_n_i ),

.data_i(data_i ),

.rd_i(fifo_rd_s ),

.wr_i(fifo_wr_s ),

.full_o(fifo_full_s ),

.empty_o(fifo_empty_s ),

.data_o(data_o ),

.freeslot_o(freeslot_o )

);

assign valid_o = !fifo_empty_s;//不空则valid

endmodule

FIFO

node之后数据存放到fifo中, fifo复习

电力电子转战数字IC20220531day15——双端口RAM与异步FIFO_广工陈奕湘的博客-CSDN博客_fifo 双口ram

module sync_dff_fifo (

clk_i ,

rst_n_i ,

data_i ,

rd_i ,

wr_i ,

full_o ,

empty_o ,

overflow_o ,//满了就会拉高

data_o ,

freeslot_o

);

input clk_i ;

input rst_n_i ;

input [31:0] data_i ;

input rd_i ;

input wr_i ;

output full_o ;

output empty_o ;

output overflow_o ;

output [31:0] data_o ;

output [ 5:0] freeslot_o ;

parameter ADDR_W_C = 5 ;

parameter DEPTH_C = 32 ;

//深度2^5的FIFO需要的地址位数就是5,要比深度多或者一样多就行

//所以ADDR_W_C是5

//深度2^5的FIFO需要的读写指针位宽5+1,多一位作为标志位

//所以freeslot是[5:0]

reg [ADDR_W_C-1 :0] wr_p_r ;//读写指针

reg [ADDR_W_C-1 :0] rd_p_r ;

reg [31:0] mem [DEPTH_C-1:0] ;

//定义了mem型变量存放数据

reg [ADDR_W_C :0] freeslot_r ;

//freeslot是说剩余的空间

wire full_s, empty_s;

reg overflow_r ;

always @(posedge clk_i or negedge rst_n_i)

begin

if (!rst_n_i) begin//复位信号为0,指针为0,freeslot剩余空间为深度32

freeslot_r <= DEPTH_C;

rd_p_r <= 0;

wr_p_r <= 0;

overflow_r <= 1'b0;

end else begin//读写信号时指针加1,表示读写了一次数据

if(rd_i) rd_p_r <= rd_p_r +1 ;

if(wr_i) wr_p_r <= wr_p_r +1 ;

//fifo同一时间可以被同时读写,也可以只读或者只写

if ( rd_i && ~wr_i ) begin

freeslot_r <= freeslot_r+1 ;

end //只读的话,剩余空间增加

if (~rd_i && wr_i ) begin

if (~full_s) begin//只写,剩余空间-1

freeslot_r <= freeslot_r-1 ;

end else begin//如果满了,overflow就会拉高

overflow_r <= 1'b1;

end

end

if (wr_i) begin

mem[wr_p_r] <= data_i ;

end//数据写入操作,直接把数据给mem[写指针]

end

end

//空满标志的assign

assign full_s = freeslot_r == 0 ? 1 : 0 ;

assign empty_o = freeslot_r == DEPTH_C ? 1 : 0 ;

assign full_o = full_s ;

assign overflow_o = overflow_r;

//读数据直接把对应mem中的assign给输出data就好,之前都是要写个always块来赋值

assign data_o = mem[rd_p_r];

assign freeslot_o = freeslot_r ;

endmodule

arbiter

fifo之后来到arbiter, 采用的机制是Round Robin轮询的一个仲裁机制。

简单来说就是4个通道会有请求,每一个clk都会设定一个最高优先级的通道,如果最高通道刚好有请求req,就判定这个channel胜出,拿他的数据,如果没有就往右查找看谁有req。操作完后这个通道的优先级就去到最低优先级,保证每个channel都可以读出数据。

遗留的问题是trigger是从哪里来的信号?

module RR_arbiter(

clk_i,

rst_n_i,

req_vec_i,

win_vec_o,

trigger_i

);

input clk_i;

input rst_n_i;

input [3:0] req_vec_i;

//这个信号表示有多少个通道发起请求

output [3:0] win_vec_o;

input trigger_i ; //触发计算?

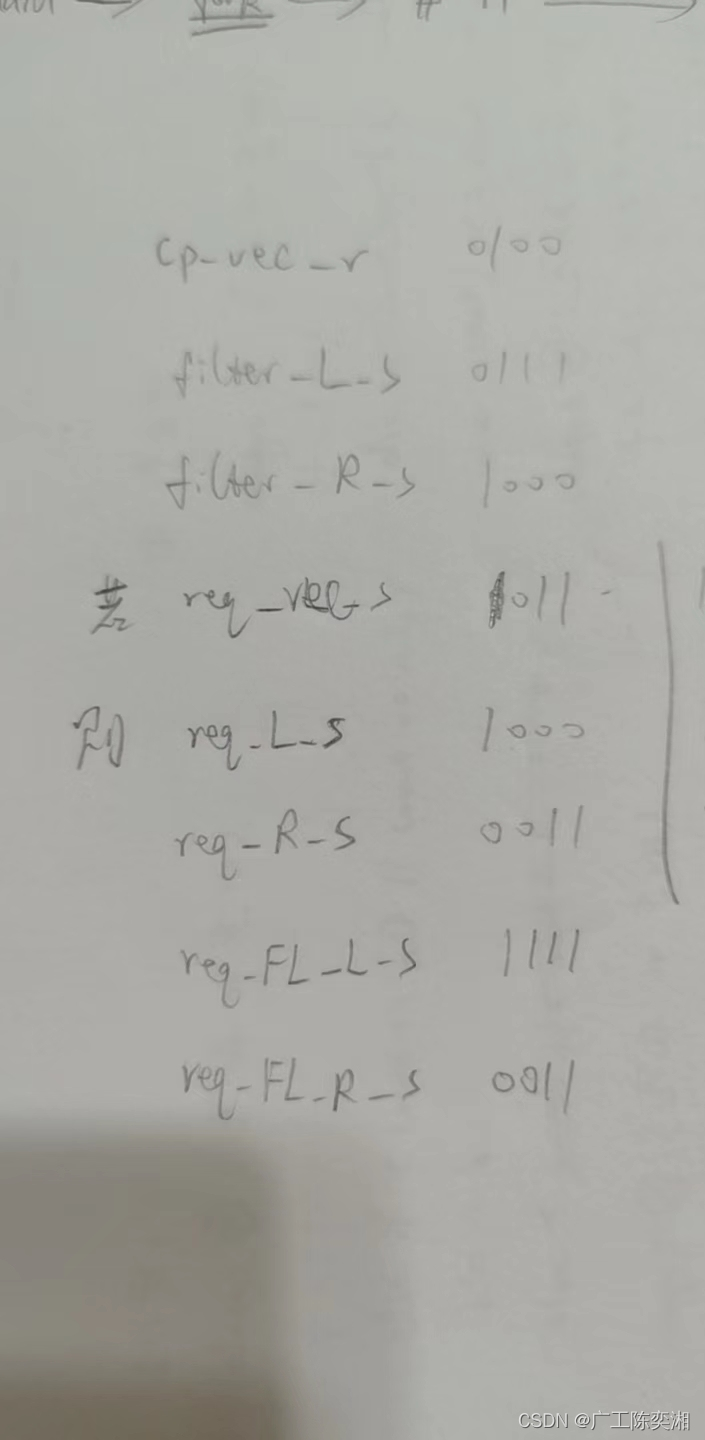

reg [3:0] cp_vec_r ; //4个通道,表示哪一个通道优先级最高

wire [3:0] filter_L_s, filter_R_s, req_msb1_L_s, req_msb1_R_s, req_FL_L_s, req_FL_R_s, req_R_s, req_L_s;

wire [3:0] win_L_s , win_R_s ;

reg [3:0] win_vec_s;

reg [3:0] win_vec_r;

wire req_all0_L_s, req_all0_R_s ;

//filter_L_s表示将cp_vec_r 中置1的那位的左边全部置0,然后取反得到filter_R_s

/用以下四个assign来实现这个功能

assign filter_L_s[3] = cp_vec_r[3];

assign filter_L_s[2] = cp_vec_r[3] || cp_vec_r[2] ;

assign filter_L_s[1] = cp_vec_r[3] || cp_vec_r[2] || cp_vec_r[1] ;

assign filter_L_s[0] = cp_vec_r[3] || cp_vec_r[2] || cp_vec_r[1] || cp_vec_r[0];

assign filter_R_s = ~ filter_L_s ;

//位操作符,每一位都进行与操作

//比如req_vec_i,也就是4个通道的请求;和根据最高优先级cp_vec_r选择的filter_R_s做与操作,都有1才为1,这样得到的req_L_s和req_R_s 是用来干什么的?

//表示结合slave自己的请求req_vec_i ,结合设定好的cp_vec_r ,最高优先级的左右分别有哪个通道允许做操作

assign req_L_s = req_vec_i & filter_R_s ;

assign req_R_s = req_vec_i & filter_L_s ;

//对刚才两个req的L和R做过滤操作,有1的位右边全部置1,为什么?

assign req_FL_L_s[3] = req_L_s[3];

assign req_FL_L_s[2] = req_L_s[3] || req_L_s[2] ;

assign req_FL_L_s[1] = req_L_s[3] || req_L_s[2] || req_L_s[1] ;

assign req_FL_L_s[0] = req_L_s[3] || req_L_s[2] || req_L_s[1] || req_L_s[0] ;

assign req_FL_R_s[3] = req_R_s[3];

assign req_FL_R_s[2] = req_R_s[3] || req_R_s[2] ;

assign req_FL_R_s[1] = req_R_s[3] || req_R_s[2] || req_R_s[1] ;

assign req_FL_R_s[0] = req_R_s[3] || req_R_s[2] || req_R_s[1] || req_R_s[0] ;

//对刚才得到的两个reg_FL的L和R,找置1的最高位,结果存放到req_msb1_L_s

//先把最高位赋值给最高位,然后次高位做判断,最高位为1时置0,否则保持不变;

//然后是次低位,合并高二位后做缩位或运算,如果是01,则出1,次低位置0,表示已经找到;如果是00,则出0,然后次低位保持不变,继续找。

assign req_msb1_L_s[3] = req_FL_L_s[3] ;

assign req_msb1_L_s[2] = req_msb1_L_s[3]? 1'b0 : req_FL_L_s[2] ;

assign req_msb1_L_s[1] = |{req_msb1_L_s[3],req_msb1_L_s[2]} ? 1'b0 : req_FL_L_s[1] ;

assign req_msb1_L_s[0] = |{req_msb1_L_s[3],req_msb1_L_s[2],req_msb1_L_s[1]} ? 1'b0 : req_FL_L_s[0] ;

assign req_msb1_R_s[3] = req_FL_R_s[3] ;

assign req_msb1_R_s[2] = req_msb1_R_s[3] ? 1'b0 : req_FL_R_s[2] ;

assign req_msb1_R_s[1] = |{req_msb1_R_s[3],req_msb1_R_s[2]}? 1'b0 : req_FL_R_s[1] ;

assign req_msb1_R_s[0] = |{req_msb1_R_s[3],req_msb1_R_s[2],req_msb1_R_s[1]}? 1'b0 : req_FL_R_s[0] ;

//---------------------------------------------------------------------------------------

//也可以用这种异或的办法

//assign req_msb1_L_s[3] = req_FL_L_s[3] ;

//assign req_msb1_L_s[2] = req_FL_L_s[3] ^ req_FL_L_s[2] ;

//assign req_msb1_L_s[1] = req_FL_L_s[3] ^ req_FL_L_s[2] ^ req_FL_L_s[1] ;

//assign req_msb1_L_s[0] = req_FL_L_s[3] ^ req_FL_L_s[2] ^ req_FL_L_s[1] ^ req_FL_L_s[0] ;

//

//assign req_msb1_R_s[3] = req_FL_R_s[3] ;

//assign req_msb1_R_s[2] = req_FL_R_s[3] ^ req_FL_R_s[2] ;

//assign req_msb1_R_s[1] = req_FL_R_s[3] ^ req_FL_R_s[2] ^ req_FL_R_s[1] ;

//assign req_msb1_R_s[0] = req_FL_R_s[3] ^ req_FL_R_s[2] ^ req_FL_R_s[1] ^ req_FL_R_s[0] ;

//---------------------------------------------------------------------------------------

//如果req_FL_L_s全部为0,也就是没有满足优先级的通道,req_FL_L_s就拉高

assign req_all0_L_s = ~(|req_msb1_L_s) ;

assign req_all0_R_s = ~(|req_msb1_R_s) ;

//有4种情况:req_FL_L_s符合/不符合条件、req_FL_R_s符合/不符合条件

//这四种情况可以拼接两个全无位来表示{req_all0_L_s, req_all0_R_s}

//根据这个拼接位来决出最后的胜者win_vec_s ,也就是这个clk要给哪个通道授权

always @(req_all0_L_s or req_all0_R_s or req_msb1_R_s or req_msb1_L_s)

begin

case ({req_all0_L_s, req_all0_R_s})

2'b11: win_vec_s <= 4'b0000 ; //这是不可能出现的情况,只能是左或右

2'b10: win_vec_s <= req_msb1_R_s ;

//过滤后左边全0没有通道满足,则胜者为req_msb1_R_s

2'b01: win_vec_s <= req_msb1_L_s ; //同理

2'b00: win_vec_s <= req_msb1_R_s ; //两边都有通道满足要求,则优先是右边的通道,且高位优先级更高

endcase

end

assign win_vec_o = win_vec_r;

always @(posedge clk_i or negedge rst_n_i)

begin

if (!rst_n_i) begin//复位值

cp_vec_r <= 4'b1000;

win_vec_r <= 4'b0000;

end else begin

if (trigger_i) begin

cp_vec_r[0] <= win_vec_s[1];

cp_vec_r[1] <= win_vec_s[2];

cp_vec_r[2] <= win_vec_s[3];

cp_vec_r[3] <= win_vec_s[0];

//每个clk决出一个channel,然后优先级最高的channel就要去到优先级最低了,保证每个通道都有机会

win_vec_r <= win_vec_s;

end

end

end

endmodule

param_def

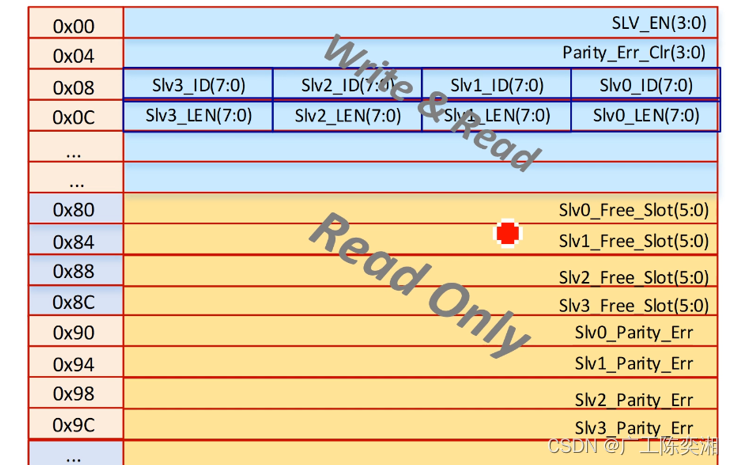

在进入寄存器代码之前,先看参数定义param_def。定义了两种寄存器的地址

4个读写寄存器0x00到0x0C,4个地址为1个寄存器,1个地址存一个8位byte?

`define ADDR_WIDTH 8

`define DATA_WIDTH 32

`define SLV_EN_ADDR_C 8'h00

`define ERR_CLR_ADDR_C 8'h04

`define SLV_ID_ADDR_C 8'h08

`define SLV_LEN_ADDR_C 8'h0C

`define SLV0_FSLOT_ADDR_C 8'h40

`define SLV1_FSLOT_ADDR_C 8'h44

`define SLV2_FSLOT_ADDR_C 8'h48

`define SLV3_FSLOT_ADDR_C 8'h4C

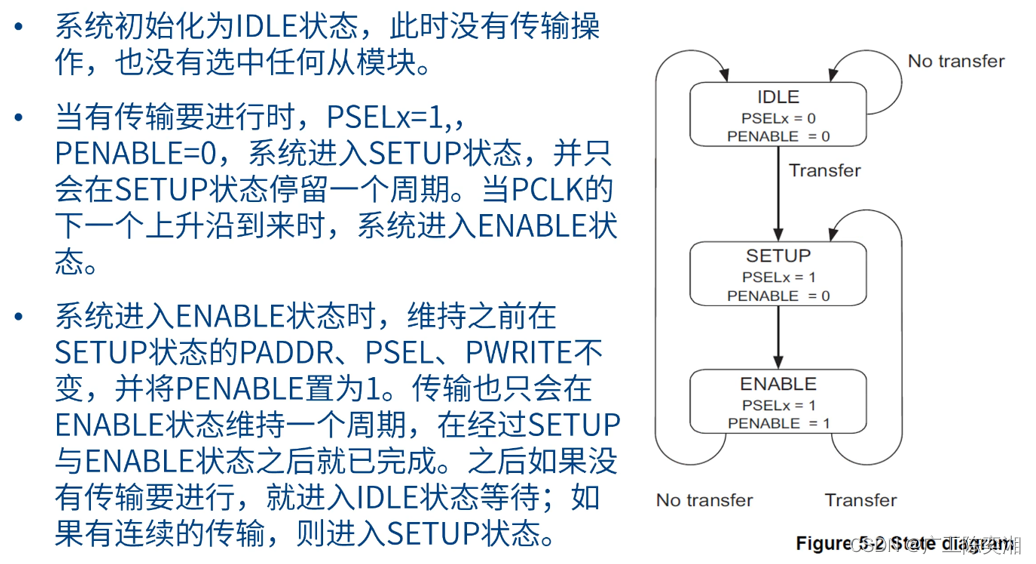

寄存器的代码开始,先看APB总线的状态图,等下会用到

寄存器接口

APB4总线的序列图看这里。

APB4总线介绍_脱密180天的博客-CSDN博客_apb4协议

`include "param_def.v"

module reg_if (

clk_i,

rst_n_i,

//寄存器的信号,其实这几个就是APB总线的信号了

paddr_i, pwr_i, pen_i, psel_i, pwdata_i, prdata_o, pready_o,

pslverr_o, //这个不明,暂时记着

slv_en_o, //对应0x00的使能信号

err_clr_o,

//对应0x08的id信号

slv0_id_o, slv1_id_o, slv2_id_o, slv3_id_o,

//对应0x0C的长度信号

slv0_len_o, slv1_len_o, slv2_len_o, slv3_len_o,

//对应0x04的奇偶校验位错误清除信号

slv0_parity_err_i, slv1_parity_err_i, slv2_parity_err_i, slv3_parity_err_i,

//对应只读寄存器0x80-0x8C的余量信号

slv0_free_slot_i, slv1_free_slot_i, slv2_free_slot_i, slv3_free_slot_i

);

input clk_i;

input rst_n_i;

input [7:0] paddr_i;

input pwr_i;

input pen_i;

input psel_i;

input [31:0] pwdata_i;

output [31:0] prdata_o;

output pready_o;

output pslverr_o;

output [3:0] slv_en_o;

output [3:0] err_clr_o;

output [7:0] slv0_id_o;

output [7:0] slv1_id_o;

output [7:0] slv2_id_o;

output [7:0] slv3_id_o;

output [7:0] slv0_len_o;

output [7:0] slv1_len_o;

output [7:0] slv2_len_o;

output [7:0] slv3_len_o;

input slv0_parity_err_i;

input slv1_parity_err_i;

input slv2_parity_err_i;

input slv3_parity_err_i;

input [5:0] slv0_free_slot_i;

input [5:0] slv1_free_slot_i;

input [5:0] slv2_free_slot_i;

input [5:0] slv3_free_slot_i;

//定义状态名,寄存器的状态有IDLE、SETUP、ACC

parameter [1:0] st_IDLE =2'b00 ;

parameter [1:0] st_SETUP =2'b01 ;

parameter [1:0] st_ACC =2'b10 ;

reg [1:0] last_st, cur_st ;

//给两种寄存器开辟了两个mem,但是只读寄存器不是有8个吗?

reg [31:0] ctrl_mem [3:0];

reg [31:0] ro_mem [3:0]; //?这里应该是[7:0]

wire is_st_idle_s, is_st_setup_s, is_st_acc_s;

//这三个是显示当前状态cur_st的,当前状态是哪个就哪个拉高

wire is_addr_freeslot_3_s;

wire is_addr_freeslot_2_s;

wire is_addr_freeslot_1_s;

wire is_addr_freeslot_0_s;

wire is_addr_parity_err_3_s;

wire is_addr_parity_err_2_s;

wire is_addr_parity_err_1_s;

wire is_addr_parity_err_0_s;

reg [7:0] addr_r;

reg [31:0] data_rd_r;

wire is_ctrl_rng_s;

wire is_ro_rng_s;

wire is_err_rng_s;

wire idx_0_s;

wire idx_1_s;

wire idx_2_s;

wire idx_3_s;

wire is_addr_slv_en_s;

wire is_addr_err_clr_s;

wire is_addr_slv_id_s;

wire is_addr_slv_len_s;

//三段式状态机,之前手撕代码用的是next_state和state

//这里换成last_st和cur_st

always @(posedge clk_i or negedge rst_n_i)

begin

if (!rst_n_i) last_st <= st_IDLE ;

else last_st <= cur_st ;

end

//根据last_st是什么状态做对应的操作,结合APB总线的时序图来看

//IDLE时,sel拉高,就进入setup状态;

//SETUP时自动进入ACC状态,emmm……

//ACC状态时,sel仍然为高,enable拉高,只要sel和en有一个不是高,就回到IDLE状态

always @(*) begin

case (last_st)

st_IDLE : if (psel_i) cur_st <= st_SETUP;

else cur_st <= st_IDLE;

st_SETUP : cur_st <= st_ACC ;

st_ACC : if (psel_i && pen_i) begin

cur_st <= st_ACC ;

end else begin

cur_st <= st_IDLE;

end

endcase

end

//assign了寄存器三个状态的显示,状态机到哪个状态,对应的位就置高

assign is_st_idle_s = (cur_st == st_IDLE ) ? 1'b1 : 1'b0 ;

assign is_st_setup_s = (cur_st == st_SETUP) ? 1'b1 : 1'b0 ;

assign is_st_acc_s = (cur_st == st_ACC ) ? 1'b1 : 1'b0 ;

//关于地址的,在setup状态时将APB总线的地址给到addr_r地址寄存器

always @(posedge clk_i or negedge rst_n_i)

begin

if (!rst_n_i) begin

addr_r <= 0 ;

end else begin

if (is_st_setup_s) begin

addr_r <= paddr_i ;end

end

end

//定义了一个32位的数据存储data_rd_r

//在ACC状态时,读操作要write信号为低~pwr_i

//if条件中的12个信号分别表示用到哪个寄存器,哪个就为1,具体看后面代码

always @(*) begin

data_rd_r <= 0;

if (is_st_acc_s) begin

if (~pwr_i) begin

//哪个寄存器拉高,就把对应mem中的数据给到读出数据的寄存器data_rd_r ,完成数据读出

if (is_addr_slv_en_s ) data_rd_r <= ctrl_mem [0];

if (is_addr_err_clr_s) data_rd_r <= ctrl_mem [1];

if (is_addr_slv_id_s ) data_rd_r <= ctrl_mem [2];

if (is_addr_slv_len_s) data_rd_r <= ctrl_mem [3];

if (is_addr_freeslot_0_s) data_rd_r <= ro_mem [0];

if (is_addr_freeslot_1_s) data_rd_r <= ro_mem [1];

if (is_addr_freeslot_2_s) data_rd_r <= ro_mem [2];

if (is_addr_freeslot_3_s) data_rd_r <= ro_mem [3];

if (is_addr_parity_err_0_s) data_rd_r <= ro_mem [4];

if (is_addr_parity_err_1_s) data_rd_r <= ro_mem [5];

if (is_addr_parity_err_2_s) data_rd_r <= ro_mem [6];

if (is_addr_parity_err_3_s) data_rd_r <= ro_mem [7];

end

end

end

//最后将读出数据寄存器的数据给到总线信号,完成读操作

assign prdata_o = data_rd_r ;

//这个信号表示在ACC状态(应该读写数据的状态)寄存器地址有误,拉高

assign pslverr_o = is_st_acc_s && is_err_rng_s ;

//在ACC状态时reday信号拉高表示准备好读写数据

assign pready_o = is_st_acc_s ;

//这三个信号,首先判断总线来的地址是不是控制寄存器的地址

//根据上面寄存器图,0x00-0x0C是读写寄存器,0x80-0x9C是只读寄存器

//也就是读写寄存器的地址最高为8C,二进制是00001000,对高四位做缩位或,四位都是0才是读写寄存器,所以取反表示当前的地址是读写寄存器的地址

assign is_ctrl_rng_s = ~|(addr_r[7:4]) ; //0h0*

//同理,只读寄存器的二进制地址是10000000到10011100,高三位必须满足100,

assign is_ro_rng_s = addr_r[7] && !addr_r[6] && !addr_r[5] ; //0h8* or 0h9*

//最后,其他地址都不对,就要报错,所以就有了以下信号,既不是读写又不是只读,取反出1

assign is_err_rng_s = ~(is_ctrl_rng_s | is_ro_rng_s);

//APB总线地址的[3:2]位表示的是寄存器的ID,读写寄存器有4个,只读寄存器中freeslot有4个,parity_err有四个,配合上面的表示寄存器的信号,可以得到下面这些信号,对应了12个寄存器,用到哪个就拉高哪个,想不明白的可以回去上面看寄存器的图。

assign idx_0_s = (addr_r[3:2]==2'b00)? 1'b1 : 1'b0;

assign idx_1_s = (addr_r[3:2]==2'b01)? 1'b1 : 1'b0;

assign idx_2_s = (addr_r[3:2]==2'b10)? 1'b1 : 1'b0;

assign idx_3_s = (addr_r[3:2]==2'b11)? 1'b1 : 1'b0;

//12个寄存器信号,地址是哪个就拉高哪个

assign is_addr_slv_en_s = is_ctrl_rng_s & idx_0_s ;

assign is_addr_err_clr_s = is_ctrl_rng_s & idx_1_s ;

assign is_addr_slv_id_s = is_ctrl_rng_s & idx_2_s ;

assign is_addr_slv_len_s = is_ctrl_rng_s & idx_3_s ;

assign is_addr_freeslot_0_s = is_ro_rng_s && !addr_r[4] && idx_0_s ;

assign is_addr_freeslot_1_s = is_ro_rng_s && !addr_r[4] && idx_1_s ;

assign is_addr_freeslot_2_s = is_ro_rng_s && !addr_r[4] && idx_2_s ;

assign is_addr_freeslot_3_s = is_ro_rng_s && !addr_r[4] && idx_3_s ;

assign is_addr_parity_err_0_s = is_ro_rng_s && addr_r[4] && idx_0_s ;

assign is_addr_parity_err_1_s = is_ro_rng_s && addr_r[4] && idx_1_s ;

assign is_addr_parity_err_2_s = is_ro_rng_s && addr_r[4] && idx_2_s ;

assign is_addr_parity_err_3_s = is_ro_rng_s && addr_r[4] && idx_3_s ;

//复位信号为0时,4个控制寄存器的初始值如下

//其中,0x08寄存器存放的是slv的ID,初始值为3210,32位寄存器每个id占8位,用32位十六进制表示为03020100,对应二进制32'b00000011|00000010|00000001|00000000(不是与)

always @ (posedge clk_i or negedge rst_n_i)

begin : CONTROL_PROC

if (!rst_n_i)

begin

ctrl_mem[0] <= 32'h00000000; // slv_en

ctrl_mem[1] <= 32'h00000000; // parity_err_clr

ctrl_mem[2] <= 32'h03020100; // slave ID

ctrl_mem[3] <= 32'h00000000; // length

end else begin

//ACC状态执行写操作,对slv_en和parity_err寄存器来说只有前4位,对slv_id和slv_len来说就有32位全写,所以pwdata分别写入这些位置

//pwdata包含了

if (is_st_acc_s & pwr_i) begin

if (is_addr_slv_en_s ) ctrl_mem [0][3:0] <= pwdata_i ;

if (is_addr_err_clr_s) ctrl_mem [1][3:0] <= pwdata_i ;

if (is_addr_slv_id_s ) ctrl_mem [2] <= pwdata_i ;

if (is_addr_slv_len_s) ctrl_mem [3] <= pwdata_i ;

end

end

end

//fifo余量和奇偶校验位报错的初始值是0

always @ (posedge clk_i or negedge rst_n_i)

begin : RO_PROC

if (!rst_n_i)

begin

ro_mem[0] <= 32'h00000000;

ro_mem[1] <= 32'h00000000;

ro_mem[2] <= 32'h00000000;

ro_mem[3] <= 32'h00000000;

ro_mem[4] <= 32'h00000000;

ro_mem[5] <= 32'h00000000;

ro_mem[6] <= 32'h00000000;

ro_mem[7] <= 32'h00000000;

end else begin

ro_mem[0][5:0] <= slv0_free_slot_i; //这是从fifo输出过来的余量信号

ro_mem[1][5:0] <= slv1_free_slot_i;

ro_mem[2][5:0] <= slv2_free_slot_i;

ro_mem[3][5:0] <= slv3_free_slot_i;

ro_mem[4][0] <= slv0_parity_err_i; //这是从node输出过来的奇偶校验位错误信号

ro_mem[5][0] <= slv1_parity_err_i;

ro_mem[6][0] <= slv2_parity_err_i;

ro_mem[7][0] <= slv3_parity_err_i;

end

end

//对应控制寄存器的位assign给寄存器输出信号

assign slv_en_o = ctrl_mem[0][3:0];

assign err_clr_o = ctrl_mem[1][3:0];

assign slv0_id_o = ctrl_mem[2][1*8-1: 0];

assign slv1_id_o = ctrl_mem[2][2*8-1:1*8];

assign slv2_id_o = ctrl_mem[2][3*8-1:2*8];

assign slv3_id_o = ctrl_mem[2][4*8-1:3*8];

assign slv0_len_o = ctrl_mem[3][1*8-1: 0];

assign slv1_len_o = ctrl_mem[3][2*8-1:1*8];

assign slv2_len_o = ctrl_mem[3][3*8-1:2*8];

assign slv3_len_o = ctrl_mem[3][4*8-1:3*8];

endmodule

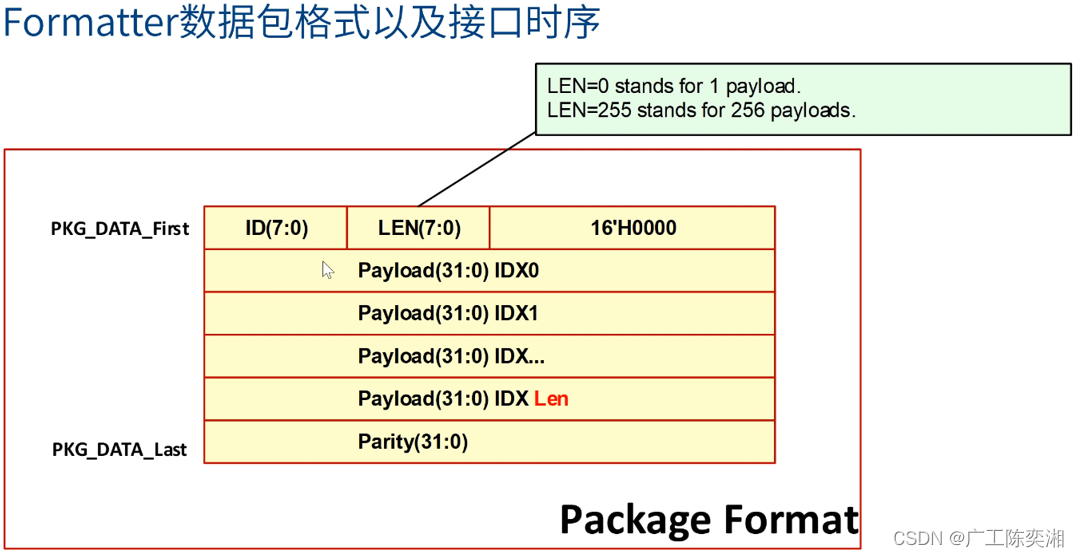

整形器formatter

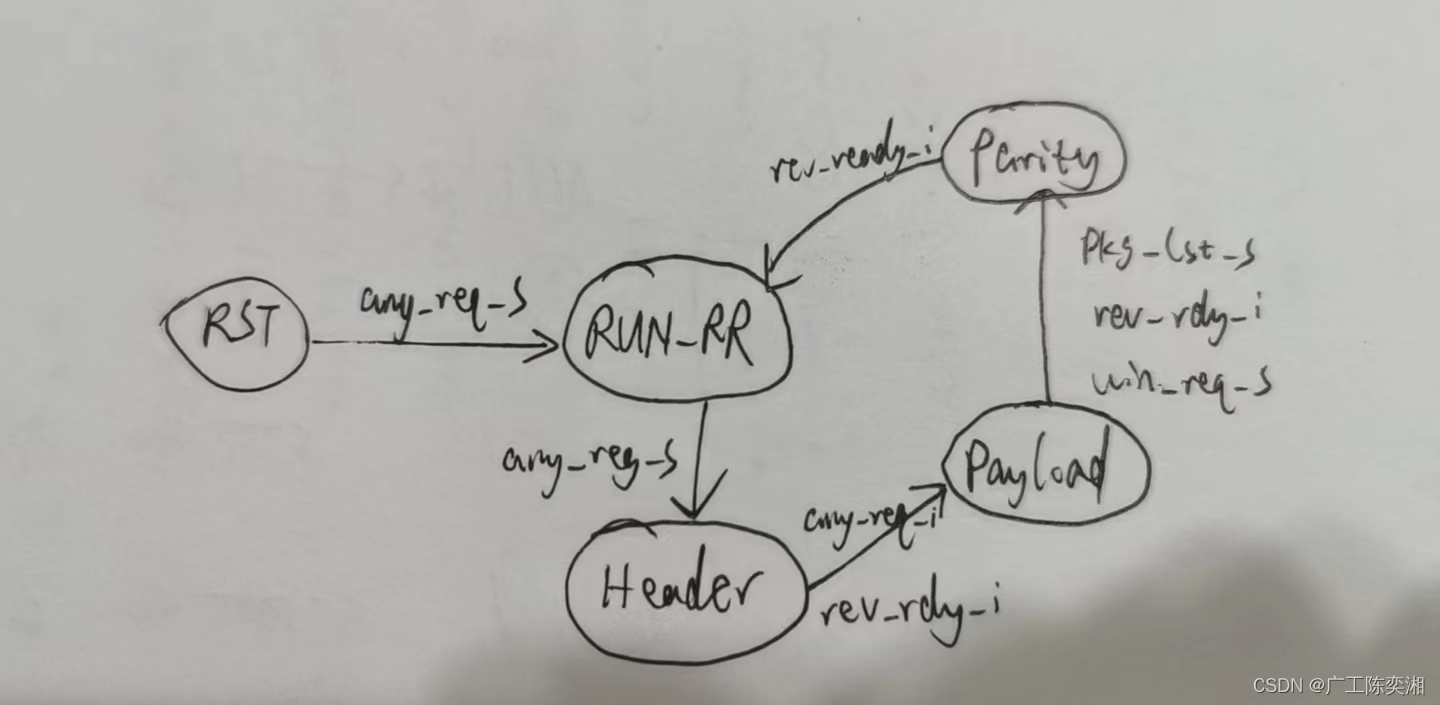

formatter的工作原理也是状态机,有任意的通道发起请求则进入RUN_RR启动仲裁器,然后进入发送第一个payload的状态header,接收端ready信号为高时开始发送数据,进入payload状态,最后一个payload发送完拉高pkg_lst表示发送完毕,进入parity,然后继续回到RUN_RR

module formater(

input clk_i,

input rst_n_i,

//和4个node的信号连接,包括32位数据,slv_id,slv_len,不包括读写寄存器[1]的奇偶校验报错

//但有些信号在node里面并没有,可能是寄存器来的?

input [31:0] data_slv0_i,

input [31:0] data_slv1_i,

input [31:0] data_slv2_i,

input [31:0] data_slv3_i,

input [7:0] id_slv0_i,

input [7:0] id_slv1_i,

input [7:0] id_slv2_i,

input [7:0] id_slv3_i,

input [7:0] len_slv0_i,

input [7:0] len_slv1_i,

input [7:0] len_slv2_i,

input [7:0] len_slv3_i,

//四个channel的请求信号

input [3:0] req_vec_i ,

output [3:0] fetch_vec_o,

//仲裁器给到这里的是胜出channel,然后fmt就接收该channel的数据

input [3:0] win_vec_i,

//arbiter中遗留的问题信号trigger应该是对应这里这个了

output trigger_start_o,

//fmt输出端信号

input rev_rdy_i,

//接收端发出的ready信号表示准备好接收fmt的数据包

//如图,fmt的任务就是把各个数据打包成多个payload的形式

//len+1表示payload的数量,32位的payload存放的是id、len和16位data,最后一个payload存放的是奇偶校验位

output pkg_vld_o,

output [31:0] pkg_dat_o,

output pkg_fst_o,

output pkg_lst_o

);

//状态定义

parameter [2:0] ST_RST = 3'b000;

parameter [2:0] ST_Run_RR = 3'b001;

parameter [2:0] ST_Header = 3'b010;

parameter [2:0] ST_Payload = 3'b011;

parameter [2:0] ST_Parity = 3'b100;

reg [2:0] cur_st, nxt_st;

//4个通道的胜者显示,包括数据、id、长度

wire [31:0] data_slv0_win_s ;

wire [31:0] data_slv1_win_s ;

wire [31:0] data_slv2_win_s ;

wire [31:0] data_slv3_win_s ;

wire [31:0] data_win_s ;

wire [7:0] id_slv0_win_s ;

wire [7:0] id_slv1_win_s ;

wire [7:0] id_slv2_win_s ;

wire [7:0] id_slv3_win_s ;

wire [7:0] id_win_s ;

wire [7:0] len_slv0_win_s ;

wire [7:0] len_slv1_win_s ;

wire [7:0] len_slv2_win_s ;

wire [7:0] len_slv3_win_s ;

wire [7:0] len_win_s ;

//状态机当前状态显示

wire is_st_run_rr_s ;

wire is_st_header_s ;

wire is_st_payload_s ;

wire is_st_parity_s ;

//发送状态点亮

wire send_header_s ;

wire send_payload_s ;

wire send_parity_s ;

wire pkg_lst_s ;

//channel的请求和胜出显示

wire [3:0] win_req_vec_s;

wire win_req_s ;

wire any_win_s ;

wire any_req_s ;

//数据包有效显示

wire pkg_vld_s ;

reg [31:0] tx_d_s ;//输出数据寄存器

reg [31:0] parity_r ;//奇偶校验位寄存器

reg [ 7:0] len_cnt_r ;//长度len寄存器

wire [ 3:0] fetch_vec_s ;//fetch?

//通道胜出者显示

assign win_req_vec_s = win_vec_i & req_vec_i ;

//缩位与,有通道请求胜出就拉高

assign win_req_s = |win_req_vec_s ;

//同理,有任意通道胜出就拉高,这两个好像差不多,要辨别一下

assign any_win_s = |win_vec_i ;

//同理,有任意通道请求就拉高

assign any_req_s = |req_vec_i ;

//fmt的工作模式也是状态机,只要有node发起请求,状态就从RST到RUN_RR再到Header,如果接收端准备好了就进入payload,如果最后一个payload发送完就进入parity,完成传输,回到RUN_RR

always @(posedge clk_i or negedge rst_n_i)

begin

if (!rst_n_i) cur_st <= ST_RST ;

else cur_st <= nxt_st ;

end

always @(*) begin

nxt_st <= cur_st;

case (cur_st)

ST_RST : if ( any_req_s) nxt_st <= ST_Run_RR ;

ST_Run_RR : if ( any_req_s) nxt_st <= ST_Header ;

ST_Header : if ( rev_rdy_i && any_req_s) nxt_st <= ST_Payload ;

ST_Payload : if (pkg_lst_s && rev_rdy_i && win_req_s) nxt_st <= ST_Parity ;

ST_Parity : if ( rev_rdy_i ) nxt_st <= ST_Run_RR ;

endcase

end

//根据仲裁器的胜者信号,拉高对应的表示data所在通道胜出的信号

assign data_slv0_win_s = win_vec_i[0] ? data_slv0_i: 0 ;

assign data_slv1_win_s = win_vec_i[1] ? data_slv1_i: 0 ;

assign data_slv2_win_s = win_vec_i[2] ? data_slv2_i: 0 ;

assign data_slv3_win_s = win_vec_i[3] ? data_slv3_i: 0 ;

//只要有一个胜出的node就拉高这个信号

assign data_win_s= data_slv0_win_s | data_slv1_win_s | data_slv2_win_s | data_slv3_win_s ;

//同上,所在通道id的信号拉高

assign id_slv0_win_s = win_vec_i[0] ? id_slv0_i : 0 ;

assign id_slv1_win_s = win_vec_i[1] ? id_slv1_i : 0 ;

assign id_slv2_win_s = win_vec_i[2] ? id_slv2_i : 0 ;

assign id_slv3_win_s = win_vec_i[3] ? id_slv3_i : 0 ;

assign id_win_s = id_slv0_win_s | id_slv1_win_s | id_slv2_win_s | id_slv3_win_s ;

//同上,所在通道数据长度的信号拉高

assign len_slv0_win_s = win_vec_i[0] ? len_slv0_i : 0 ;

assign len_slv1_win_s = win_vec_i[1] ? len_slv1_i : 0 ;

assign len_slv2_win_s = win_vec_i[2] ? len_slv2_i : 0 ;

assign len_slv3_win_s = win_vec_i[3] ? len_slv3_i : 0 ;

assign len_win_s = len_slv0_win_s | len_slv1_win_s | len_slv2_win_s | len_slv3_win_s ;

//状态机的显示信号,在哪个状态就拉高哪个信号

assign is_st_run_rr_s = (cur_st==ST_Run_RR )? 1'b1 : 1'b0 ;

assign is_st_header_s = (cur_st==ST_Header )? 1'b1 : 1'b0 ;

assign is_st_payload_s = (cur_st==ST_Payload)? 1'b1 : 1'b0 ;

assign is_st_parity_s = (cur_st==ST_Parity )? 1'b1 : 1'b0 ;

//在header状态时,若有任意通道有req且接收端做好准备rev_req,则开始发送第一个payload,并进入payload状态,这个信号表示发送了第一个payload

assign send_header_s = is_st_header_s && rev_rdy_i ;

assign pkg_fst_o = send_header_s ;

//同理,这个表示发送剩余payloads

assign send_payload_s = is_st_payload_s && rev_rdy_i && win_req_s ;

//同理,这个表示发送最后的payload奇偶校验

assign send_parity_s = is_st_parity_s && rev_rdy_i ;

//send_parity_s标志着数据包传输结束,拉高last

assign pkg_lst_o = send_parity_s ;

//trigger信号在启动仲裁器或开始发送header时拉高

//assign trigger_start_o = send_header_s ;

assign trigger_start_o = is_st_run_rr_s ;

//在传送payload的状态中将对应payload中的数据赋给输出端完成传输,结合fmt的图就知道了

always @(*)

begin

tx_d_s <= 0;

if (is_st_header_s) begin

tx_d_s <= {id_win_s, len_win_s,16'h0000};

end

if (is_st_payload_s) begin

tx_d_s <= data_win_s ;

end

if (is_st_parity_s) begin

tx_d_s <= parity_r;

end

end

assign pkg_dat_o = tx_d_s ;

//最后一个payload发送完后长度len就为0,缩位逻辑或出0,取反出1表示payload发送完了

assign pkg_lst_s = ~|(len_cnt_r) ;

//

always @(posedge clk_i or negedge rst_n_i)

begin

if (~rst_n_i) begin

parity_r <= 0 ;

len_cnt_r <= 0 ;

end else begin

if (send_header_s) begin

parity_r <= {id_win_s, len_win_s,16'h0000};

len_cnt_r <= len_win_s ;

end

if (send_payload_s) begin

parity_r <= data_win_s ^ parity_r ;

len_cnt_r<= len_cnt_r - 1;//第一个payload的len是[0],这里要减1

end

if (send_parity_s) begin//发送完parity后清零结束一个pkg的传输

parity_r <= 0 ;

len_cnt_r <= 0 ;

end

end

end

// fetch_vec是个4位信号,表示4个channel哪一个个完成了传输(ready且经过payload状态)

//4位和独热码win_vec按位与

assign fetch_vec_s = {4{rev_rdy_i && is_st_payload_s }} & win_vec_i ;

assign fetch_vec_o = fetch_vec_s ;

// pkg有效信号,在状态为header、payload且有req、parity时有效

assign pkg_vld_s = is_st_header_s || (is_st_payload_s && win_req_s) || is_st_parity_s ;

assign pkg_vld_o = pkg_vld_s ;

endmodule

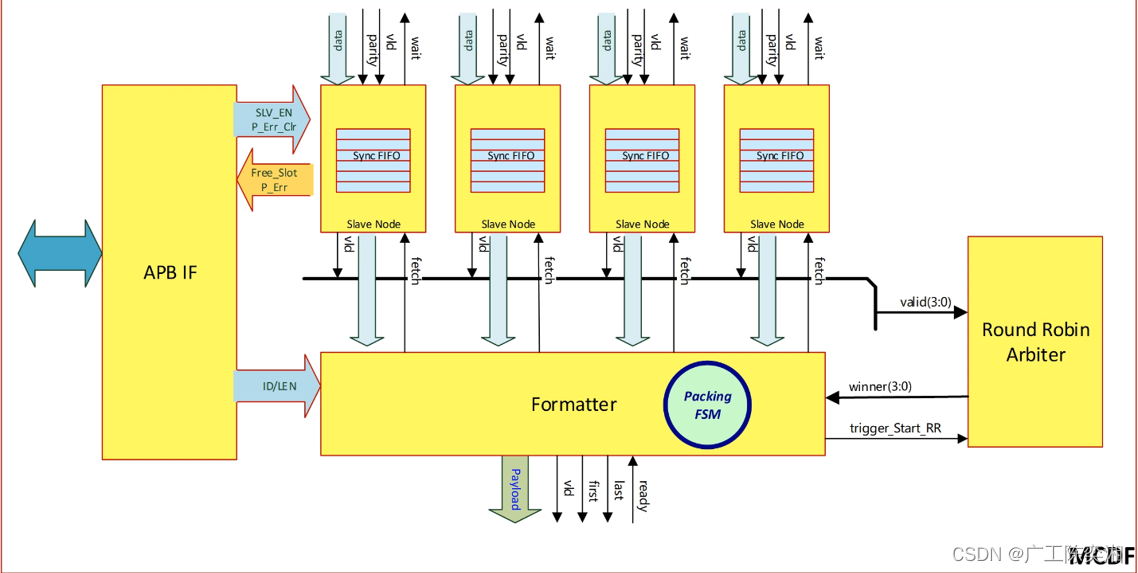

顶层MCDF

结构不是之前的channel-arb-fmt,而是node_fifo直接到fmt,arb和reg和apb包围这两个结构,形成一个完整的MCDF结构

module mcdf(

input clk_i ,

input rst_n_i ,

//4个node的信号,分别有32位数据,1位奇偶校验,valid信号应该是fmt的输出pkg_vld_o,最后是奇偶校验报错给到APB总线

input [31:0] slv0_data_i , //

input slv0_data_p_i , //

input slv0_valid_i , //

output slv0_wait_o , //fifo满了,slv_en为低,奇偶校验错误,则wait

output slv0_parity_err_o , //

input [31:0] slv1_data_i , //

input slv1_data_p_i , //

input slv1_valid_i , //

output slv1_wait_o , //

output slv1_parity_err_o , //

input [31:0] slv2_data_i , //

input slv2_data_p_i , //

input slv2_valid_i , //

output slv2_wait_o , //

output slv2_parity_err_o , //

input [31:0] slv3_data_i , //

input slv3_data_p_i , //

input slv3_valid_i , //

output slv3_wait_o , //

output slv3_parity_err_o , //

// APB总线的接口信号,和后面的apb_if中的一样,在mcdf顶层结构中要完成接口的连接

input [7:0] paddr_i ,

input pwr_i ,

input pen_i ,

input psel_i ,

input [31:0] pwdata_i ,

output [31:0] prdata_o ,

output pready_o ,

output pslverr_o ,

//mcdf的输出端,其实就是fmt的输出端

input rev_rdy_i ,

output pkg_vld_o ,

output [31:0] pkg_dat_o ,

output pkg_fst_o ,

output pkg_lst_o

);

//数据显示信号

wire [31:0] slv0_data_s,slv1_data_s, slv2_data_s, slv3_data_s ;

//余量显示信号,0x80-0x8C寄存器存储的

wire [5 :0] slv0_freeslot_s, slv1_freeslot_s, slv2_freeslot_s, slv3_freeslot_s;

//0x08寄存器存储的ID信号,和寄存器相连

wire [7 :0] slv0_id_s,slv1_id_s,slv2_id_s,slv3_id_s ;

//同理

wire [7 :0] slv0_len_s,slv1_len_s,slv2_len_s,slv3_len_s ;

wire [3 :0] err_clr_vec_s, fetch_vec_s, req_vec_s, slv_en_vec_s, win_vec_s;

wire trigger_s,slv3_fetch_s ,slv2_fetch_s ,slv1_fetch_s ,slv0_fetch_s ;

//MCDF接口连接到寄存器接口上,左边是reg_if的接口

reg_if inst_reg_if (

.clk_i (clk_i ),

.rst_n_i (rst_n_i ),

.paddr_i (paddr_i ),

.pwr_i (pwr_i ),

.pen_i (pen_i ),

.psel_i (psel_i ),

.pwdata_i (pwdata_i ),

.prdata_o (prdata_o ),

.pready_o (pready_o ),

.pslverr_o (pslverr_o ),

.slv_en_o (slv_en_vec_s ),

.err_clr_o (err_clr_vec_s ),

.slv0_id_o (slv0_id_s ),

.slv1_id_o (slv1_id_s ),

.slv2_id_o (slv2_id_s ),

.slv3_id_o (slv3_id_s ),

.slv0_len_o (slv0_len_s ),

.slv1_len_o (slv1_len_s ),

.slv2_len_o (slv2_len_s ),

.slv3_len_o (slv3_len_s ),

.slv0_parity_err_i (slv0_parity_err_s ),

.slv1_parity_err_i (slv1_parity_err_s ),

.slv2_parity_err_i (slv2_parity_err_s ),

.slv3_parity_err_i (slv3_parity_err_s ),

.slv0_free_slot_i (slv0_freeslot_s ),

.slv1_free_slot_i (slv1_freeslot_s ),

.slv2_free_slot_i (slv2_freeslot_s ),

.slv3_free_slot_i (slv3_freeslot_s )

);

//MCDF接口连接到4个node上

slave_node inst_slave_node_0 (

.clk_i (clk_i ),

.rst_n_i (rst_n_i ),

.data_i (slv0_data_i ),

.data_p_i (slv0_data_p_i ),

.valid_i (slv0_valid_i ),

.slv_en_i (slv_en_vec_s[0] ),

.wait_o (slv0_wait_o ),

.parity_err_o (slv0_parity_err_s ),

.data_o (slv0_data_s ),

.freeslot_o (slv0_freeslot_s ),

.valid_o (slv0_valid_o_s ),

.fetch_i (slv0_fetch_s ),

.parity_err_clr_i (err_clr_vec_s[0] )

);

assign slv0_parity_err_o = slv0_parity_err_s;

slave_node inst_slave_node_1 (

.clk_i (clk_i ),

.rst_n_i (rst_n_i ),

.data_i (slv1_data_i ),

.data_p_i (slv1_data_p_i ),

.valid_i (slv1_valid_i ),

.slv_en_i (slv_en_vec_s[1] ),

.wait_o (slv1_wait_o ),

.parity_err_o (slv1_parity_err_s ),

.data_o (slv1_data_s ),

.freeslot_o (slv1_freeslot_s ),

.valid_o (slv1_valid_o_s ),

.fetch_i (slv1_fetch_s ),

.parity_err_clr_i (err_clr_vec_s[1] )

);

assign slv1_parity_err_o = slv1_parity_err_s;

slave_node inst_slave_node_2 (

.clk_i (clk_i ),

.rst_n_i (rst_n_i ),

.data_i (slv2_data_i ),

.data_p_i (slv2_data_p_i ),

.valid_i (slv2_valid_i ),

.slv_en_i (slv_en_vec_s[2] ),

.wait_o (slv2_wait_o ),

.parity_err_o (slv2_parity_err_s ),

.data_o (slv2_data_s ),

.freeslot_o (slv2_freeslot_s ),

.valid_o (slv2_valid_o_s ),

.fetch_i (slv2_fetch_s ),

.parity_err_clr_i (err_clr_vec_s[2] )

);

assign slv2_parity_err_o = slv2_parity_err_s;

slave_node inst_slave_node_3 (

.clk_i (clk_i ),

.rst_n_i (rst_n_i ),

.data_i (slv3_data_i ),

.data_p_i (slv3_data_p_i ),

.valid_i (slv3_valid_i ),

.slv_en_i (slv_en_vec_s[3] ),

.wait_o (slv3_wait_o ),

.parity_err_o (slv3_parity_err_s ),

.data_o (slv3_data_s ),

.freeslot_o (slv3_freeslot_s ),

.valid_o (slv3_valid_o_s ),

.fetch_i (slv3_fetch_s ),

.parity_err_clr_i (err_clr_vec_s[3] )

);

assign slv3_parity_err_o = slv3_parity_err_s;

assign req_vec_s = {slv3_valid_o_s,slv2_valid_o_s,slv1_valid_o_s,slv0_valid_o_s};

//连接到仲裁器

RR_arbiter inst_arb (

.clk_i (clk_i ),

.rst_n_i (rst_n_i ),

.req_vec_i (req_vec_s ),

.win_vec_o (win_vec_s ),

.trigger_i (trigger_s )

);

//连接到fmt

formater inst_formatter (

.clk_i (clk_i ),

.rst_n_i (rst_n_i ),

.data_slv0_i (slv0_data_s ),

.data_slv1_i (slv1_data_s ),

.data_slv2_i (slv2_data_s ),

.data_slv3_i (slv3_data_s ),

.id_slv0_i (slv0_id_s ),

.id_slv1_i (slv1_id_s ),

.id_slv2_i (slv2_id_s ),

.id_slv3_i (slv3_id_s ),

.len_slv0_i (slv0_len_s ),

.len_slv1_i (slv1_len_s ),

.len_slv2_i (slv2_len_s ),

.len_slv3_i (slv3_len_s ),

.req_vec_i (req_vec_s ),

.fetch_vec_o (fetch_vec_s ),

.win_vec_i (win_vec_s ),

.trigger_start_o (trigger_s ),

.rev_rdy_i (rev_rdy_i ),

.pkg_vld_o (pkg_vld_o ),

.pkg_dat_o (pkg_dat_o ),

.pkg_fst_o (pkg_fst_o ),

.pkg_lst_o (pkg_lst_o )

);

//fetch信号的显示

assign slv0_fetch_s = fetch_vec_s[0];

assign slv1_fetch_s = fetch_vec_s[1];

assign slv2_fetch_s = fetch_vec_s[2];

assign slv3_fetch_s = fetch_vec_s[3];

endmodule

接口打包信号

APB接口

对应MCDF中的APB接口。

这里的问题是,has_coverage和has_coverage有没有其他地方控制的?

`ifndef APB_IF_SV

`define APB_IF_SV

interface apb_if (input clk, input rstn);

logic [31:0] paddr;

logic pwrite;

logic psel;

logic penable;

logic [31:0] pwdata;

logic [31:0] prdata;

logic pready;

//表示APB传输的过程中发生了错误,可能是读写;只在传输的最后一拍拉高

logic pslverr;

// Control flags

bit has_checks = 1;

bit has_coverage = 1;

import uvm_pkg::*;

`include "uvm_macros.svh"

//这里信号的方向和MCDF中的完全相反,addr等信号是从总线给到MCDF的,所以这里是输出

clocking cb_mst @(posedge clk);

default input #1ps output #1ps;

output paddr, pwrite, psel, penable, pwdata;

input prdata, pready, pslverr;

endclocking : cb_mst

//如果是总线的从设备(MCDF),则方向和MCDF的一样

// clocking cb_slv @(posedge clk);

// default input #1ps output #1ps;

// input paddr, pwrite, psel, penable, pwdata;

// output prdata, pready, pslverr;

// endclocking : cb_slv

//monitor的时钟块,所有信号都是input

clocking cb_mon @(posedge clk);

default input #1ps output #1ps;

input paddr, pwrite, psel, penable, pwdata, prdata, pready, pslverr;

endclocking : cb_mon

// APB指令的覆盖组

//覆盖组 组名 @触发条件;然后是覆盖点 信号名{设置打印与收集 编写bins}

covergroup cg_apb_command @(posedge clk iff rstn);

pwrite: coverpoint pwrite{

type_option.weight = 0;

bins write = {1};

bins read = {0};

}//pwrite信号有两种状态,拉高为write拉低为read,所以有两个bins,下面同理

psel : coverpoint psel{

type_option.weight = 0;

bins sel = {1};

bins unsel = {0};

}

//apb指令有三个,binsof指定覆盖点,指令为write时对应的覆盖点是sel拉高和write拉高

cmd : cross pwrite, psel{

bins cmd_write = binsof(psel.sel) && binsof(pwrite.write);

bins cmd_read = binsof(psel.sel) && binsof(pwrite.read);

bins cmd_idle = binsof(psel.unsel);

}

endgroup: cg_apb_command

// APB连续传输多个数据的覆盖组

covergroup cg_apb_trans_timing_group @(posedge clk iff rstn);

psel: coverpoint psel{//传输n个数据psel拉高2*n拍,

bins single = (0 => 1 => 1 => 0);

bins burst_2 = (0 => 1 [*4] => 0);

bins burst_4 = (0 => 1 [*8] => 0);

bins burst_8 = (0 => 1 [*16] => 0);

bins burst_16 = (0 => 1 [*32] => 0);

bins burst_32 = (0 => 1 [*64] => 0);

}

penable: coverpoint penable {

//enable连续传输时每两拍拉高一拍,传输单个数据时记得是有idel_cycle的设置所以是2-10拍

bins single = (0 => 1 => 0 [*2:10] => 1);

bins burst = (0 => 1 => 0 => 1);

}

endgroup: cg_apb_trans_timing_group

// APB读写顺序检测的覆盖组

//触发条件多了个penable,只有enable拉高的读写才是有效读写

covergroup cg_apb_write_read_order_group @(posedge clk iff (rstn && penable));

write_read_order: coverpoint pwrite{

bins write_write = (1 => 1);

bins write_read = (1 => 0);

bins read_write = (0 => 1);

bins read_read = (0 => 0);

}

endgroup: cg_apb_write_read_order_group

//覆盖组需要例化,且声明为automatic型

initial begin : coverage_control

if(has_coverage) begin

automatic cg_apb_command cg0 = new();

automatic cg_apb_trans_timing_group cg1 = new();

automatic cg_apb_write_read_order_group cg2 = new();

end

end

//属性和断言的编写,描述具体的感兴趣的序列,首先是断言属性

//第一个是希望总线过来的地址不存在x,地址和sel为高时(交叠蕴含同一拍)用isunknown检查地址中是否存在x和z,若有则为1,取非没有出1,assert这个property要为1才不会报错

//断言是检查时序的,可以通过一个max_quit什么的设置error数量,到了就finish,具体忘了,等uvm的时候看看

property p_paddr_no_x;

@(posedge clk) psel |-> !$isunknown(paddr);

endproperty: p_paddr_no_x

assert property(p_paddr_no_x) else `uvm_error("ASSERT", "PADDR is unknown when PSEL is high")

property p_psel_rose_next_cycle_penable_rise;

@(posedge clk) $rose(psel) |=> $rose(penable);

endproperty: p_psel_rose_next_cycle_penable_rise

assert property(p_psel_rose_next_cycle_penable_rise) else `uvm_error("ASSERT", "PENABLE not rose after 1 cycle PSEL rose")

property p_penable_rose_next_cycle_fall;

@(posedge clk) penable && pready |=> $fell(penable);

endproperty: p_penable_rose_next_cycle_fall

assert property(p_penable_rose_next_cycle_fall) else `uvm_error("ASSERT", "PENABLE not fall after 1 cycle PENABLE rose")

property p_pwdata_stable_during_trans_phase;

@(posedge clk) ((psel && !penable) ##1 (psel && penable)) |-> $stable(pwdata);

endproperty: p_pwdata_stable_during_trans_phase

assert property(p_pwdata_stable_during_trans_phase) else `uvm_error("ASSERT", "PWDATA not stable during transaction phase")

property p_paddr_stable_until_next_trans;

logic[31:0] addr1, addr2;

@(posedge clk) first_match(($rose(penable),addr1=paddr) ##1 ((psel && !penable)[=1],addr2=$past(paddr))) |-> addr1 == addr2;

endproperty: p_paddr_stable_until_next_trans

assert property(p_paddr_stable_until_next_trans) else `uvm_error("ASSERT", "PADDR not stable until next transaction start")

property p_pwrite_stable_until_next_trans;

logic pwrite1, pwrite2;

@(posedge clk) first_match(($rose(penable),pwrite1=pwrite) ##1 ((psel && !penable)[=1],pwrite2=$past(pwrite))) |-> pwrite1 == pwrite2;

endproperty: p_pwrite_stable_until_next_trans

assert property(p_pwrite_stable_until_next_trans) else `uvm_error("ASSERT", "PWRITE not stable until next transaction start")

property p_prdata_available_once_penable_rose;

@(posedge clk) penable && !pwrite && pready |-> !$stable(prdata);

endproperty: p_prdata_available_once_penable_rose

assert property(p_prdata_available_once_penable_rose) else `uvm_error("ASSERT", "PRDATA not available once PENABLE rose")

//property覆盖率

//和上面的区别是这里是收集覆盖率

//第一个是非连续写操作

property p_write_during_nonburst_trans;

@(posedge clk) $rose(penable) |-> pwrite throughout (##1 (!penable)[*2] ##1 penable[=1]);

endproperty: p_write_during_nonburst_trans

cover property(p_write_during_nonburst_trans);

property p_write_during_burst_trans;

@(posedge clk) $rose(penable) |-> pwrite throughout (##2 penable);

endproperty: p_write_during_burst_trans

cover property(p_write_during_burst_trans);

property p_write_read_burst_trans;

logic[31:0] addr;

@(posedge clk) ($rose(penable) && pwrite, addr=paddr) |-> (##2 ($rose(penable) && !pwrite && addr==paddr));

endproperty: p_write_read_burst_trans

cover property(p_write_read_burst_trans);

property p_write_twice_read_burst_trans;

logic[31:0] addr;

@(posedge clk) ($rose(penable) && pwrite, addr=paddr) |-> (##2 ($rose(penable) && pwrite && addr==paddr) ##2 ($rose(penable) && !pwrite && addr==paddr) );

endproperty: p_write_twice_read_burst_trans

cover property(p_write_twice_read_burst_trans);

property p_read_during_nonburst_trans;

@(posedge clk) $rose(penable) |-> !pwrite throughout (##1 (!penable)[*2] ##1 penable[=1]);

endproperty: p_read_during_nonburst_trans

cover property(p_read_during_nonburst_trans);

property p_read_during_burst_trans;

@(posedge clk) $rose(penable) |-> !pwrite throughout (##2 penable);

endproperty: p_read_during_burst_trans

cover property(p_read_during_burst_trans);

property p_read_write_read_burst_trans;

logic[31:0] addr;

@(posedge clk) ($rose(penable) && pwrite, addr=paddr) |-> ##2 ($rose(penable) && !pwrite && addr==paddr);

endproperty: p_read_write_read_burst_trans

cover property(p_read_write_read_burst_trans);

//控制断言的开关

initial begin: assertion_control

fork

forever begin

wait(rstn == 0);

$assertoff();

wait(rstn == 1);

if(has_checks) $asserton();

end

join_none

end

endinterface : apb_if

`endif // APB_IF_SV

tb中的接口

bind_intf是什么接口?印象中好像是什么绑定接口

`timescale 1ns/1ps

`include "apb_if.sv"//上面的apb接口include了

//node的接口,不包含slv_en_i和给下线的信号,为什么?

interface chnl_intf(input clk, input rstn);

logic [31:0] ch_data;

logic ch_data_p;

logic ch_valid;

logic ch_wait;

logic ch_parity_err;

clocking drv_ck @(posedge clk);//驱动时钟块,channel是指哪个模块的?

default input #1ps output #1ps;

output ch_data, ch_valid, ch_data_p;

input ch_wait, ch_parity_err;

endclocking

clocking mon_ck @(posedge clk);//给到monitor的信号全部为input

default input #1ps output #1ps;

input ch_data, ch_valid, ch_data_p, ch_wait, ch_parity_err;

endclocking

endinterface

//fmt接口,只打包与外界的五个信号,fmt输出的这里作为输入

interface fmt_intf(input clk, input rstn);

logic fmt_ready;

logic fmt_valid;

logic [31:0] fmt_data;

logic fmt_first;

logic fmt_last;

clocking drv_ck @(posedge clk);

default input #1ps output #1ps;

input fmt_valid, fmt_data, fmt_first, fmt_last;

output fmt_ready;

endclocking

clocking mon_ck @(posedge clk);

default input #1ps output #1ps;

input fmt_ready, fmt_valid, fmt_data, fmt_first, fmt_last;

endclocking

endinterface

//mcdf的接口打包reg_if、chnl_if、fmt_if里面没有的信号

interface mcdf_intf(output logic clk, output logic rstn);

logic [3:0] chnl_en; //node中的slv_en_i

clocking mon_ck @(posedge clk);

default input #1ps output #1ps;

input chnl_en;

endclocking

//产生clk

initial begin

clk <= 0;

forever begin

#5 clk <= !clk;

end

end

//复位信号

initial begin

#10 rstn <= 0;

repeat(10) @(posedge clk);

rstn <= 1;

end

endinterface

//这是什么接口?

interface bind_intf(

input logic [5:0] slv0_freeslot_bind,

input logic [5:0] slv1_freeslot_bind,

input logic [5:0] slv2_freeslot_bind,

input logic [5:0] slv3_freeslot_bind

);

endinterfacetb后续

module tb;

logic clk;

logic rstn;

//顶层MCDF所有信号与刚才定义的接口进行连接

mcdf dut(

.clk_i (clk ) ,

.rst_n_i (rstn ) ,

.slv0_data_i (chnl0_if.ch_data ) ,

.slv0_data_p_i (chnl0_if.ch_data_p ) ,

.slv0_valid_i (chnl0_if.ch_valid ) ,

.slv0_wait_o (chnl0_if.ch_wait ) ,

.slv0_parity_err_o (chnl0_if.ch_parity_err ) ,

.slv1_data_i (chnl1_if.ch_data ) ,

.slv1_data_p_i (chnl1_if.ch_data_p ) ,

.slv1_valid_i (chnl1_if.ch_valid ) ,

.slv1_wait_o (chnl1_if.ch_wait ) ,

.slv1_parity_err_o (chnl1_if.ch_parity_err ) ,

.slv2_data_i (chnl2_if.ch_data ) ,

.slv2_data_p_i (chnl2_if.ch_data_p ) ,

.slv2_valid_i (chnl2_if.ch_valid ) ,

.slv2_wait_o (chnl2_if.ch_wait ) ,

.slv2_parity_err_o (chnl2_if.ch_parity_err ) ,

.slv3_data_i (chnl3_if.ch_data ) ,

.slv3_data_p_i (chnl3_if.ch_data_p ) ,

.slv3_valid_i (chnl3_if.ch_valid ) ,

.slv3_wait_o (chnl3_if.ch_wait ) ,

.slv3_parity_err_o (chnl3_if.ch_parity_err ) ,

.paddr_i (reg_if.paddr[7:0] ) ,

.pwr_i (reg_if.pwrite ) ,

.pen_i (reg_if.penable ) ,

.psel_i (reg_if.psel ) ,

.pwdata_i (reg_if.pwdata ) ,

.prdata_o (reg_if.prdata ) ,

.pready_o (reg_if.pready ) ,

.pslverr_o (reg_if.pslverr ) ,

.rev_rdy_i (fmt_if.fmt_ready ) ,

.pkg_vld_o (fmt_if.fmt_valid ) ,

.pkg_dat_o (fmt_if.fmt_data ) ,

.pkg_fst_o (fmt_if.fmt_first ) ,

.pkg_lst_o (fmt_if.fmt_last )

);

import uvm_pkg::*;

`include "uvm_macros.svh"

import mcdf_pkg::*;

apb_if reg_if(.*);

chnl_intf chnl0_if(.*);

chnl_intf chnl1_if(.*);

chnl_intf chnl2_if(.*);

chnl_intf chnl3_if(.*);

fmt_intf fmt_if(.*);

mcdf_intf mcdf_if(.*);

// mcdf interface monitoring MCDF ports and signals

assign mcdf_if.chnl_en = tb.dut.inst_reg_if.slv_en_o;

initial begin

// do interface configuration from top tb (HW) to verification env (SW)

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.chnl_agts[0]", "vif", chnl0_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.chnl_agts[1]", "vif", chnl1_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.chnl_agts[2]", "vif", chnl2_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.chnl_agts[3]", "vif", chnl3_if);

uvm_config_db#(virtual apb_if )::set(uvm_root::get(), "uvm_test_top.env.reg_agt", "vif", reg_if );

uvm_config_db#(virtual fmt_intf )::set(uvm_root::get(), "uvm_test_top.env.fmt_agt", "vif", fmt_if );

uvm_config_db#(virtual mcdf_intf)::set(uvm_root::get(), "uvm_test_top.env.*", "mcdf_vif", mcdf_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.*", "chnl_vifs[0]", chnl0_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.*", "chnl_vifs[1]", chnl1_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.*", "chnl_vifs[2]", chnl2_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.*", "chnl_vifs[3]", chnl3_if);

uvm_config_db#(virtual apb_if )::set(uvm_root::get(), "uvm_test_top.env.*", "reg_vif", reg_if );

uvm_config_db#(virtual fmt_intf )::set(uvm_root::get(), "uvm_test_top.env.*", "fmt_vif", fmt_if );

// If no external configured via +UVM_TESTNAME=my_test, the default test is

// mcdf_data_consistence_basic_test

run_test("mcdf_data_consistence_basic_test");

end

//--------------------------------------------------------

// Example for how to probe signals

//--------------------------------------------------------

logic [5:0] slv0_freeslot_vlog, slv1_freeslot_vlog, slv2_freeslot_vlog, slv3_freeslot_vlog;

logic [5:0] slv0_freeslot_mti, slv1_freeslot_mti, slv2_freeslot_mti, slv3_freeslot_mti;

logic [5:0] slv0_freeslot_vcs, slv1_freeslot_vcs, slv2_freeslot_vcs, slv3_freeslot_vcs;

// Verilog hierarchy probe

assign slv0_freeslot_vlog = tb.dut.slv0_freeslot_s;

assign slv1_freeslot_vlog = tb.dut.slv1_freeslot_s;

assign slv2_freeslot_vlog = tb.dut.slv2_freeslot_s;

assign slv3_freeslot_vlog = tb.dut.slv3_freeslot_s;

// Questasim supplied probe

// initial begin

// $init_signal_spy("tb.dut.slv0_freeslot_s", "tb.slv0_freeslot_mti");

// $init_signal_spy("tb.dut.slv1_freeslot_s", "tb.slv1_freeslot_mti");

// $init_signal_spy("tb.dut.slv2_freeslot_s", "tb.slv2_freeslot_mti");

// $init_signal_spy("tb.dut.slv3_freeslot_s", "tb.slv3_freeslot_mti");

// end

// VCS supplied probe

initial begin

$hdl_xmr("tb.dut.slv0_freeslot_s", "tb.slv0_freeslot_vcs");

$hdl_xmr("tb.dut.slv1_freeslot_s", "tb.slv1_freeslot_vcs");

$hdl_xmr("tb.dut.slv2_freeslot_s", "tb.slv2_freeslot_vcs");

$hdl_xmr("tb.dut.slv3_freeslot_s", "tb.slv3_freeslot_vcs");

end

//括号内是RTL的信号

bind tb.dut bind_intf bind_if0(

.slv0_freeslot_bind(slv0_freeslot_s)

,.slv1_freeslot_bind(slv1_freeslot_s)

,.slv2_freeslot_bind(slv2_freeslot_s)

,.slv3_freeslot_bind(slv3_freeslot_s)

);

endmodule软件部分

chnl_pkg

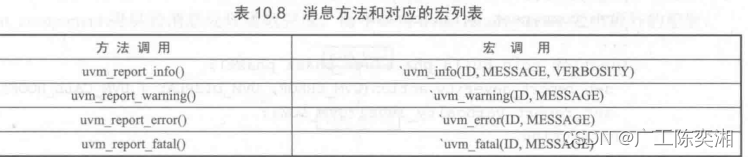

消息方法对应4个宏:

`uvm_info(ID, 信息内容,过滤级别),warning和error和fatal没有过滤级别这个参数。

ID可以用get_type_name()获取,信息内容可以“”也可以是字符串s

过滤级别有4个:UVM_HIGH,UVM_MEDIUM,UVM_LOW,UVM_NONE

sequence中有个宏`uvm_declare_p_sequencer(chnl_sequencer),将chnl_sequencer转换成了p_sequencer,相当于?

chnl_sequencer p_sequencer;

也就是用了这个宏进行转换,不需要再声明,记住结论:在sequence中要用,参数是当前的sequencer

uvm_declare_p_sequencer_zilan23的博客-CSDN博客_uvm_declare_p_sequencer

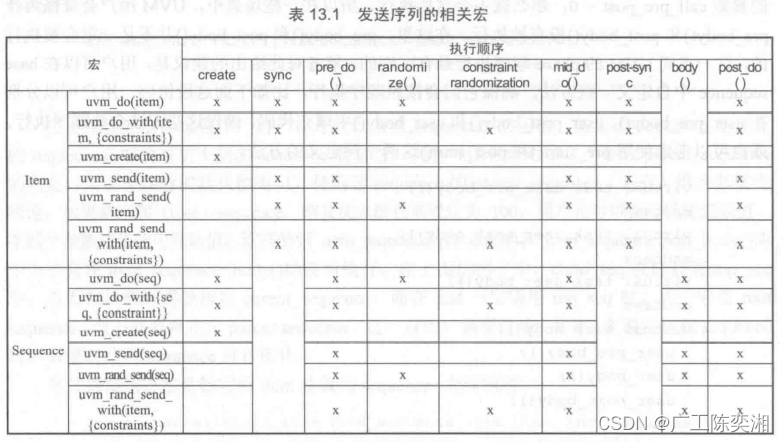

发送序列用的宏

uvm_do_with对于item来说,创建了item,同步,做约束的随机化,发送

顶层环境中,根据uvm的config机制,配置接口:在tb的initial块中做

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.chnl_agts[0]", "vif", chnl0_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.chnl_agts[1]", "vif", chnl1_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.chnl_agts[2]", "vif", chnl2_if);

uvm_config_db#(virtual chnl_intf)::set(uvm_root::get(), "uvm_test_top.env.chnl_agts[3]", "vif", chnl3_if);

在agent的build_phase中做:

if(!uvm_config_db#(virtual chnl_intf)::get(this,"","vif", vif)) begin

`uvm_fatal("GETVIF","cannot get vif handle from config DB")

end

我的第二个UVM代码——连接interface - 腾讯云开发者社区-腾讯云

//接下来进入软件验证环境的搭建,chnl_pkg对应node,先看结构

//首先由于用到UVM,开头的import和include少不了

//node有需要传输的数据,传输数据需要用到seq、sqeuencer、driver,检测数据的monitor,包含这几个结构的agent

package chnl_pkg;

import uvm_pkg::*;

`include "uvm_macros.svh"

//sequence item继承于uvm_transaction——uvm_object

//seq item的创建和随机化发生在seq中的body任务

class chnl_trans extends uvm_sequence_item;

rand bit[31:0] data[];//成员变量全部为随机变量rand,数据类型用动态数组

rand int ch_id;

rand int pkt_id;

rand int data_nidles;

rand int pkt_nidles;

bit rsp;//单比特rsp在写入数据并转换句柄后点亮表示完成写入

//对成员变量做soft约束也就是初始化,具体在发包的时候会做随机化替代这里的初始化

constraint cstr{

//数据位宽在4到32位之间

soft data.size inside {[4:32]};

//数据之间按一定规律生成

foreach(data[i]) soft data[i] == 'hC000_0000 + (this.ch_id<<24) + (this.pkt_id<<8) + i;

//通道id和包的id默认是0

soft ch_id == 0;

soft pkt_id == 0;

//数据间隔和包的间隔在一定范围内,这跟idle_cycle有关?

soft data_nidles inside {[0:2]};

soft pkt_nidles inside {[1:10]};

};

//注册,由于有成员变量,做域的自动化

`uvm_object_utils_begin(chnl_trans)

`uvm_field_array_int(data, UVM_ALL_ON)

`uvm_field_int(ch_id, UVM_ALL_ON)

`uvm_field_int(pkt_id, UVM_ALL_ON)

`uvm_field_int(data_nidles, UVM_ALL_ON)

`uvm_field_int(pkt_nidles, UVM_ALL_ON)

`uvm_field_int(rsp, UVM_ALL_ON)

`uvm_object_utils_end

//每个class必做的new函数,由于是object类,只有name

function new (string name = "chnl_trans");

super.new(name);

endfunction

endclass: chnl_trans

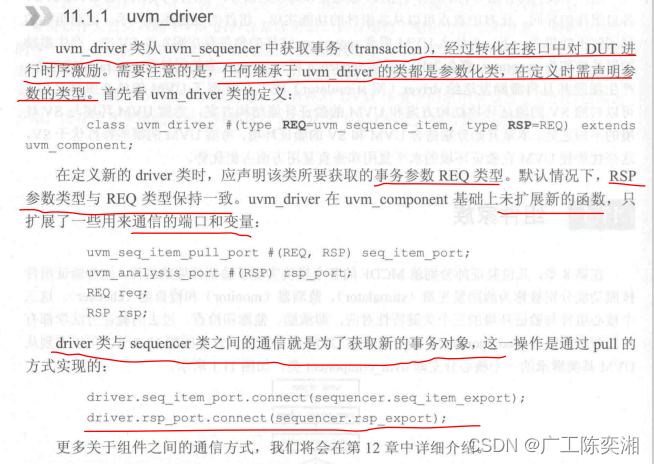

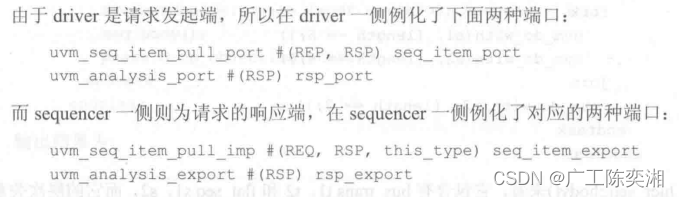

//driver的工作原理:通过seq_item_port从sequencer拿到一个seq_item,写入数据后返回rsp句柄,通过seq_item_port.item_done(rsp);结束发送

//注意是参数类#(chnl_trans)

class chnl_driver extends uvm_driver #(chnl_trans);

//注意这里就有接口了

local virtual chnl_intf intf;

//每个class都要的注册,无成员变量,不需要域的自动化

`uvm_component_utils(chnl_driver)

//component的new函数有两个参数(和object区分)

function new (string name = "chnl_driver", uvm_component parent);

super.new(name, parent);

endfunction

//由于有接口,要将接口连接到driver

function void set_interface(virtual chnl_intf intf);

if(intf == null)

$error("interface handle is NULL, please check if target interface has been intantiated");

else

this.intf = intf;

endfunction

//uvm_component的phase机制,只有run_phase是耗时的任务

//driver的run_phase同时执行了驱动和复位两个线程

task run_phase(uvm_phase phase);

fork

this.do_drive();

this.do_reset();

join

endtask

task do_reset();

forever begin//intf是这里定义的chnl_intf接口名,对应tb中的接口

@(negedge intf.rstn);

intf.ch_valid <= 0;//这三个是输出的三个信号。不空就valid

intf.ch_data <= 0;

intf.ch_data_p <= 0;

end

endtask

//驱动包的任务,声明两个item的句柄,通过seq_item_port调用get_next_item(req)方法

//拿到item,然后执行驱动任务chnl_write,通过接口中的时钟块点亮三个输出端数据

//等待:奇偶校验无错误、FIFO不满、slv_en_i为高,则wait拉低,包得到传送

//然后根据包中的data_nidles和pkt_nidles执行chnl_idle()

//完成以上驱动任务后将包的句柄进行克隆,由于item继承于object,克隆得到的句柄是父类句柄,需要将其转换成子类句柄

//点亮转换后的单比特rsp表示完成包的驱动,通过seq_item_port.item_done(rsp)返回rsp给sequence

task do_drive();

chnl_trans req, rsp;

@(posedge intf.rstn);

forever begin

seq_item_port.get_next_item(req);

this.chnl_write(req);

void'($cast(rsp, req.clone()));

rsp.rsp = 1;

//item中没有定义的函数,应该是自带的函数,从req获取seq id作为rsp的设置seq id的参数

rsp.set_sequence_id(req.get_sequence_id());

seq_item_port.item_done(rsp);

end

endtask

//driver和sequencer之间通信的tlm端口如下:采取get模式

//driver作为initiator,例化了两个端口,默认的REQ类型是uvm_sequence_item父类

//uvm_seq_item_pull_port #(REQ, RSP) seq_item_port

//uvm_analysis_port #(RSP) rsp_port

task chnl_write(input chnl_trans t);

foreach(t.data[i]) begin

@(posedge intf.clk);

intf.drv_ck.ch_valid <= 1;

intf.drv_ck.ch_data <= t.data[i];

intf.drv_ck.ch_data_p <= get_parity(t.data[i]);

@(negedge intf.clk);

wait(intf.ch_wait === 'b0);

//消息打印第一个参数ID用get_type_name获得类型名,第二个参数打印内容用

//系统函数sformatf再写,第三个参数过滤级别为HIGH

`uvm_info(get_type_name(), $sformatf("sent data 'h%8x", t.data[i]), UVM_HIGH)

//get_type_name获取的可能是item的类型,对应seq,针对多个seq同时向sequencer发包

repeat(t.data_nidles) chnl_idle();

end

repeat(t.pkt_nidles) chnl_idle();

endtask

task chnl_idle();

@(posedge intf.clk);

intf.drv_ck.ch_valid <= 0;

intf.drv_ck.ch_data <= 0;

intf.drv_ck.ch_data_p <= 0;

endtask

function get_parity(bit[31:0] data);

return ^data;//对32位数据缩位异或可得奇偶校验位

endfunction

endclass: chnl_driver

//sequencer只需要注册和new函数,注意是参数类#(chnl_trans)

//sequencer继承于sequencer_base——component,所以也是两个参数

class chnl_sequencer extends uvm_sequencer #(chnl_trans);

`uvm_component_utils(chnl_sequencer)

function new (string name = "chnl_sequencer", uvm_component parent);

super.new(name, parent);

endfunction

endclass: chnl_sequencer

//sequence继承于item——transaction——object,item在这产生

class chnl_data_sequence extends uvm_sequence #(chnl_trans);

rand int pkt_id = 0;//定义的时候就赋值

rand int ch_id = -1;

rand int data_nidles = -1;

rand int pkt_nidles = -1;

rand int data_size = -1;

rand int ntrans = 10;//包的数量?

rand int data[];

constraint cstr{//这里约束为什么是-1?

soft pkt_id == 0;

soft ch_id == -1;

soft data_nidles == -1;

soft pkt_nidles == -1;

soft data_size == -1;

soft ntrans == 10;

soft data.size() == data_size;

foreach(data[i]) soft data[i] == -1;

};

`uvm_object_utils_begin(chnl_data_sequence)

`uvm_field_int(pkt_id, UVM_ALL_ON)

`uvm_field_int(ch_id, UVM_ALL_ON)

`uvm_field_int(data_nidles, UVM_ALL_ON)

`uvm_field_int(pkt_nidles, UVM_ALL_ON)

`uvm_field_int(data_size, UVM_ALL_ON)

`uvm_field_int(ntrans, UVM_ALL_ON)

`uvm_object_utils_end

//将p_sequencer设置成chnl_sequencer

`uvm_declare_p_sequencer(chnl_sequencer)

function new (string name = "chnl_data_sequence");

super.new(name);

endfunction

task body();

repeat(ntrans) send_trans();

endtask

task send_trans();

chnl_trans req, rsp;

//发送item的宏,第一个参数是发送的item的句柄,第二个参数是约束随机化

//约束块,这里是条件约束,在这个class中如果这五个成员变量大于等于0,就赋给

`uvm_do_with(req, {local::ch_id >= 0 -> ch_id == local::ch_id;

local::pkt_id >= 0 -> pkt_id == local::pkt_id;

local::data_nidles >= 0 -> data_nidles == local::data_nidles;

local::pkt_nidles >= 0 -> pkt_nidles == local::pkt_nidles;

local::data_size >0 -> data.size() == local::data_size;

foreach(local::data[i]) local::data[i] >= 0 -> data[i] == local::data[i];

})//这里的随机化只针对一个包,然后重复ntrans次

this.pkt_id++;//包的id加一

`uvm_info(get_type_name(), req.sprint(), UVM_HIGH)

get_response(rsp);//sequence从driver那获得rsp表示完成一次握手

`uvm_info(get_type_name(), rsp.sprint(), UVM_HIGH)

assert(rsp.rsp)//做个断言,若rsp不点亮则报错,why is 断言?

else $error("[RSPERR] %0t error response received!", $time);

endtask

function void post_randomize();//随机化之后打印

string s;

s = {s, "AFTER RANDOMIZATION n"};

s = {s, "=======================================n"};

s = {s, "chnl_data_sequence object content is as below: n"};

s = {s, super.sprint()};

s = {s, "=======================================n"};

`uvm_info(get_type_name(), s, UVM_HIGH)

endfunction

endclass: chnl_data_sequence

typedef struct packed {//packed表示合并,结构体可以存放不同数据类型的变量

//typedef定义新的类型,32位的data和2位id合起来称为mon_data_t

bit[31:0] data;

bit[1:0] id;

} mon_data_t;

//monitor没有太多介绍,继承于comp,处理方法和其他comp类似

class chnl_monitor extends uvm_monitor;

//在接口中声明过monitor的时钟块和驱动的时钟块

//由于要接入信号,也要用到接口,同样声明一个monitor中的local接口

local virtual chnl_intf intf;

uvm_analysis_port #(mon_data_t) mon_ana_port;

//analysis port是一initiator对多target的应用,push模式,从port调用各个target的write函数实现数据传输

//需要在顶层进行analysis port和imp的连接,在initiator调用write

`uvm_component_utils(chnl_monitor)

function new(string name="chnl_monitor", uvm_component parent);

super.new(name, parent);

//ap不是组件自带的,要用户声明后在new函数例化

mon_ana_port = new("mon_ana_port", this);

endfunction

function void set_interface(virtual chnl_intf intf);

if(intf == null)//配置接口

$error("interface handle is NULL, please check if target interface has been intantiated");

else

this.intf = intf;

endfunction

task run_phase(uvm_phase phase);

this.mon_trans();//comp的子类,phase机制

endtask

task mon_trans();

mon_data_t m;

forever begin//在valid拉高wait拉低时才采集

@(intf.mon_ck iff (intf.mon_ck.ch_valid==='b1 && intf.mon_ck.ch_wait==='b0));

m.data = intf.mon_ck.ch_data;

mon_ana_port.write(m);//initiator端调用write函数,参数是句柄

`uvm_info(get_type_name(), $sformatf("monitored channel data 'h%8x", m.data), UVM_HIGH)

end

endtask

endclass: chnl_monitor

//agent作为chnl_pkg的顶层,build_phase获取接口,例化3个comp

//例化用 组件名=类名::type_id::create(“组件名”,this)

//connect_phase连接driver和sequencer,并把接口连上

class chnl_agent extends uvm_agent;

chnl_driver driver;

chnl_monitor monitor;

chnl_sequencer sequencer;

local virtual chnl_intf vif;

`uvm_component_utils(chnl_agent)

function new(string name = "chnl_agent", uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

//#(配置的类型),this,"","vif"为存储路径,vif为传递的接口(已声明)

if(!uvm_config_db#(virtual chnl_intf)::get(this,"","vif", vif)) begin

`uvm_fatal("GETVIF","cannot get vif handle from config DB")

end

driver = chnl_driver::type_id::create("driver", this);

monitor = chnl_monitor::type_id::create("monitor", this);

sequencer = chnl_sequencer::type_id::create("sequencer", this);

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

driver.seq_item_port.connect(sequencer.seq_item_export);

this.set_interface(vif);

endfunction

function void set_interface(virtual chnl_intf vif);

driver.set_interface(vif);

monitor.set_interface(vif);

endfunction

endclass: chnl_agent

endpackage

fmt_pkg

复习mailbox

SV--线程(mailbox)_ICer吼吼的博客-CSDN博客_sv中mailbox

//和硬件fmt对比了一下,感觉硬件和软件写的模型不太一样,这里fifo和带宽会变

package fmt_pkg;

import uvm_pkg::*;

`include "uvm_macros.svh"

//枚举类型:FIFO深度和数据位宽

typedef enum {SHORT_FIFO, MED_FIFO, LONG_FIFO, ULTRA_FIFO} fmt_fifo_t;

typedef enum {LOW_WIDTH, MED_WIDTH, HIGH_WIDTH, ULTRA_WIDTH} fmt_bandwidth_t;

//结构是一样的,从item开始

//将fifo深度和带宽声明为随机变量

class fmt_trans extends uvm_sequence_item;

rand fmt_fifo_t fifo;

rand fmt_bandwidth_t bandwidth;

bit [7:0] length;

bit [31:0] data[];

bit [7:0] ch_id;

bit [31:0] parity;

bit rsp;

constraint cstr{//默认为medium

soft fifo == MED_FIFO;

soft bandwidth == MED_WIDTH;

};

`uvm_object_utils_begin(fmt_trans)

`uvm_field_enum(fmt_fifo_t, fifo, UVM_ALL_ON)

`uvm_field_enum(fmt_bandwidth_t, bandwidth, UVM_ALL_ON)

`uvm_field_int(length, UVM_ALL_ON)

`uvm_field_array_int(data, UVM_ALL_ON)

`uvm_field_int(ch_id, UVM_ALL_ON)

`uvm_field_int(rsp, UVM_ALL_ON)

`uvm_object_utils_end

function new (string name = "fmt_trans");

super.new(name);

endfunction

endclass

//driver

class fmt_driver extends uvm_driver #(fmt_trans);

local virtual fmt_intf intf;

local mailbox #(bit[31:0]) fifo;

local int fifo_bound;

local int data_consum_peroid;

`uvm_component_utils(fmt_driver)

function new (string name = "fmt_driver", uvm_component parent);

super.new(name, parent);

this.fifo = new();//mailbox需要例化

this.fifo_bound = 4096;//fifo深度初始化

this.data_consum_peroid = 1;//带宽初始化

endfunction

function void set_interface(virtual fmt_intf intf);

if(intf == null)

$error("interface handle is NULL, please check if target interface has been intantiated");

else

this.intf = intf;

endfunction

task run_phase(uvm_phase phase);

fork

this.do_receive();

this.do_consume();

this.do_config();

this.do_reset();

join

endtask

task do_config();

fmt_trans req, rsp;

forever begin//从seq拿到item

seq_item_port.get_next_item(req);

case(req.fifo)//看看里面的随机变量fifo深度是哪个

SHORT_FIFO: this.fifo_bound = 64;

MED_FIFO: this.fifo_bound = 256;

LONG_FIFO: this.fifo_bound = 512;

ULTRA_FIFO: this.fifo_bound = 2048;

endcase

//把得到的深度作为参数例化给当前类的邮箱fifo

this.fifo = new(this.fifo_bound);

case(req.bandwidth)//看看里面的随机变量带宽是哪个,带宽越大消化时间越短

LOW_WIDTH: this.data_consum_peroid = 8;

MED_WIDTH: this.data_consum_peroid = 4;

HIGH_WIDTH: this.data_consum_peroid = 2;

ULTRA_WIDTH: this.data_consum_peroid = 1;

endcase

//其他操作是一样的

void'($cast(rsp, req.clone()));

rsp.rsp = 1;

rsp.set_sequence_id(req.get_sequence_id());

seq_item_port.item_done(rsp);

end

endtask

task do_reset();

forever begin

@(negedge intf.rstn)

intf.fmt_ready <= 0;//根据接口,output只有一个fmt_ready

end

endtask

task do_receive();//fmt接收来自node的data,就是存进fifo

forever begin

@(intf.drv_ck); #10ps;

if(intf.fmt_valid === 1'b1) begin//实验0里面的grant信号

forever begin

if((this.fifo_bound-this.fifo.num()) >= 1)//why?

break;//如果fifo容量和实际存储的数量的差大于等于1就停止

@(intf.drv_ck); #10ps;

end

this.fifo.put(intf.fmt_data);

#1ps; intf.fmt_ready <= 1;

end//接收完数据后拉高ready

else begin

#1ps; intf.fmt_ready <= 0;

end

end

endtask

task do_consume();//消化数据需要一定时间,但是为什么用随机范围?

bit[31:0] data;

forever begin

void'(this.fifo.try_get(data));

repeat($urandom_range(1, this.data_consum_peroid)) @(posedge intf.clk);

end

endtask

endclass: fmt_driver

//sequencer依然是注册和new函数即可

class fmt_sequencer extends uvm_sequencer #(fmt_trans);

`uvm_component_utils(fmt_sequencer)

function new (string name = "fmt_sequencer", uvm_component parent);

super.new(name, parent);

endfunction

endclass: fmt_sequencer

//sequence做item的随机化和在body中发送,做p_sequencer的宏

class fmt_config_sequence extends uvm_sequence #(fmt_trans);

rand fmt_fifo_t fifo = MED_FIFO;

rand fmt_bandwidth_t bandwidth = MED_WIDTH;

constraint cstr{

soft fifo == MED_FIFO;

soft bandwidth == MED_WIDTH;

}

`uvm_object_utils_begin(fmt_config_sequence)

`uvm_field_enum(fmt_fifo_t, fifo, UVM_ALL_ON)

`uvm_field_enum(fmt_bandwidth_t, bandwidth, UVM_ALL_ON)

`uvm_object_utils_end

`uvm_declare_p_sequencer(fmt_sequencer)

function new (string name = "fmt_config_sequence");

super.new(name);

endfunction

task body();//是body不是run_phase

send_trans();

endtask

task send_trans();

fmt_trans req, rsp;

`uvm_do_with(req, {local::fifo != MED_FIFO -> fifo == local::fifo;

local::bandwidth != MED_WIDTH -> bandwidth == local::bandwidth;

})//随机化只要和初始化的不一样就做更改,寄存器会配置

`uvm_info(get_type_name(), req.sprint(), UVM_HIGH)

get_response(rsp);

`uvm_info(get_type_name(), rsp.sprint(), UVM_HIGH)

assert(rsp.rsp)//其他的相同

else $error("[RSPERR] %0t error response received!", $time);

endtask

function void post_randomize();

string s;

s = {s, "AFTER RANDOMIZATION n"};

s = {s, "=======================================n"};

s = {s, "fmt_config_sequence object content is as below: n"};

s = {s, super.sprint()};

s = {s, "=======================================n"};

`uvm_info(get_type_name(), s, UVM_HIGH)

endfunction

endclass: fmt_config_sequence

// formatter monitor

class fmt_monitor extends uvm_monitor;

local string name;

local virtual fmt_intf intf;

uvm_analysis_port #(fmt_trans) mon_ana_port;

`uvm_component_utils(fmt_monitor)

function new(string name="fmt_monitor", uvm_component parent);

super.new(name, parent);

mon_ana_port = new("mon_ana_port", this);

endfunction

function void set_interface(virtual fmt_intf intf);

if(intf == null)

$error("interface handle is NULL, please check if target interface has been intantiated");

else

this.intf = intf;

endfunction

task run_phase(uvm_phase phase);

this.mon_trans();

endtask

//chnl_pkg没有例化item,为什么这里就要例化?

task mon_trans();

fmt_trans m;

string s;

forever begin//first、valid、ready拉高才开始读数据

@(intf.mon_ck iff intf.mon_ck.fmt_first && intf.mon_ck.fmt_valid && intf.mon_ck.fmt_ready);

m = new();//为什么这里就要例化?

//由fmt数据包格式的图可知id和length是高16位

m.length = intf.mon_ck.fmt_data[23:16];

m.ch_id = intf.mon_ck.fmt_data[31:24];

//动态数组分配空间,length+1是payload的数量,加上包头包尾+2

//所以这里需要length+3的空间。还是看数据包的图

m.data = new[m.length + 3];

foreach(m.data[i]) begin

m.data[i] = intf.mon_ck.fmt_data;

//size-1表示数据最高位是奇偶校验位

if(i == m.data.size()-1) m.parity = m.data[i];

if(i < m.data.size()-1) @(intf.mon_ck iff intf.mon_ck.fmt_valid && intf.mon_ck.fmt_ready);

end//奇偶校验位以外的是数据位

mon_ana_port.write(m);

s = $sformatf("=======================================n");

s = {s, $sformatf("%0t %s monitored a packet: n", $time, this.m_name)};

s = {s, $sformatf("length = %0d: n", m.length)};

s = {s, $sformatf("chid = %0d: n", m.ch_id)};

foreach(m.data[i]) s = {s, $sformatf("data[%0d] = %8x n", i, m.data[i])};

s = {s, $sformatf("=======================================n")};

`uvm_info(get_type_name(), s, UVM_HIGH)

end

endtask

endclass: fmt_monitor

//agent顶层环境做的事情完全一样

class fmt_agent extends uvm_agent;

fmt_driver driver;//声明三个组件和接口

fmt_monitor monitor;

fmt_sequencer sequencer;

local virtual fmt_intf vif;

`uvm_component_utils(fmt_agent) //注册和new函数

function new(string name = "chnl_agent", uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

//build_phase get接口,例化三个组件

if(!uvm_config_db#(virtual fmt_intf)::get(this,"","vif", vif)) begin

`uvm_fatal("GETVIF","cannot get vif handle from config DB")

end

driver = fmt_driver::type_id::create("driver", this);

monitor = fmt_monitor::type_id::create("monitor", this);

sequencer = fmt_sequencer::type_id::create("sequencer", this);

endfunction

//connect phase连接driver和sequencer,调用set_interface连接接口

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

driver.seq_item_port.connect(sequencer.seq_item_export);

this.set_interface(vif);

endfunction

function void set_interface(virtual fmt_intf vif);

driver.set_interface(vif);

monitor.set_interface(vif);

endfunction

endclass

endpackage

mcdf_rgm_pkg

电力电子转战数字IC20220818day63——uvm入门实验5_广工陈奕湘的博客-CSDN博客

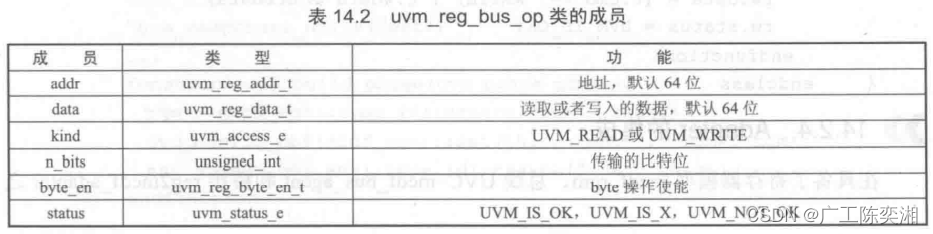

复习一下UVM的寄存器模型。寄存器自己操作的trans是uvm_reg_bus_op,通过adapter转化到mcdf的总线

关于set_coverage()

uvm设计分析——reg - _9_8 - 博客园

(30)UVM 寄存器模型的应用场景和功能覆盖率收集_数字IC小白的日常修炼的博客-CSDN博客_uvm_subscriber

覆盖率选项设置

Systemverilog(绿皮书)第九章——功能覆盖率(四)覆盖选项_胡九筒的博客-CSDN博客

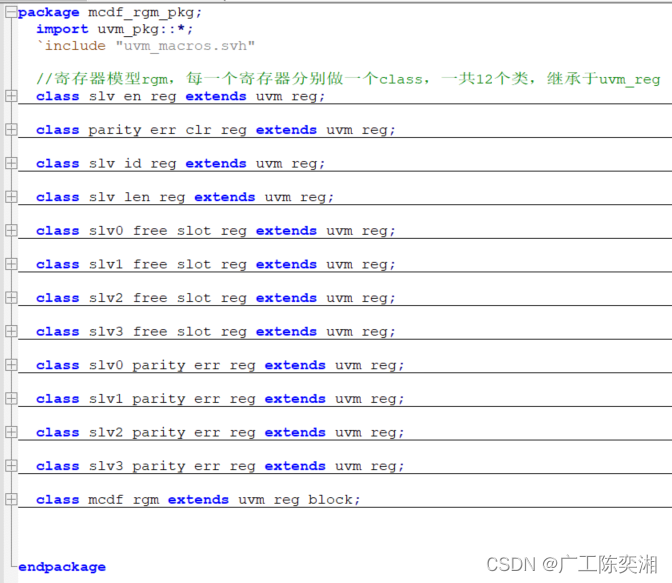

rgm_pkg只提供两个reg的代码即可,因为12个reg类的代码结构完全一样,只有域和值不一样,注意默认值的设置。rgm可以用工具生成。

电力电子转战数字IC20220824day68——uvm实战3_广工陈奕湘的博客-CSDN博客

关于uvm_reg_map

关于uvm_reg_map

[CU]reg model构建篇-uvm_reg_map(与前门访问相关) - _见贤_思齐 - 博客园

关于后门访问

//寄存器模型rgm,每一个寄存器分别做一个class,一共12个类,继承于uvm_reg

class slv_en_reg extends uvm_reg;

//每个class包含:注册+域的声明+覆盖组+new函数+build_phase+sample函数

//相当于只是做了覆盖组和例化和采样

`uvm_object_utils(slv_en_reg)

rand uvm_reg_field en;//[3:0]前4位是slv_en,其他位是预留位reserved

rand uvm_reg_field reserved;

covergroup value_cg;//两个域写成两个覆盖点组成一个覆盖组

option.per_instance = 1;

en: coverpoint en.value[3:0];

reserved: coverpoint reserved.value[31:4];

endgroup

//new函数有3个参数,name,寄存器位数32,是否要加入覆盖率的支持

function new(string name = "slv_en_reg");

super.new(name, 32, UVM_CVR_ALL);//若UVM_NO_COVERAGE,则不支持

//如果有覆盖率收集的需求,在new函数要set_coverage,然后例化覆盖组

void'(set_coverage(UVM_CVR_FIELD_VALS));

if(has_coverage(UVM_CVR_FIELD_VALS)) begin

value_cg = new();//覆盖组必须例化才会收集

end

endfunction

//build_phase例化+配置寄存器域

virtual function void build();

en = uvm_reg_field::type_id::create("en");

reserved = uvm_reg_field::type_id::create("reserved");

//配置域的参数:第一个是this,然后两个表示寄存器对应的位

//第四个参数表示寄存器属性,读写还是只读,后五个参数表示默认值

en.configure(this, 4, 0, "RW", 0, 'h0, 1, 0, 0);

reserved.configure(this, 28, 4, "RO", 0, 'h0, 1, 0, 0);

endfunction

//覆盖率采样函数,需要自定义

function void sample(

uvm_reg_data_t data,//寄存器操作的trans——uvm_reg_bus_op,见截图

uvm_reg_data_t byte_en,

bit is_read,

uvm_reg_map map//为什么连map也要?

);

//调用父类sample函数,输入参数相同

super.sample(data, byte_en, is_read, map);

sample_values(); //调用自定义sample_values函数

endfunction

function void sample_values();

super.sample_values();//也调用父类sample_values函数

//new函数set了,这里如果get就调用覆盖组的sample

if (get_coverage(UVM_CVR_FIELD_VALS)) begin

value_cg.sample();

end

endfunction

endclass

class parity_err_clr_reg extends uvm_reg;

`uvm_object_utils(parity_err_clr_reg)//注册

rand uvm_reg_field err_clr;//寄存器域声明

rand uvm_reg_field reserved;

covergroup value_cg;//覆盖组编写

option.per_instance = 1;

err_clr: coverpoint err_clr.value[3:0];

reserved: coverpoint reserved.value[31:4];

endgroup

function new(string name = "parity_err_clr_reg");

super.new(name, 32, UVM_CVR_ALL);

void'(set_coverage(UVM_CVR_FIELD_VALS));

if(has_coverage(UVM_CVR_FIELD_VALS)) begin

value_cg = new();

end

endfunction

virtual function void build();

err_clr = uvm_reg_field::type_id::create("err_clr");

reserved = uvm_reg_field::type_id::create("reserved");

err_clr.configure(this, 4, 0, "RW", 0, 'h0, 1, 0, 0);

reserved.configure(this, 28, 4, "RO", 0, 'h0, 1, 0, 0);

endfunction

function void sample(

uvm_reg_data_t data,

uvm_reg_data_t byte_en,

bit is_read,

uvm_reg_map map

);

super.sample(data, byte_en, is_read, map);

sample_values();

endfunction

function void sample_values();

super.sample_values();

if (get_coverage(UVM_CVR_FIELD_VALS)) begin

value_cg.sample();

end

endfunction

endclass顶层的mcdf_rgm类

关于配置寄存器的9个参数

UVM 中的寄存器模型

//最后的rgm就是寄存器的顶层环境

class mcdf_rgm extends uvm_reg_block;

`uvm_object_utils(mcdf_rgm)//注册

rand slv_en_reg slv_en;//声明所有reg为随机变量

rand parity_err_clr_reg parity_err_clr;

rand slv_id_reg slv_id;

rand slv_len_reg slv_len;

rand slv0_free_slot_reg slv0_free_slot;

rand slv1_free_slot_reg slv1_free_slot;

rand slv2_free_slot_reg slv2_free_slot;

rand slv3_free_slot_reg slv3_free_slot;

rand slv0_parity_err_reg slv0_parity_err;

rand slv1_parity_err_reg slv1_parity_err;

rand slv2_parity_err_reg slv2_parity_err;

rand slv3_parity_err_reg slv3_parity_err;

uvm_reg_map map;//map不要漏

function new(string name = "mcdf_rgm");

super.new(name, UVM_NO_COVERAGE);//顶层不收集覆盖率

endfunction

//build_phase对每一个reg进行:例化+调用configure配置+调用build

//对map进行例化

virtual function void build();

slv_en = slv_en_reg::type_id::create("slv_en");

slv_en.configure(this);

slv_en.build();

parity_err_clr = parity_err_clr_reg::type_id::create("parity_err_clr");

parity_err_clr.configure(this);

parity_err_clr.build();

slv_id = slv_id_reg::type_id::create("slv_id");

slv_id.configure(this);

slv_id.build();

slv_len = slv_len_reg::type_id::create("slv_len");

slv_len.configure(this);

slv_len.build();

slv0_free_slot = slv0_free_slot_reg::type_id::create("slv0_free_slot");

slv0_free_slot.configure(this);

slv0_free_slot.build();

slv1_free_slot = slv1_free_slot_reg::type_id::create("slv1_free_slot");

slv1_free_slot.configure(this);

slv1_free_slot.build();

slv2_free_slot = slv2_free_slot_reg::type_id::create("slv2_free_slot");

slv2_free_slot.configure(this);

slv2_free_slot.build();

slv3_free_slot = slv3_free_slot_reg::type_id::create("slv3_free_slot");

slv3_free_slot.configure(this);

slv3_free_slot.build();

slv0_parity_err = slv0_parity_err_reg::type_id::create("slv0_parity_err");

slv0_parity_err.configure(this);

slv0_parity_err.build();

slv1_parity_err = slv1_parity_err_reg::type_id::create("slv1_parity_err");

slv1_parity_err.configure(this);

slv1_parity_err.build();

slv2_parity_err = slv2_parity_err_reg::type_id::create("slv2_parity_err");

slv2_parity_err.configure(this);

slv2_parity_err.build();

slv3_parity_err = slv3_parity_err_reg::type_id::create("slv3_parity_err");

slv3_parity_err.configure(this);

slv3_parity_err.build();

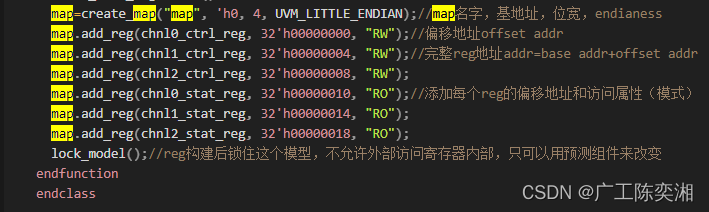

//map的例化,名字-基地址-总线宽度,单位是byte,32位对应4byte-大小端不知道是什么意思

map = create_map("map", 'h0, 4, UVM_LITTLE_ENDIAN);

//将寄存器添加到map:寄存器-偏移地址-访问模式(只读/读写)

map.add_reg(slv_en, 32'h00, "RW");

map.add_reg(parity_err_clr, 32'h04, "RW");

map.add_reg(slv_id, 32'h08, "RW");

map.add_reg(slv_len, 32'h0C, "RW");

map.add_reg(slv0_free_slot, 32'h80, "RO");

map.add_reg(slv1_free_slot, 32'h84, "RO");

map.add_reg(slv2_free_slot, 32'h88, "RO");

map.add_reg(slv3_free_slot, 32'h8C, "RO");

map.add_reg(slv0_parity_err, 32'h90, "RO");

map.add_reg(slv1_parity_err, 32'h94, "RO");

map.add_reg(slv2_parity_err, 32'h98, "RO");

map.add_reg(slv3_parity_err, 32'h9C, "RO");

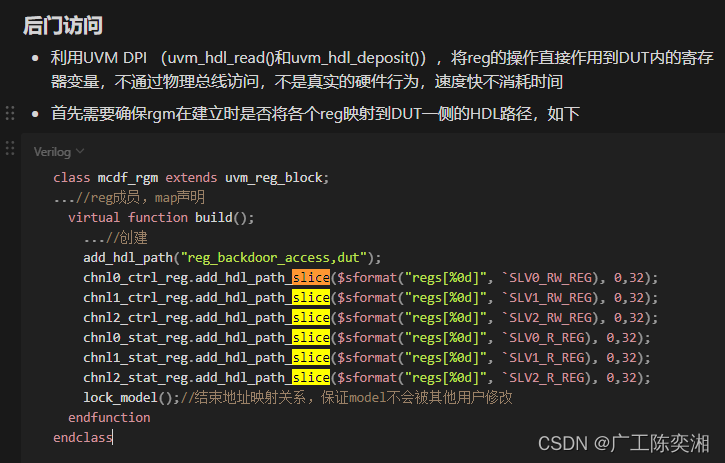

//后门访问:reg.add_hdl_path_slice(“name”,首位,末位)

slv_en.add_hdl_path_slice("???", 0, 32);

parity_err_clr.add_hdl_path_slice("???", 0, 32);

slv_id.add_hdl_path_slice("???", 0, 32);

slv_len.add_hdl_path_slice("???", 0, 32);

slv0_free_slot.add_hdl_path_slice("???", 0, 32);

slv1_free_slot.add_hdl_path_slice("???", 0, 32);

slv2_free_slot.add_hdl_path_slice("???", 0, 32);

slv3_free_slot.add_hdl_path_slice("???", 0, 32);

slv0_parity_err.add_hdl_path_slice("???", 0, 32);

slv1_parity_err.add_hdl_path_slice("???", 0, 32);

slv2_parity_err.add_hdl_path_slice("???", 0, 32);

slv3_parity_err.add_hdl_path_slice("???", 0, 32);

add_hdl_path("???");//为什么不是具体的名称,见图

lock_model();//结束地址映射关系,保证model不会被其他用户修改

endfunction

//定义函数获取域的长度,暂时不知道会在哪里调用到

function int get_reg_field_length(int ch);

int fd;

case(ch)//根据channel id将slv_len的4个域调用get()获得

0: fd = slv_len.slv0_len.get();

1: fd = slv_len.slv1_len.get();

2: fd = slv_len.slv2_len.get();

3: fd = slv_len.slv3_len.get();

default: `uvm_error("TYPERR", $sformatf("channel number should not be %0d", ch))

endcase

return fd;

endfunction

function int get_reg_field_id(int ch);

int fd;

case(ch)

0: fd = slv_id.slv0_id.get();

1: fd = slv_id.slv1_id.get();

2: fd = slv_id.slv2_id.get();

3: fd = slv_id.slv3_id.get();

default: `uvm_error("TYPERR", $sformatf("channel number should not be %0d", ch))

endcase

return fd;

endfunction

endclassapb_pkg

.sv与.svh以及`ifndef `else `endif - 知乎

SystemVerilog与Verilog中重定义问题解决方案 - 知乎

7-字符串与$sformatf,$sformat,$psprintf - _见贤_思齐 - 博客园

//——————————————————————————apb_pkg————————————————————————————

//这两句话表示:如果没有定义过就定义,定义过了就不会执行

//由于多个文件都会调用到相同的文件,这样做避免头文件的重复编译

`ifndef APB_PKG_SV

`define APB_PKG_SV

package apb_pkg;

import uvm_pkg::*;//uvm的两句话

`include "uvm_macros.svh"

//定义了一个参数

parameter bit[31:0] DEFAULT_READ_VALUE = 32'hFFFF_FFFF;

`include "apb.svh"//uvm_pkg的内容写在其他文件中

endpackage : apb_pkg

`endif

//—————————————————————————apb.svh———————————————————————————

//那么就来看看apb.svh这个头文件有什么

//APB为一主多从结构,主端为AHB总线等发送数据过来,从端为给MCDF的信号

//所以分为master和slave两部分,分别搭建验证环境

`ifndef APB_SVH//同理

`define APB_SVH

`include "apb_transfer.sv"

`include "apb_config.sv"

`include "apb_master_driver.svh"

`include "apb_master_monitor.svh"

`include "apb_master_sequencer.svh"

`include "apb_master_agent.svh"

`include "apb_slave_driver.svh"

`include "apb_slave_monitor.svh"

`include "apb_slave_sequencer.svh"

`include "apb_slave_agent.svh"

`include "apb_master_driver.sv"

`include "apb_master_monitor.sv"

`include "apb_master_sequencer.sv"

`include "apb_master_agent.sv"

`include "apb_master_seq_lib.sv"

`include "apb_slave_driver.sv"

`include "apb_slave_monitor.sv"

`include "apb_slave_sequencer.sv"

`include "apb_slave_agent.sv"

`include "apb_slave_seq_lib.sv"

`endif

//——————————————————————apb_transfer——————————————————————————————

//按顺序,看apb_transfer,分为头文件和sv

`ifndef APB_TRANSFER_SV

`define APB_TRANSFER_SV

//枚举变量,APB工作的类型:idle还是读写

//APB传输状态,没问题or出错了

typedef enum {IDLE, WRITE, READ } apb_trans_kind;

typedef enum {OK, ERROR} apb_trans_status;

//apb_pkg本身就是个完整的验证结构,transfer就是apb传输的item

//item只有地址+数据+两个状态+间隔,没有ready信号这些具体的?

class apb_transfer extends uvm_sequence_item;

rand bit [31:0] addr;

rand bit [31:0] data;