在IC设计中,很多时候我们需要产生单周期脉冲来作为启动信号。

单脉冲产生很简单:

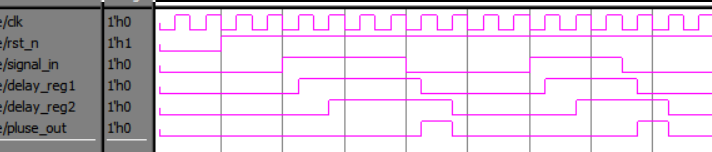

1、 输入信号signal_in延迟1个周期得到delay_reg1;

2、 输入信号signal_in延迟2个周期得到delay_reg2;

3、 delay_reg1取反然后与 delay_reg2相与产生单周期脉冲pluse_out。

NOTE:此种情况下,只要signal_in有脉冲就会产生单脉冲pluse_out。

重点

assign pluse_out= (!delay_reg1)&delay_reg2;

Verilog代码

module single_pluse ( clk,rst_n, signal_in, pluse_out);

input clk ;

input rst_n ;

input signal_in ;

output pluse_out ;

reg delay_reg1;

reg delay_reg2;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

delay_reg1 <= 0;

delay_reg2 <= 0;

end

else

begin

delay_reg1 <= signal_in ;

delay_reg2 <= delay_reg1 ;

end

assign pluse_out= (!delay_reg1)&delay_reg2;

最后

以上就是想人陪魔镜最近收集整理的关于单脉冲的产生的全部内容,更多相关单脉冲内容请搜索靠谱客的其他文章。

发表评论 取消回复