之前学Verilog都是从计组的课程设计胡乱自学,纯属散装Verilog,也没有接触过状态机的概念

先看了下 夏宇闻《Verilog数字系统设计教程》中第12、13章与状态机相关的内容总结了下:夏宇闻《Verilog数字系统设计教程》第12章 同步状态机的原理、结构和设计 和 夏宇闻《Verilog数字系统设计教程》第13章 设计可综合的状态机的指导原则,但感觉没有讲很全

再看了些网上的一些教程博客和案例,主要参考 Verilog 状态机 和 状态机的Verilog写法 两篇博客,个人总结出写状态机的一般格式

3 段式(推荐)

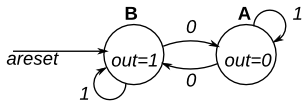

以HDLBits中Simple FSM1 (asynchronous reset) 为例

(0)根据状态机的个数确定状态机编码。利用编码给状态寄存器赋值,代码可读性更好。Verilog数字系统教程书中对基于FPGA的状态机,推荐使用独热编码。

(1)状态机第一段,时序逻辑,非阻塞赋值,传递寄存器的状态。

// This is a sequential always block

always @(posedge clk, posedge areset) begin

// State flip-flops with asynchronous reset

if(areset) begin

state <= B;

end

else begin

state <= next_state;

end

end

(2)状态机第二段,组合逻辑,阻塞赋值,根据当前状态和当前输入,确定下一个状态机的状态。

// This is a combinational always block

always @(*) begin

// State transition logic

case(state)

A: begin

if(in == 1'b1) begin

next_state = A;

end

else begin

next_state = B;

end

end

B: begin

if(in == 1'b1) begin

next_state = B;

end

else begin

next_state = A;

end

end

endcase

end

(3)状态机第三段,时序逻辑,非阻塞赋值,如果是 Mealy 型状态机,根据当前状态和当前输入,确定输出信号;如果是 Moore 型状态机,根据当前状态确定输出信号。

输出的这一段,看各博客教程一般都是 时序逻辑、对当前状态、非阻塞赋值,但也有部分博客是对下一状态判断。

对于该题,提示使用 (1)assign out = (state == …); 组合逻辑,方便且正确;

(2)换成电平敏感的 always 块对当前状态 state 阻塞赋值,判断也正确;

(3)换成边沿敏感的 always 块(时序逻辑)对下一状态 next_state 非阻塞赋值,判断也正确。

// Output logic

// -----------------------------------------

// (1) 用 assign 连续赋值 组合逻辑的写法

assign out = (state == B);

// -----------------------------------------

// (2)用电平敏感的 always 块 组合逻辑的写法,判断的是当前state

always @(*) begin

if(areset) begin

out = 1'b1;

end

else begin

if(state == B) begin

out = 1'b1;

end

else begin

out = 1'b0;

end

end

end

// -----------------------------------------

// (3)时序逻辑的写法,注意判断的是next_state,用当前state会比答案结果慢一周期

always @(posedge clk, posedge areset) begin

if(areset) begin

out <= 1'b1;

end

else begin

if(next_state == B) begin

out <= 1'b1;

end

else begin

out <= 1'b0;

end

end

end

Moore 型输出信号与 Mealy 型 3 段式状态机相比延迟了一个时钟周期,这是因为进入到新增加的编码状态机时需要一个时钟周期的时延。此时,输出再用非阻塞赋值就会导致最终的输出信号延迟一个时钟周期。这也属于 Moore 型状态机的特点。

输出信号赋值时,用阻塞赋值,则可以提前一个时钟周期。 但在该题的第(3)种写法中,对当前状态 state 使用阻塞赋值和使用非阻塞赋值的结果一样,都比答案慢一周期,不理解是不是背后eda的原因?

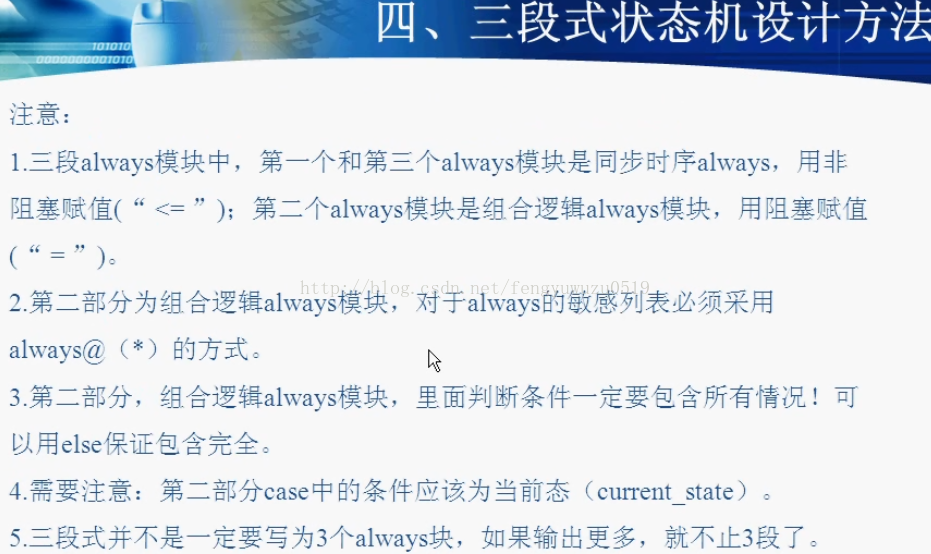

参考Verilog状态机用法精讲案例总结状态机三段式的规范写法注意事项

2段式

(待补充)

最后

以上就是无私发带最近收集整理的关于Verilog状态机3 段式(推荐)2段式的全部内容,更多相关Verilog状态机3内容请搜索靠谱客的其他文章。

发表评论 取消回复