AD936x 系列快速入口

MGC、Slow AGC、Fast AGC补充: AD9361 补充(上)

文章目录

- 一、 MGC 详细配置

- 1.1 Gain Table Config

- 1.2 ADC Overload 、LMT Overload 和 Analog Settling Time

- 1.3 RSSI

- 二、 AGC Slow Attack / hybrid 详细配置

- 2.1 AGC Attack Delay

- 2.2 gain table

- 2.3 Thresholds and steps

- 2.4 Overload

- 2.5 Slow AGC 和 hybrid AGC

- 三、 AGC Fast Attack 详细配置

- 3.1 digital gain

- 3.2 步长 和 State Wait Time

- 3.3 STATE 2 和 STATE 3 主要配置

- 3.4 增益解锁

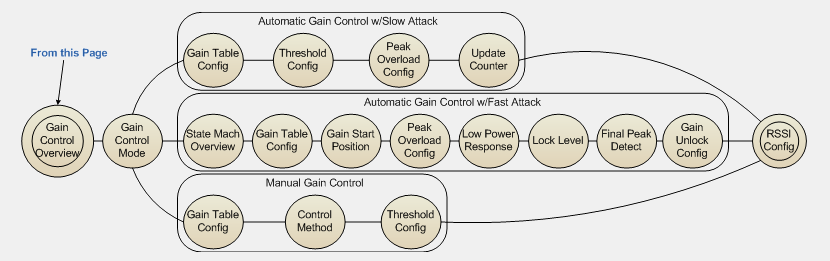

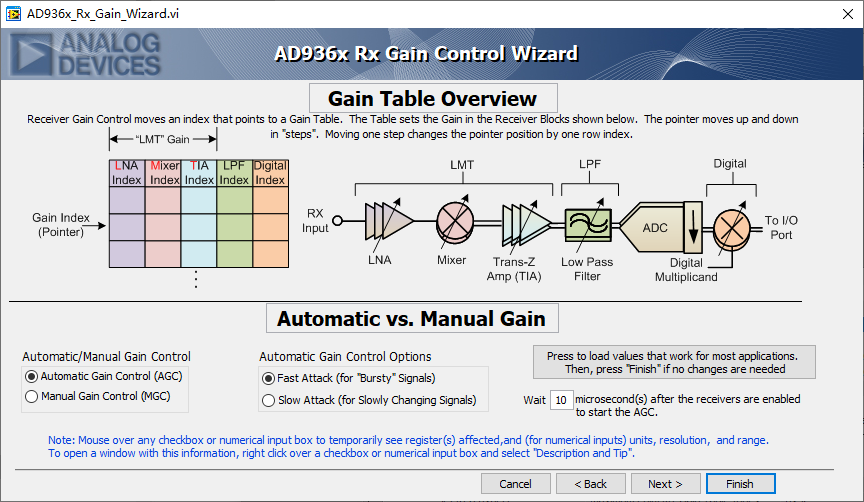

上图为AGC Fast Attack 、 AGC Slow Attack 和 MGC配置步骤框图,下面分别讲解。

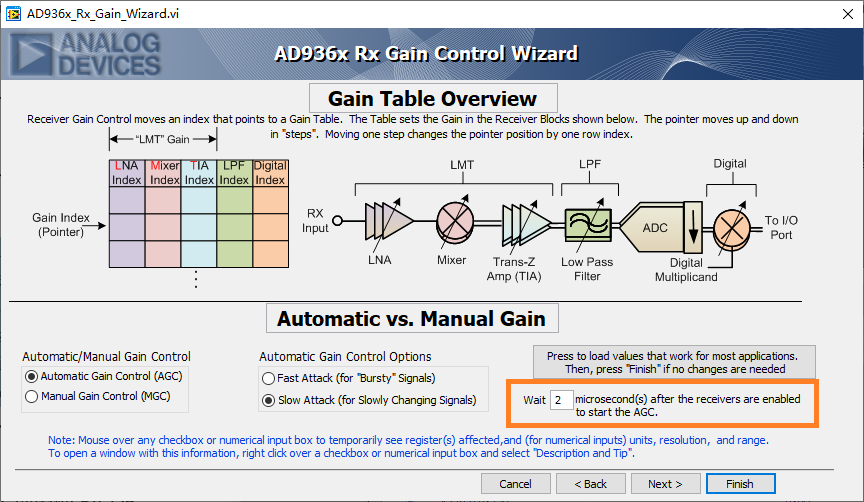

一、 MGC 详细配置

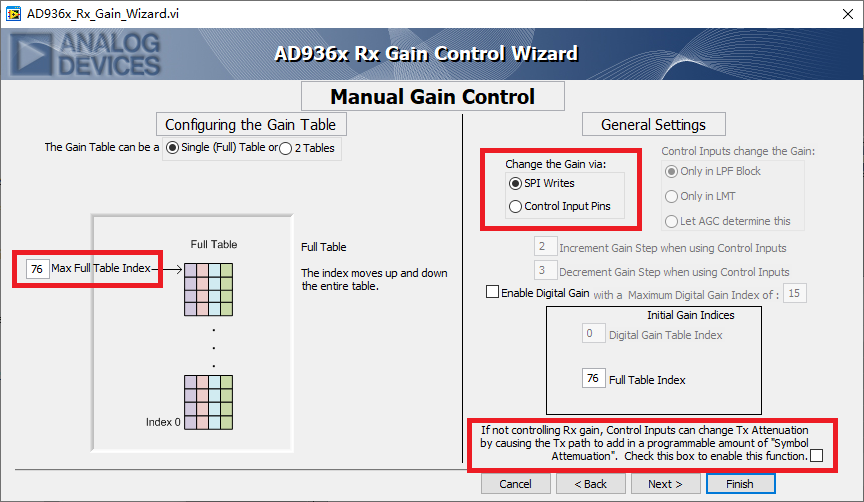

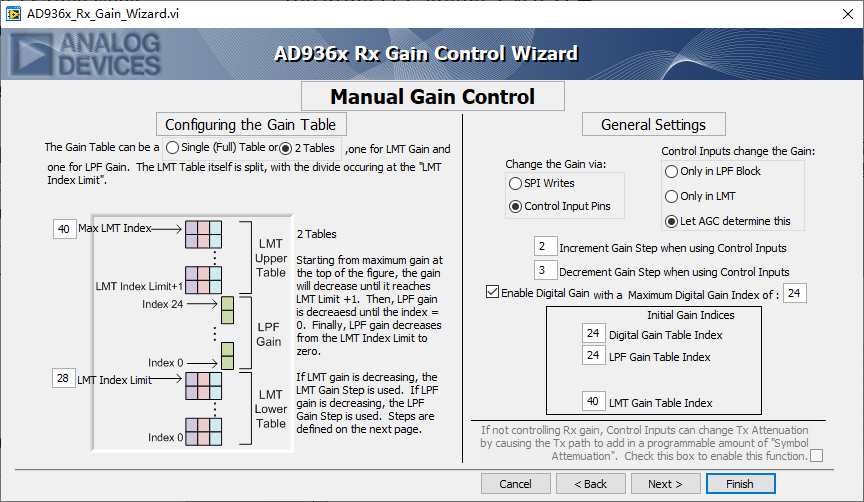

1.1 Gain Table Config

MGC 的 Change the Gain via、Control Inputs change the Gain 、LMT Index Limit详细介绍在 AD9361 补充(上)第一部分

Gain Table、Enable Digital gain 、Max LMT Index、Maximum Digital Gain Index、MAX Full Table Index详细介绍在在AD9361 介绍 (中) 6.1节

Gain Table : Full Table 和 Split Table

MAX Full Table Index : 仅含模拟增益的标准全增益表的最大索引为76(d)

Change the Gain via : BBP可以通过SPI write和 control input pins控制增益改变

Enable Digital gain :可以仅使用模拟增益,不使用数字增益。

Maximum Digital Gain Index :最大数字索引为31(d)

Initial Gain Indices : 在初始化时增益索引先配置为最大。

上图右下角红色方框 :MGC模式手动控制TX Symbol 增益, 当寄存器0x0FB[D1:D0]位都是1,CTRL_IN信号控制增益,当CTRL_IN信号变为高电平时,增益索引增加或减少。 默认状态,不勾选

Max LMT Index : Split Table 模式时, LMT表最大索引为40(d)

Control Inputs change the Gain : 在Split Table模式,使用control input pins控制增益时 才可选

LMT Index Limit : LMT表分为两个部分,一个上部LMT表和一个下部LMT表,分割线是初始LMT gain limit

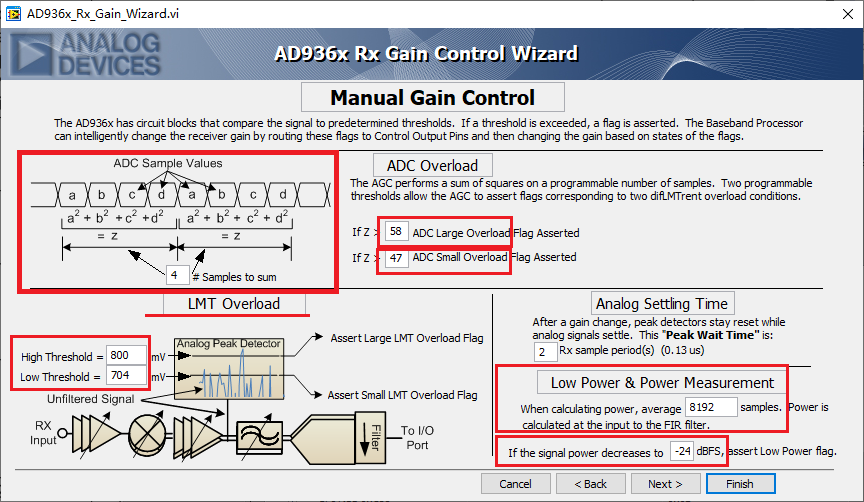

1.2 ADC Overload 、LMT Overload 和 Analog Settling Time

ADC Overload 、LMT Overload、 peak wait time、average signal power、LOW power threshold详细介绍在在AD9361 介绍 (中) 6.3节

Samples to sum : 4 个样本,范围 1 到 8 个

ADC Large Overload threshold :58

ADC Small Overload threshold :47

LMT High threshold : 800,范围 16 到 800mv ,分辨率:16mv/LSB

LMT Low threshold : 704,范围 16 到 800mv ,分辨率:16mv/LSB

peak wait time : 2 ,范围 1 到 31

average signal power :8192 个样本

LOW power threshold : -24 dBFS, 范围为0 dBFS至-63.5 dBFS

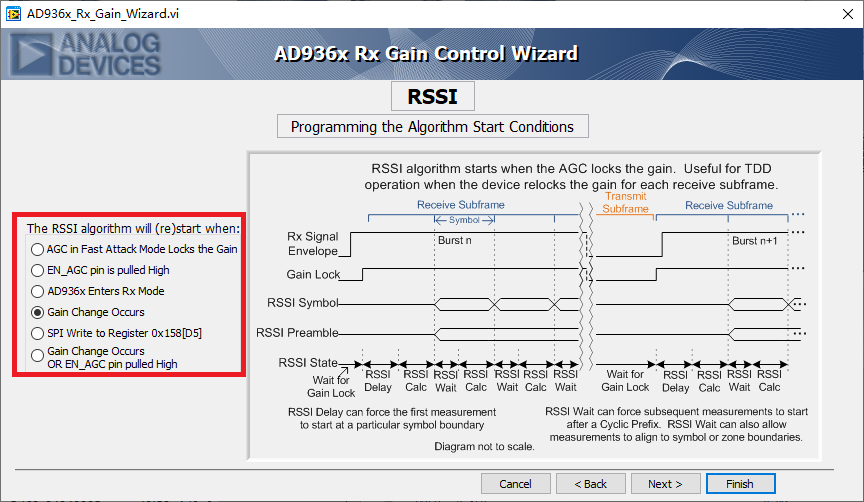

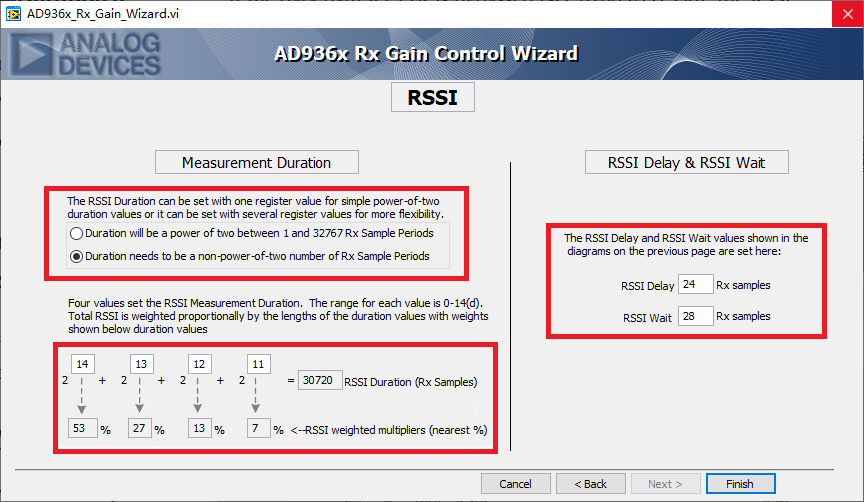

1.3 RSSI

RSSI详见 AD9361 补充(中)第五部分,对下述配置都有讲解。

RSSI algorithm start mode :3,Gain change occurs

Measurement Duration : Default RSSI Meas Mode位为零,持续时间由四部分持续时间组成, 各部分如上图所示。

RSSI Delay :时钟频率为接收采样速率8分频, 范围0到2040个 Rx samples,暂时配置如上图所示,依情况修改。

RSSI Wait : 时钟频率为接收采样速率4分频, 范围0到1020个 Rx samples,暂时配置如上图所示,依情况修改。

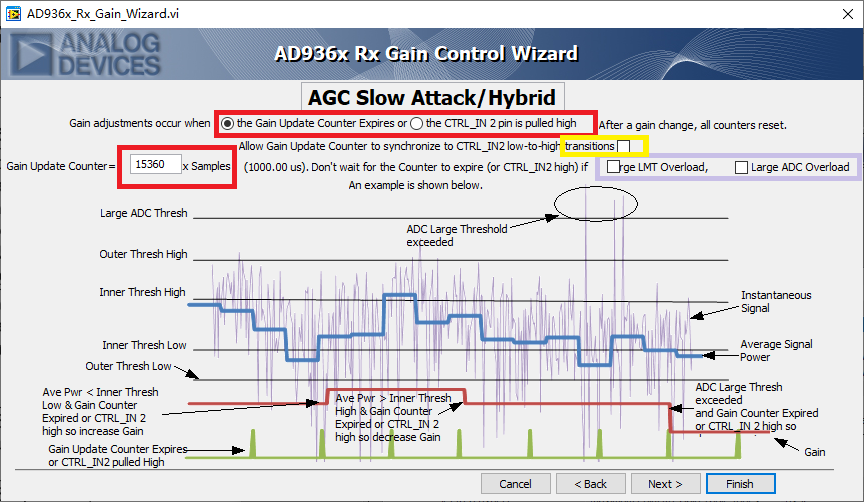

二、 AGC Slow Attack / hybrid 详细配置

AGC Slow Attack / hybrid 的 详细介绍在 AD9361 补充(上)第二和第三部分

2.1 AGC Attack Delay

右下角:AGC Attack Delay ,AGC等待AGC attack寄存器所设置的时间(微秒),该延时使接收路径在AGC启动之前稳定。 ENSM 进入Rx 状态,开始计时。分辨率:1 µs/LSB,范围:0到31微秒。可使用下方公式配置。

AGC Attack Delay (us)=ceiling((((0.2+Delay_LNA) * ClkRF+14))/(2*ClkRF))+1

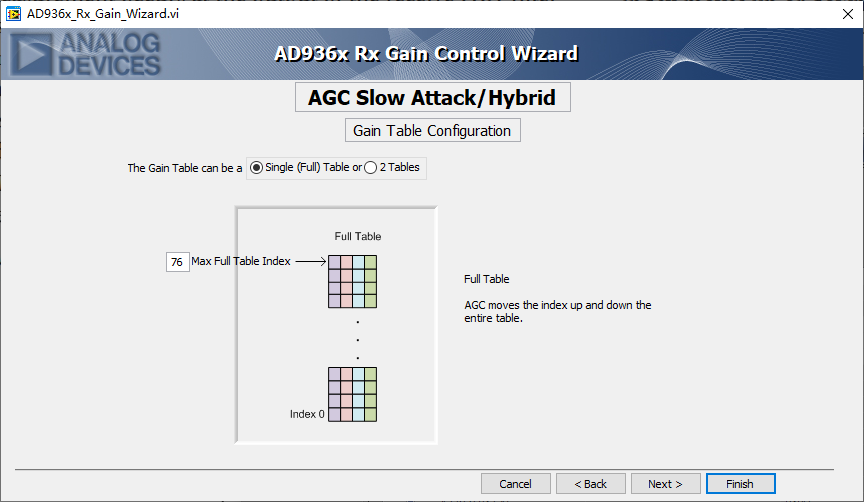

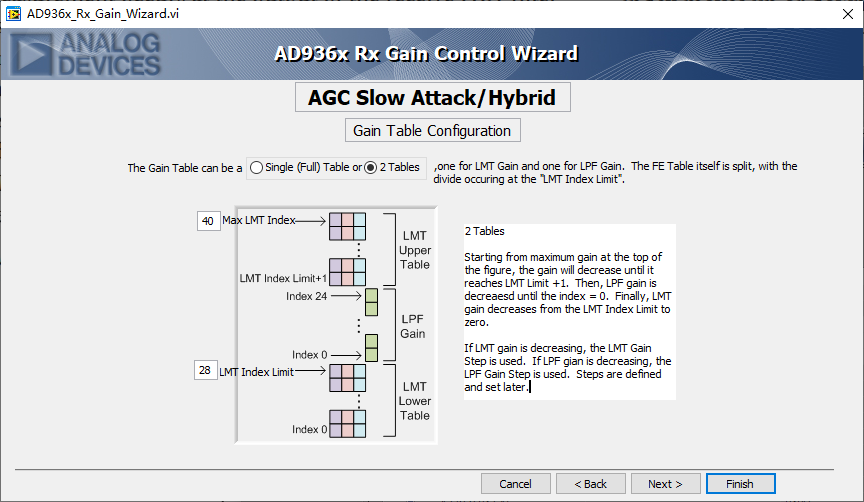

2.2 gain table

增益表和MGC配置类似,我们选取Full table 模式

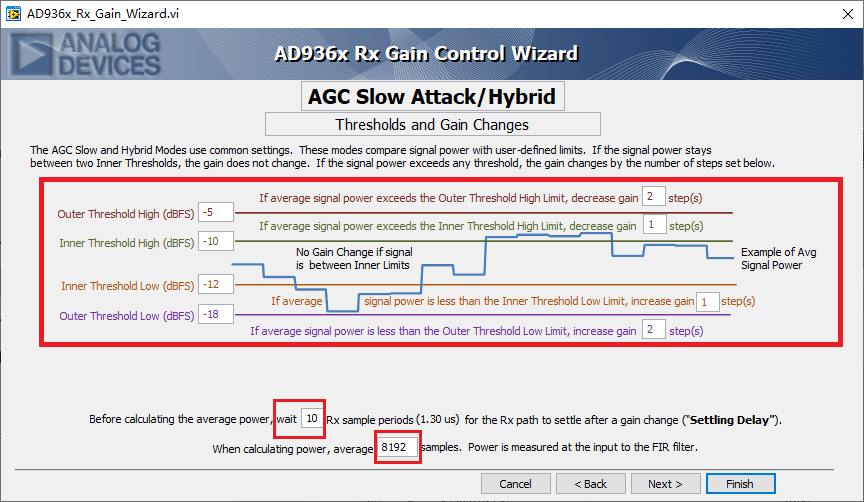

2.3 Thresholds and steps

阈值和步长 : 先按默认配置

Settling Delay:详见 AD9361 介绍 (中) 6.37,延时等于寄存器值(Dec Power Measurement Duration[3:0],最大31)乘以2,最大62,其以ClkRF速率(Rx FIR滤波器时钟速率的输入)计时。 软件中其范围:0到 62 /(RFIR 抽取因子),因为软件中以 Rx sample 计。上图中抽取因子为2,10个 Rx sample , 即20个ClkRF。

Power : 功率测量期间抽取一定数量的样本,测量持续时间以 Rx sample periods 计 ,范围:0到16*32768=524288个

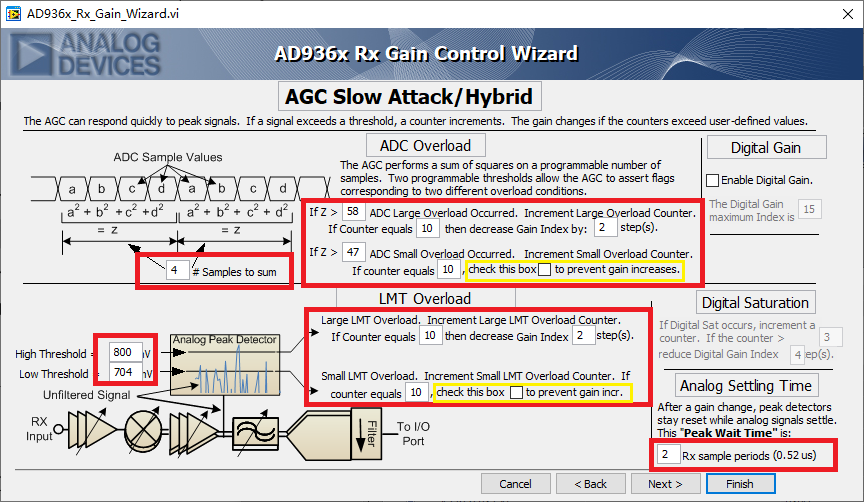

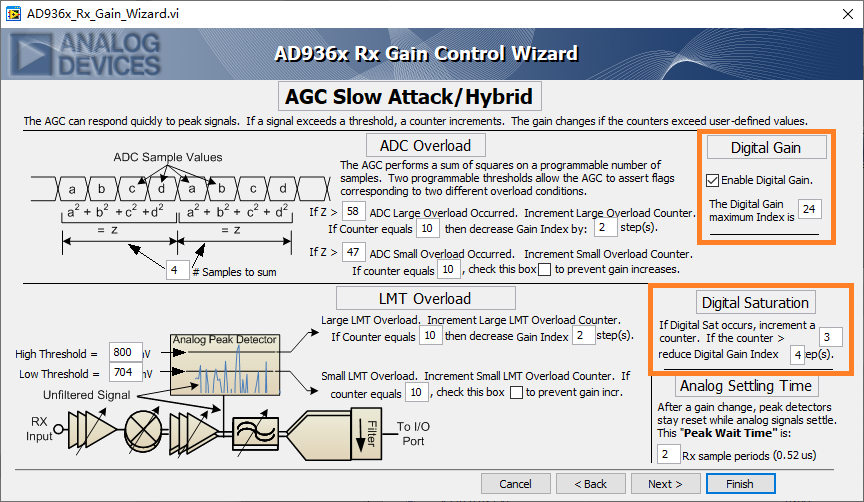

2.4 Overload

Overload 详见 AD9361 补充(上)2.2

部分配置与MGC中一样,特定过载事件(ADC 和 LMT overload )超过10 次就调整增益索引,步长配置如上图所示。

黄色框 Prevent Gain Inc : 如果发生small LMT或 small ADC 过载,勾选可防止增益增加。

Digital Gain :,可以不使用 Digital Gain,也可以使用。使用时Digital Saturation 也启用,如果digital saturation发生的次数超出计数器配置的3次,增益索引降低,步长为4。

2.5 Slow AGC 和 hybrid AGC

Gain adjustments : 增益更新计数器到期 或 hybrid模式下BBP将CTRL_IN2信号拉高,我们选 Slow AGC 模式增益计数器到期。

黄色框 :勾选后,Digital Sat Counter的Enable Sync位置1,CTRL_IN2拉为高电平可以复位增益更新计数器

Gain Update Counter : 增益更新计数器配置为1000 微秒。

紫色框 :勾选后,large LMT过载和/或 large ADC过载使增益立即变化,忽略增益更新计数器

后续 RSSI配置和MGC一样

三、 AGC Fast Attack 详细配置

Fast AGC 的 详细介绍在 AD9361 补充(上)第四部分

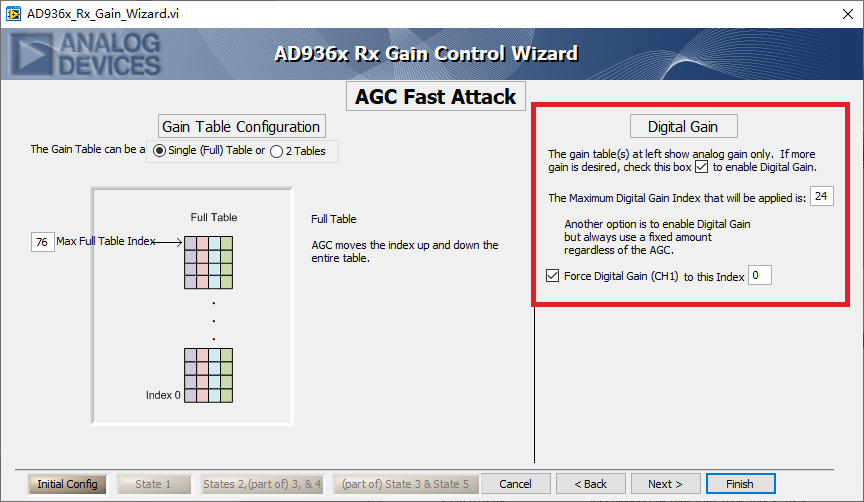

3.1 digital gain

full table 和 split table : 和 slow AGC 配置一样

digital gain : 可以使用,也可以不使用, 使用时可以勾选 Force Digital Gain 来迫使数字增益一直保持某一个值。 本次不使用 digital gain。

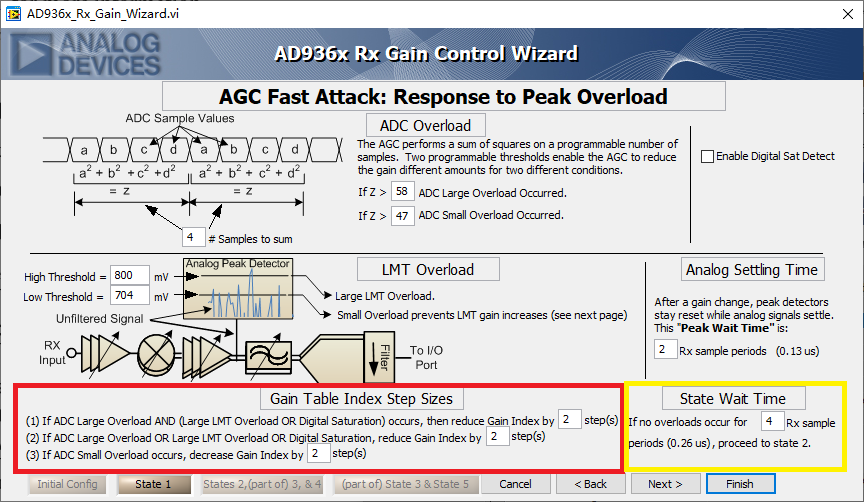

3.2 步长 和 State Wait Time

红色框 :

- 全表模式下的 large ADC和(Large LMT或 digital sat)过载,步长配置为2

- 全表模式下的 large ADC或Large LMT或 digital sat 过载,步长配置为2

- small ADC 过载,步长配置为2

State Wait Time : Energy Detect Count 配置为260 ns ,4个 Rx samples, 如果该时段没有检测到峰值过载,fast AGC可以进入状态2。Energy Detect Count 以ClkRF时钟频率(Rx FIR滤波器输入端使用的时钟)计时。

其他配置 参考之前内容

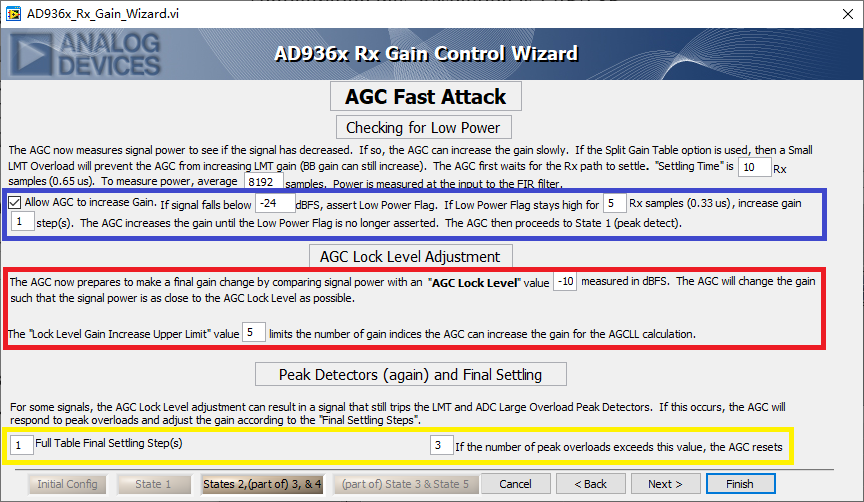

3.3 STATE 2 和 STATE 3 主要配置

Settling time 和 平均功率样本数量配置与之前一样

蓝色框 : 当Enable Incr Gain 位置1时,如果平均信号功率低于低功率阈值的时间大于增量时间,进入State 2A, AGC 增加增益,使用的增益步长为寄存器Increment Gain Step + 1。 低功率阈值配置为24,增量时间 5 Rx samples ,步长 为1。 后续我们不使用Enable Incr Gain 位,不勾选。

红色框 : 将测得的信号功率与 AGC Lock Level锁定电平进行比较。AGC调整增益,使平均信号功率与AGC锁定电平相匹配。如果增益需要增加来达到锁定电平,有一个最大增加量,由AGCLL Max Increase设置。 AGC Lock Level配置为10,最大增加量 设为5。

黄色框 : 在全增益表模式下,无论过载类型如何,步长(减少的索引数)始终是Post Lock Level Step Size for Full Table值。AGC 对锁定电平后出现的过载情况进行计数。如果该数超过Final Overrange Count,AGC将返回 State 1 。 步长 配置为1 ,过载数配置为3。

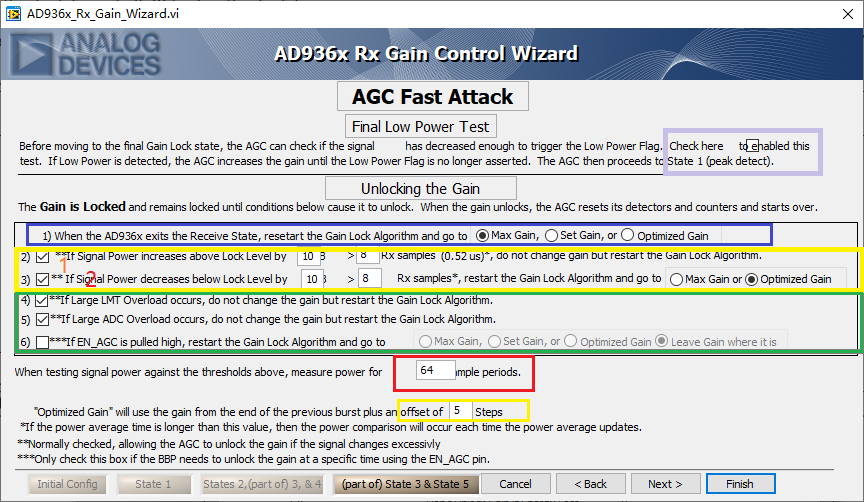

3.4 增益解锁

紫色框 :STATE 3下,如果Enable Gain Inc After Gain Lock和Enable Incr Gain 位为1,AGC 将检查是否出现低功率情况,执行低功率测试。 勾选后 Enable Gain Inc After Gain Lock 位 为1 。本次暂不勾选

蓝色框 :AD9361退出Rx State, AGC将增益重置为Max gain

黄色框 :信号功率与Energy Lost Threshold比较,信号功率值更新时,AGC都会计算增益锁定开始时测量的功率与当前信号功率之间的差值,将差值与Energy Lost Threshold进行比较。如果差值超过阈值的时间等于Gain Lock Exit Count(寄存器 0x119)的两倍,增益解锁。 Stronger Signal Threshold也进行一样的比较。

2号框 : Energy Lost Threshold 配置为10, 时间 配置为8 个 Rx samples

1号框 : Stronger Signal Threshold配置为10, 时间 配置寄存器 与2号框是同 一个。

当 超出 Energy Lost Threshold 阈值,增益解锁选用 optimized gain 方式 , Optimize Gain Offset 配置为 5。

绿色框 : 勾选 ,Large ADC Overload 和 Large LMT Overload 发生 ,配置为 解锁时 增益索引不立即改变,但AGC算法会重新开始。 不勾选时,Don’t Unlock Gain if Lg ADC or LMT Ovrg 位 为1,如果0x0FB[D6]和0x014[D1]位也为1,发生Overload ,也不解锁。

BBP将EN_AGC引脚拉高,增益解锁功能不勾选。

红色框 : 测量信号的平均功率,配置为 64 个 样本。

后续配置和之前一样。

最后

以上就是漂亮黑裤最近收集整理的关于AD936x 配置软件介绍 下一、 MGC 详细配置二、 AGC Slow Attack / hybrid 详细配置三、 AGC Fast Attack 详细配置的全部内容,更多相关AD936x内容请搜索靠谱客的其他文章。

发表评论 取消回复