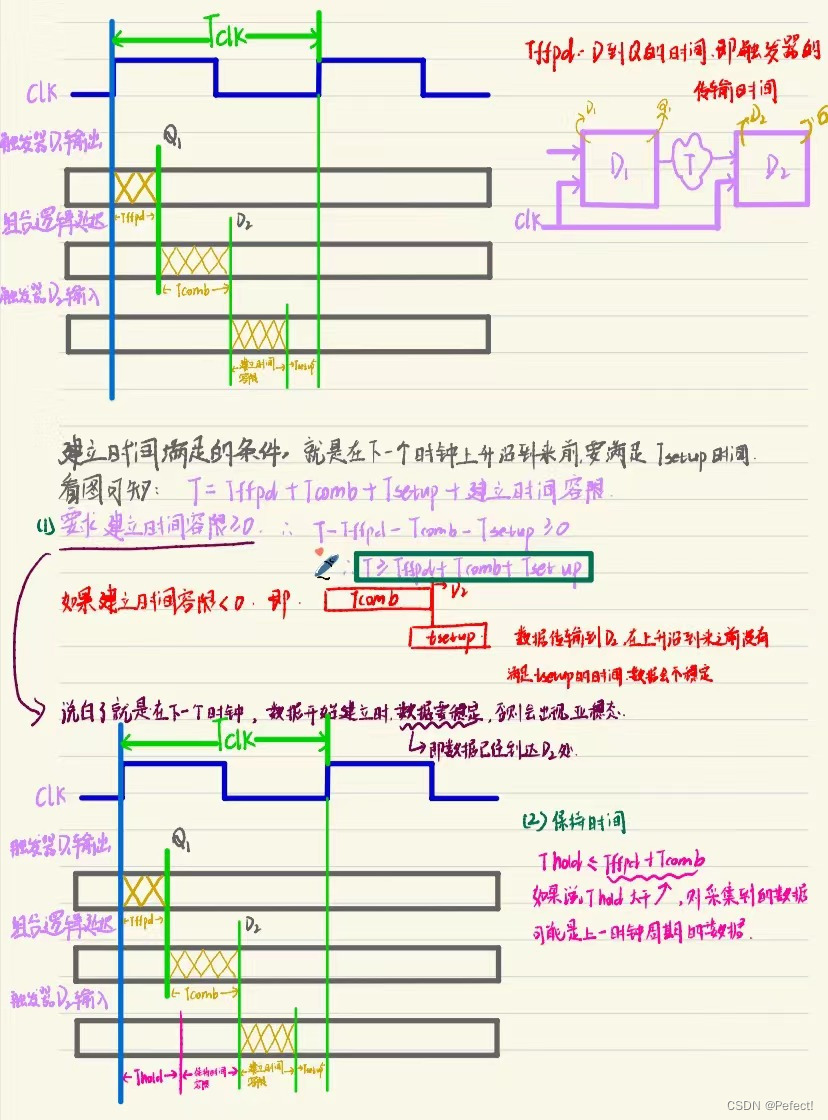

一. 建立时间和保持时间

1.建立时间:触发器在时钟沿到来之前,其数据输入端口的数据需要保持不变的时间,决定了触发器之间的组合逻辑的最大延迟。因为在数据setup时必须保证数据已经稳定,即数据已经通过组合逻辑到达D输入端口。

T >= tff(max) + tcomb(max) + tsetup

2.保持时间:触发器在时钟沿到来之后,其数据输入端口的数据需要保持不变的时间,决定了触发器之间的组合逻辑的最小延迟。不满足要求的话,上一时钟周期的数据会冲掉本周期应该传输的数据。

thold <= tff(min) + tcomb(min)

二. 亚稳态

- 亚稳态产生的原因

(1)在同步(同一时钟域)系统中,如果触发器的setup time / hold time不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。这段之间成为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是究竟是0还是1,这是随机的,与输入没有必然的关系。(根本原因)

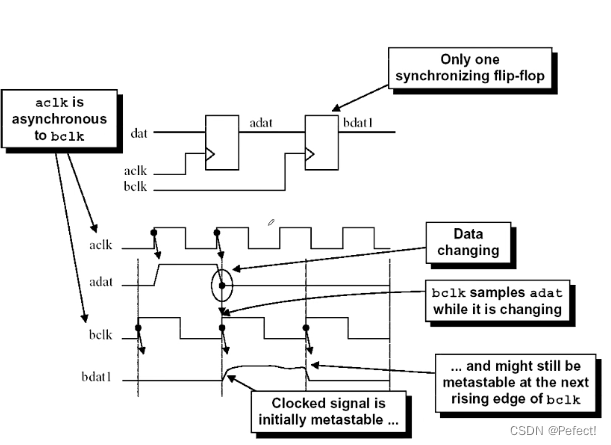

(2)在跨时钟域中,跨时钟域的信号和同步时钟的关系不能确定,也会产生亚稳态。

- 如何减少亚稳态的风险

单一时钟域内的信号:

工具检查每个触发器的建立保持时间,确保其不出现亚稳态。

跨时钟的信号:

· 没有工具可以保证其可靠性

· 静态时序分析其应该设置false path 约束

· 只能靠逻辑设计来保证:同步化技术 - 同步化技术

· 同步器——控制信号

· 保持寄存器和握手——地址或数据总线信号

· 异步FIFO设计——数据总线信号 - 同步器

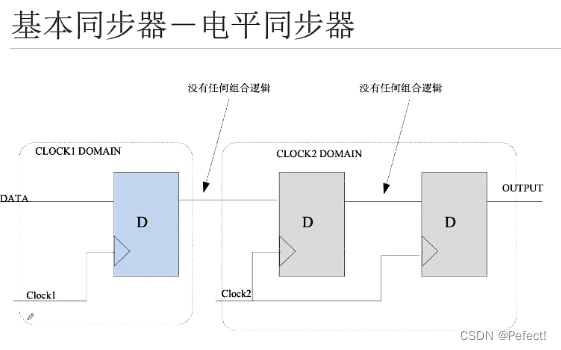

(1) 为什么使用两级寄存器(接受时钟域)

发生亚稳态的概率是一级寄存器概率的平方,两级并不能完全消除亚稳态的危害,但是提高了可靠性,减少其概率的发生。一级概率很大,三级改善不大。同步器延迟1或2个接受时钟。

(2) 同步器的分类

· 电平同步器

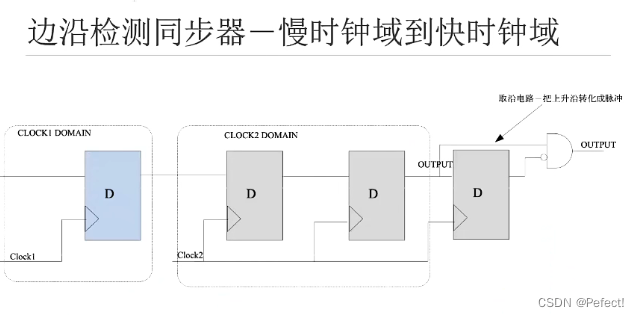

· 边缘检测同步器

· 脉冲同步器

①电平同步器

电平同步器适合两时钟信号的频率相等的情况,如果频率不相等,一个快,一个慢,会发生数据丢失或重复采样的情况。

②边缘检测同步器

慢时钟域到快时钟域会发生重复采样数据的情况

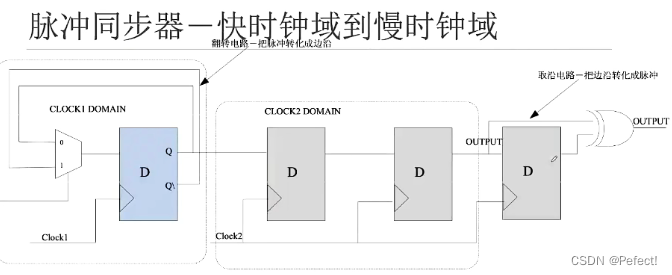

③ 脉冲同步器

快时钟域到慢时钟域会发生数据丢失的情况

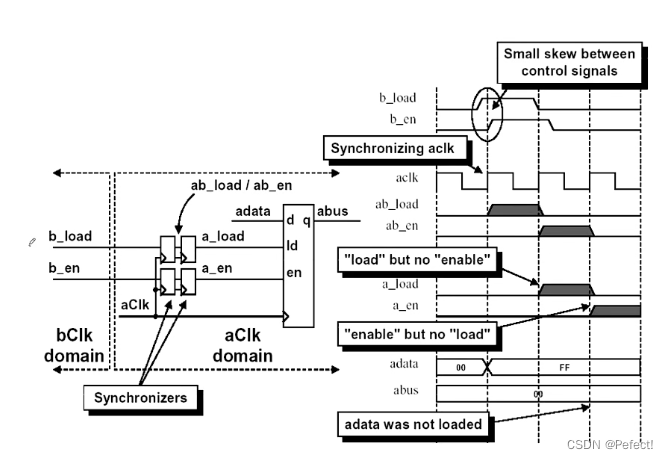

(3)多位控制信号跨时钟域

本身两路控制信号b_load 和 b_en 到达同步器的时间就不一样(因为路径不同延迟不同),经过两级延迟后,出现上图的情况,不能让使能信号同时有效。解决方案是将两路控制信号设计成一个控制信号。

- 总线信号跨时钟域

总线信号跨时钟域就不能像上面一样把几路信号合成一个信号了,因为信号太多了。解决方案:保持寄存器和握手和异步FIFO设计 - 握手(效率不是很好)

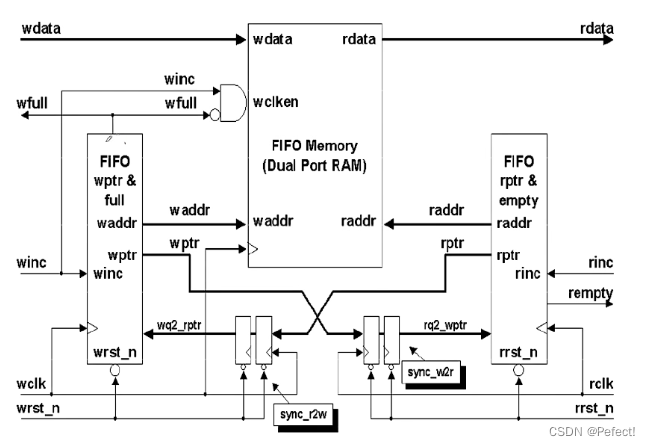

- FIFO(终极方案)

· 同步FIFO:写时钟和读时钟为同一个时钟

· 异步FIFO:写时钟和读时钟为独立的时钟

跨时钟域的数据信号需要用到异步FIFO,隔离时钟域匹配读写速度。(FIFO在两个不同时钟域中间传递数据,当前时钟域快后时钟慢时,FIFO会被写满,当FIFO为满时会给前面一个信号,告诉它不能再写了;当前时钟慢后时钟快时,FIFO会被读空,会给后面一个信号,告诉它不能再读了。)避免了数据重复采样和数据丢失的情况。所以异步FIFO中最重要的部分就是写满和读空标志的产生,通过比较写指针和读指针来实现。

最后

以上就是跳跃秀发最近收集整理的关于跨时钟域问题(建立时间保持时间、亚稳态、同步化技术)一. 建立时间和保持时间二. 亚稳态的全部内容,更多相关跨时钟域问题(建立时间保持时间、亚稳态、同步化技术)一.内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复