阶段二.译码

1.id(组合逻辑电路),结合regs(组合逻辑电路)

主要功能为:1.根据指令内容,分析当前具体是哪一条指令(比如上面的mul);2.根据具体指令,确定当前涉及的寄存器,比如是1个还是2个,是否需要写寄存器,包括写到哪一个上3.访存:访问通用寄存器,并且得到要读的寄存器的内容以及地址。

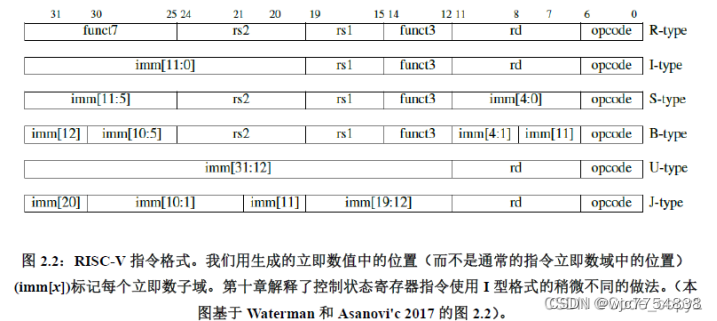

首先我们知道指令为32位。我们可以看下risc-v基础的基本指令,也是我们目前学习risc-v指令的比较重点的地方如下图9.

图9

还有是所有指令这里暂不做介绍,感兴趣可以自己CSDN搜索。

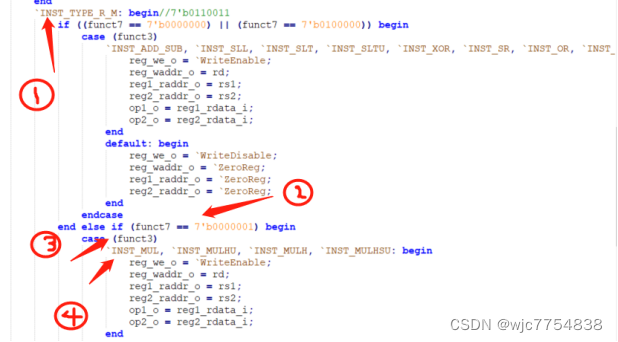

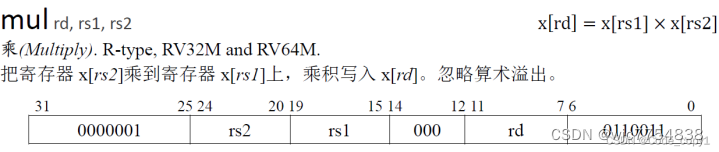

举例:代码中可以看到不同的最终译码指令,比如我们采用了图9中的R指令,比如说mul,在代码中我们可以看到在当opcode为INST_TYPE_R_M(在define.v中可以看到其值为7’b0110011。funct7==7’b0000001,并且funct3有mul。如下图10,11

图10

图11

可以看到,代码做的是:

1.根据opcode和funct7,funct3确定指令为Mul;

2.寄存器写使能;

3.写地址为rd(也就是Inst[11:7])4.寄存器1的地址值为rs1,并且结合regs将地址的内容给予op1_o。寄存器2的地址值为rs2,并且结合regs将地址的内容给予op2_o。其中寄存器1中的指令内容,把寄存器对应的地址中的内容值取出来。(这里再次说明下,op这里是用于计算赋值等,可以认为它就是出现在运算赋值等情况下,代表一个值,无实际意义)

图11也说明算数的方法。说白了:做的工作就是根据Inst中rs1和rs2找到寄存器的地址,并且把地址的内容相乘放到rs1上,然后写到rd中(注意,后面黑体字执行这一部分是在第三阶段执行中完成的,这里只是提前的解释一下方便我们对解码阶段的理解)。

值得说明的是:id和regs这里都是组合逻辑电路,意思也就是说。虽然上述代码是在id.v和regs.v中分别完成,但是他们是同一时间发生也就是说,id在regs的辅助下将值分别完成了上述工作。

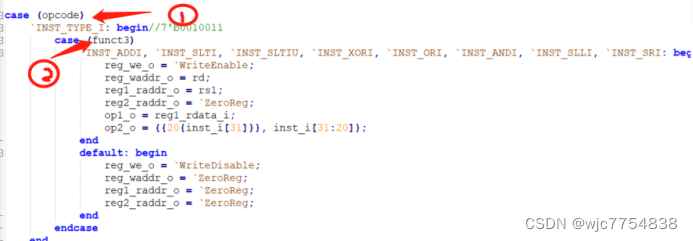

再举一个I指令的例子。ADD

我们看下代码,如下图12

图12

步骤为:

1.根据opcode和funct3确定是add指令;

2.写使能;

3.给出目标寄存器地址,得到rs1,并且根据rs1地址通过regs得到rs1的地址内容给予op1_o。并且根据inst[31:20]我们可以直接的出来op2_o的的内容,进行后续操作。

剩下的其他所有指令不管是加减乘除与或,都是和上述指令的操作类似,可能不同的是出现在R指令或者I指令等等。但是总体来说是换汤不换药。

2.id_ex(时序逻辑电路)

首先是主要功能:

1.根据指令内容,解析出当前具体是哪一条指令(比如add指令);

2.根据具体的指令,确定当前指令涉及的寄存器。比如读寄存器是一个还是两个,是否需要写寄存器以及写哪一个寄存器;

3.访存:访问通用寄存器,得到要读的寄存器的值(地址)。

这里没什么好说的,我仍然是觉得id_ex的主要作用是把对应的信号整合在一起,送到下一个阶段执行。还有的其他作用像是中断控制的是这里(后续再说)

最后

以上就是狂野世界最近收集整理的关于tinyrisc-v学习笔记(三.代码译码)的全部内容,更多相关tinyrisc-v学习笔记(三内容请搜索靠谱客的其他文章。

发表评论 取消回复