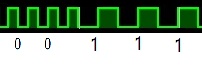

FSK是数字通信中的一种调制方式。具有较强的抗干扰能力。常用的bfsk其原理比较简单,不同的频率代表不同的信息,比如10khz表示0,20khz表示1,如下图:

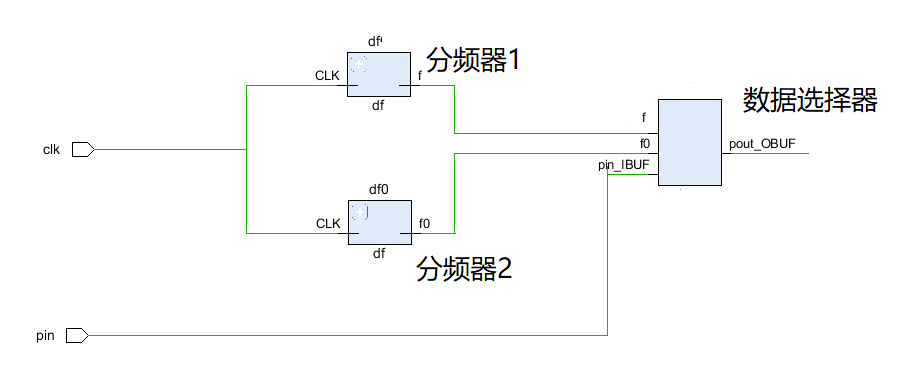

采用fpga实现功能的画,需要下面几个部分,分频器,与数据选择器

电路图如下:

对应的veril代码如下

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/01/14 06:42:19

// Design Name:

// Module Name: fskd

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module df(clk,k,f);//分频器

input clk;

input [31:0]k;

output reg f=0;

reg [31:0]cnt=0;

always@(posedge clk)//alway下只能用reg

begin

cnt=cnt+1;

if(cnt==k)

cnt=0;

if(cnt==0)

f<=~f;

end

endmodule

module ds(f0,f1,pin,pout);//选择器

input wire f0;

input wire f1;

input wire pin;

output wire pout;

assign pout=(pin==0)?f0:f1;

endmodule

module fskd(clk,pin,pout);

input clk;

input pin;

output pout;

wire pout;

wire f0;

wire f1;

parameter k0=50000;

parameter k1=25000;

df df0(clk,k0,f0);

df df1(clk,k1,f1);

ds ds01(f0,f1,pin,pout);

endmodule

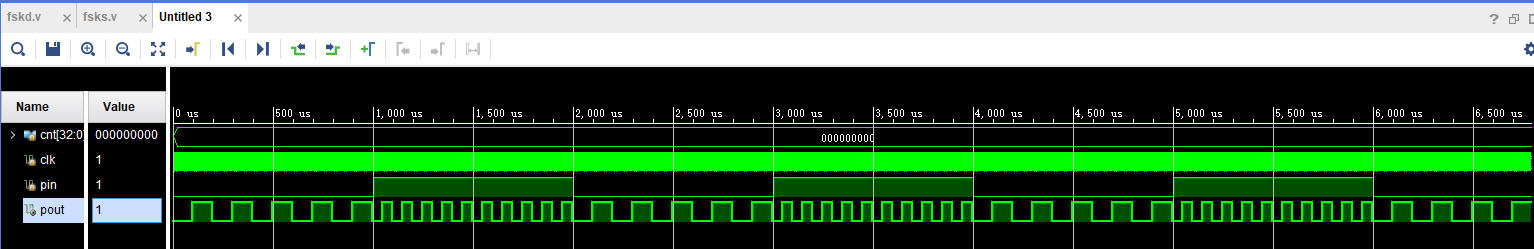

仿真代码如下,未调信号用的方波

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/01/14 07:03:49

// Design Name:

// Module Name: fsks

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

//module fskd(clk,pin,pout);

//module df(clk,k,f);//分频器

//module ds(f0,f1,pin,pout);//选择器

module fsks();

reg[32:0]cnt=0;

reg clk=0;

reg pin=0;

wire pout;

fskd fskd0(.clk(clk),.pin(pin),.pout(pout));

initial

forever

begin

repeat(1000000)

begin

#1 clk<=~clk;

end

pin=~pin;

end

endmodule

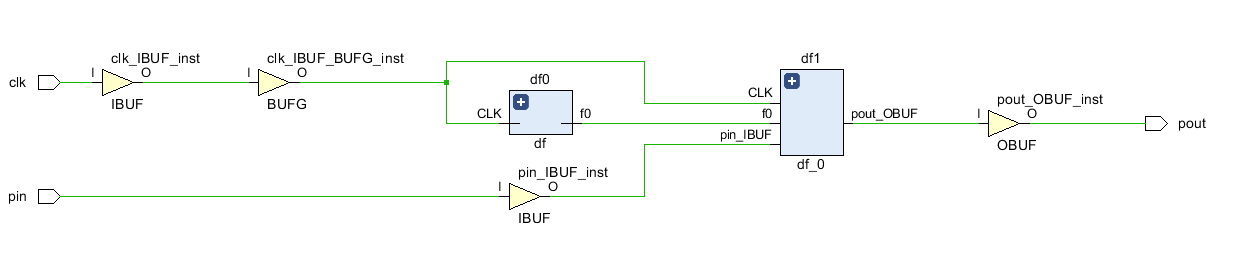

得到的电路图和仿真波形如

有一个分频器和数据选择器放到了一起

最后

以上就是强健草丛最近收集整理的关于bfsk的fpga实现的全部内容,更多相关bfsk内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。