参考高级设计:http://www.eefocus.com/coyoo/blog/13-12/301064_679a3.html

异步复位同步化(同步化的异步复位)

为了避免纯粹的同步复位和纯粹异步复位的问题,可以使用一种叫做同步化的异步复位,我们称其为第三类复位。这种复位完全结合了异步复位和同步复位的优势,我们知道异步复位的优势是不参与数据路径,所以不影响数据路径速度,而复位几乎是瞬间起作用;而同步复位的优势是百分百地同步时序分析且具有抗噪声性能。这种复位其实就是通常我们所说的异步复位同步释放。就如同我之前讨论的那样,异步地进入复位是最好的,只是异步地退出复位会导致一些类似亚稳态和由同步电路参与反馈而引起不想要的状态之类的危害等问题。

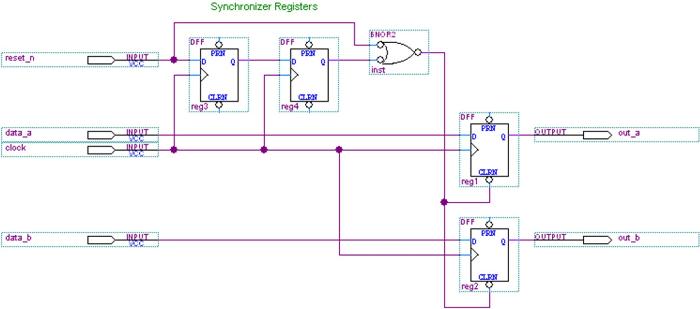

后面我们会讨论如何来实现这样的同步化的异步复位。我先来如图15所示的电路,同步寄存器(Synchronizer Register)象同步复位那样被使用,不过被同步后的异步复位和原始异步复位经过门控以后用来异步地复位后续寄存器。这个电路中异步复位信号异步地复位后续电路,并且复位是异步地释放。它的缺点就是复位路径上引入了门电路的延迟。

图15:带门控的同步化异步复位原理图

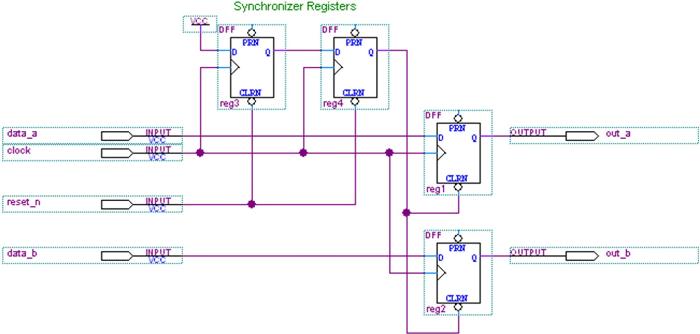

一种更好的实现方法如图16所示,这个电路去除了图15中复位路径上门电路延迟。异步复位输入直接连接到同步寄存器(Synchronizer Register)的CLRN端口上,这样复位立即生效。当复位撤除(释放)时,一个逻辑“1”从同步器(Synchronizer)被时钟打出用来同步地释放后续寄存器的复位。

图16:不带门控的同步化异步复位原理图

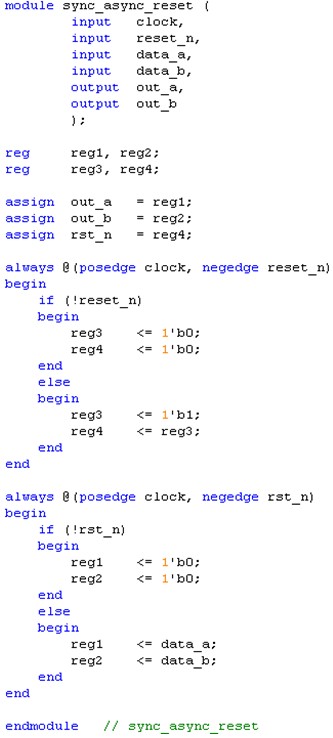

图16等效的Verilog代码如图17所示,第一个进程模块用来产生同步复位输出rst_n,rst_n作为第二个进程模块的异步复位。两个进程模块的复位信号都位于各自的敏感列表中。其实第一个进程模块就是将系统输入的异步复位进行同步,产生一个后续逻辑使用的同步化了的异步复位,所以我们看到第二个进程模块里将这个已经同步化了的复位信号当作异步复位使用。

图17:同步化异步复位的Verilog代码

同样,为了减少亚稳态对上述同步器中的两个寄存器的影响,同时也是为了增加平均无故障时间(MTBF),这两个寄存器应该在FPGA中被放置的越靠近越好,以尽量减少在器件中的布线延迟。Quartus II的fitter将会自动认识到这些寄存器是用于同步器,所以会自动地进行上述处理,作为本例这两个寄存器将会被布局到同一个LAB中。

尽管reset_n已经进行了上述同步化处理,时序约束的时候还是要使用set_false_path命令将其进行切割,而从同步寄存器输出的复位rst_n现在可以使用TimeQuest进行准确地Recovery和Removal分析。本设计的SDC约束和图14是一样,所以现在我们在Quartus II中编译这个设计并运行TimeQuest时序分析器,那么我们将会得到这个电路的Recovery和Removal的slack报告,如图18所示。

图18:同步化异步复位的Recovery和Removal分析

上述分析结果表明,两条路径(reg4到reg1和reg4到reg2)都进行了Recovery和Removal检查。这个电路的Recovery时间检查(就象建立时间检测一样)差不多有9ns的slack,而Removal(就象保持时间检查一样)也有660ps的slack。两个检查都得到通过,意味着这个电路没有时序错误路径。

使用上述同步化异步复位的一个代价是它们很容易受到噪声和窄脉冲的干扰。同样地,如果可能最好对输入到FPGA的异步复位先进行滤波和去抖动。图16中的同步化异步复位原理图可以确保同步后的异步至少有一个时钟周期的长度,如果需要扩展复位长度到n个时钟周期,那么可以增加同步器中的寄存器个数到n+1个。请一定确保外部输入的异步复位reset_n连接到了所有同步器寄存器的CLRN端口,这样确保使得产生的同步化异步复位能够被异步地置位。

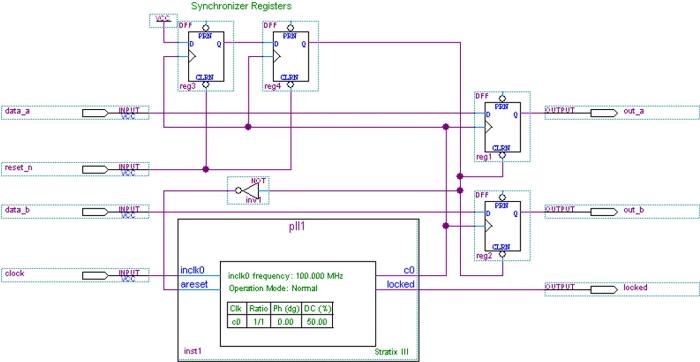

当有PLL涉及时,有些特殊情况需要考虑。比如我们来如图19所示的电路。需要同步的复位跟之前一样直接接到了同步器中寄存器的CLRN端口,而同步后的寄存器也同样接到了reg1和reg2的CLRN端口,同时也被接到PLL的areset端口。所有寄存器包括同步器中的寄存器的驱动时钟来自PLL的输出时钟。虽然看起来PLL使用了同步后的复位,实际上这是行不通的。当PLL处于复位状态时,PLL的c0是没有时钟输出的,因此同步器中的寄存器将无法清除复位(意思是复位无法得到释放)。结果是,这个电路将永远无法跳出复位。

图19:使用PLL时不正确实现同步化异步复位的原理图

为了解决这个问题,PLL的复位应该使用FPGA原始输入的异步复位reset_n(如图20所示,这里进行了取反,这主要取决于复位是‘0’有效还是‘1’有效,这里不讨论),而不是同步后的复位。此外,使用PLL的Lock输出来作为同步器中寄存器的时钟使能,是个不错的做法。因为这将防止同步后的复位在PLL的输出时钟稳定之前提前释放。

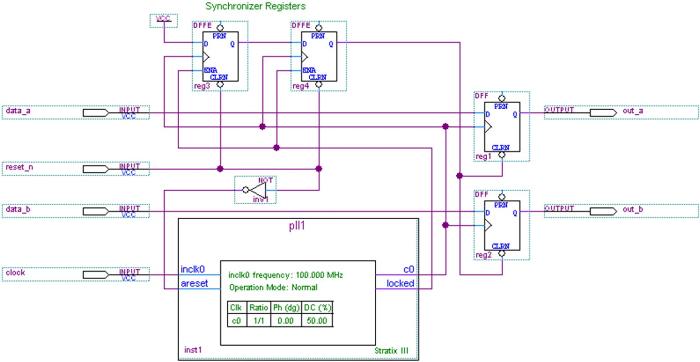

图20:使用PLL时正确实现同步化异步复位的原理图

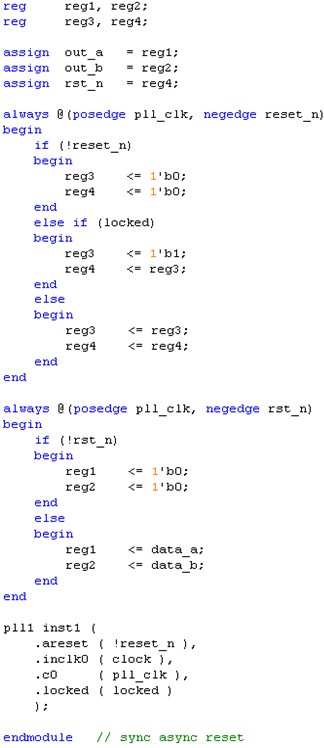

图21显示了图20所示是PLL正确实现同步化异步复位原理图的Verilog代码。

图21:使用PLL时正确实现同步化异步复位的Verilog代码

注意到上述代码中同步器的进程模块中多一个条件,即PLL的Locked信号,它作为同步器中的寄存器的同步时钟使能信号。同时注意下面例化的PLL以及两个个进程模块的时钟,这些都是当加入PLL时仅有的变化。

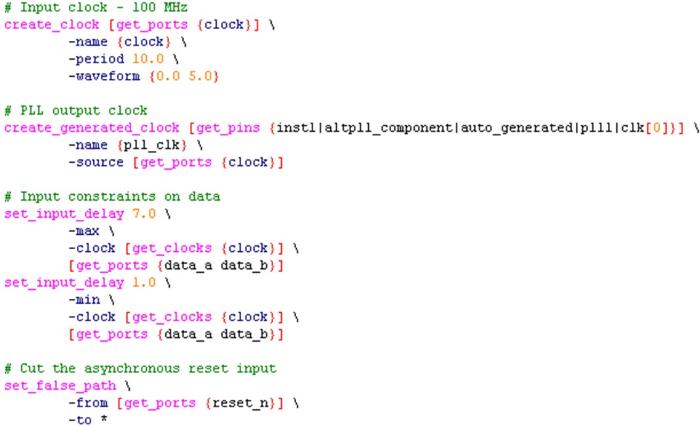

图22是需要给这个电路加入的SDC时序约束,基本和没有使用PLL相同,唯一的区别是需要使用create_generated_clock语句为PLL的输出时钟加约束(注意其实使用PLL后,可以直接使用语句derive_pll_clocks来简单地进行约束)。

图22:使用PLL时实现同步化异步复位的时序约束

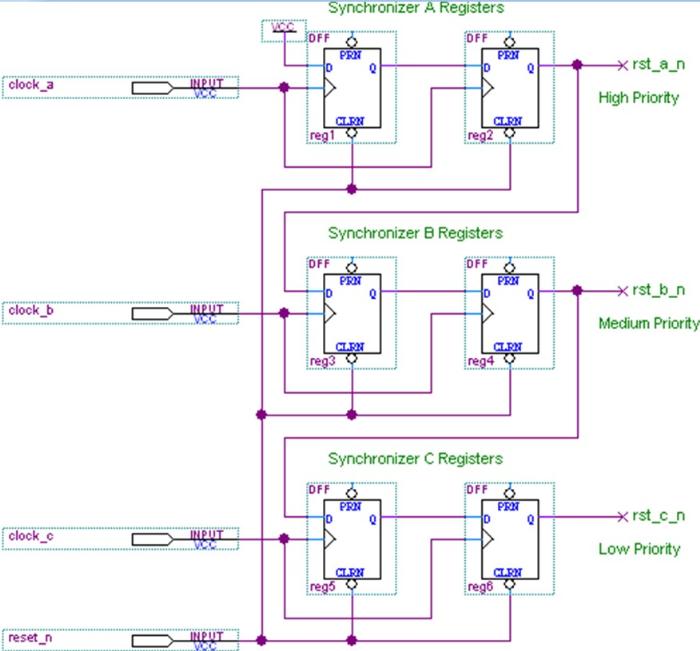

最后,还有一个值得一提的例子。如前所述,设计中的不同时钟域的寄存器如果需要复位,应该首先将复位同步到当前的时钟域后再使用,也就是说每个时钟都需要有一套自己的复位同步器寄存器。而且,有的时候设计的某些部分可能需要比其它部分先从复位状态释放,所以这就需要一个复位释放顺序的安排。图23给出了这样一个例子,同步寄存器都通过类似菊花链方式串起来,我们看到最上面的同步器具有最高优先级从复位状态跳出来。图23所示的电路中,所有的复位都同时有效,但是rst_a_n具有从复位状态跳出的最高优先级,接着是rst_b_n具有中等优先级,rst_c_n是最后被释放的。当然,如果在不同复位之间需要更长的间隔时间,可以在同步器中添加任意个数寄存器来达到需要的间隔长度。

图23:不同时钟域同步化异步复位释放优先级安排

总结

本文介绍了不同复位的优缺点,比如同步复位,异步复位以及同步化的异步复位。同步复位需要一个时钟,所以窄复位脉冲将会被忽略,然后同时增加了系统的抗干扰能力。同步复位是百分之一百的同步电路,所以不存在亚稳态问题。只是同步复位会带来额外的资源消耗以及数据路径上的延迟,基于此我们说同步复位不是最佳复位选择。TimeQuest可以象分析其它数据路径那样分析同步复位。

异步复位通常立即起作用,也容易被实现,而且由于它们不象同步复位那样会给数据路径引入额外的延迟,所以复位速度很快。同时相比同步复位,异步复位消耗更少的逻辑资源。比较不幸的是,它们无法通过TimeQuest来进行时序分析(其它静态时序分析器也无法分析),而且如果处理不当还会给电路带来亚稳态问题。异步复位的最大弱点是它们无法确保所有的寄存器在同一个时钟沿处跳出复位状态。这在带反馈的同步设计中是会有问题的,比如状态机设计。

在将异步复位连接到寄存器的异步输入端口前给它加入一个同步器,这样就创造一个叫同步化了的异步复位。这种复位具有异步复位那样的立即将复位作用于电路好处,同时又提高电路速度,因为它们不会给数据路径带来额外的延迟。同时,这种复位象同步复位那样避免了亚稳态问题,而且保证所有的寄存器能够同时从复位状态跳出。不象异步复位,同步化了异步复位可以在TimeQuest里分析Recovery和Removal。正是由于这些原因,同步化了的异步复位是大部分FPGA设计中复位电路首先方法。

注意:

1)PLL的复位应该使用FPGA原始输入的异步复位reset_n

2)复位信号的IO约束——看你的复位是同步复位还是异步复位,通常复位都会做成异步,这时候应该是false path的,如果同步,从管教输入的复位需要设最大输入延时。

3)对异步信号进行同步化(异步复位,同步释放),尽管reset_n已经进行了上述同步化处理,时序约束的时候还是要使用set_false_path命令将其进行切割,而从同步寄存器输出的复位rst_n现在可以使用TimeQuest进行准确地Recovery和Removal分析。

最后

以上就是可耐小兔子最近收集整理的关于异步复位同步化(同步化的异步复位)实现和注意事项的全部内容,更多相关异步复位同步化(同步化内容请搜索靠谱客的其他文章。

发表评论 取消回复