文章目录

- 简介

- 3位伪随机码

- 4位伪随机码

????声明:本文所使用的的所有代码均已编译并仿真通过,仿真结果附于文中。

????注:更多精彩请看: 面试常问的verilog代码汇总 一文

简介

伪随机序列又称为伪随机码,是一种人工生成的周期序列,可以作为数字通信中的一个信号源,用于检测数字通信系统错码的概率,即误码率。

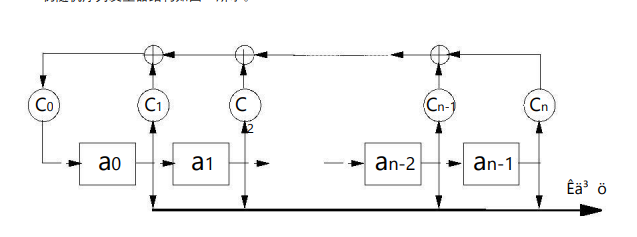

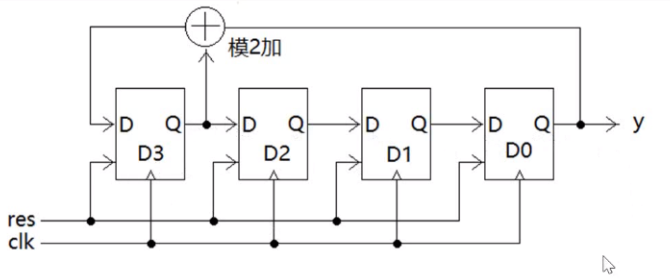

产生伪随机码的方式有很多,通常使用线性反馈移位寄存器(LFSR)来产生。所谓线性反馈,是指反馈函数中仅包含模 2 加运算(也就是逻辑异或),而不含非线性运算。由线性反馈寄存器产生的周期最长的二进制序列称为最大长度线线性反馈寄存器序列,简称m序列。如果移位寄存器长度为n,则m序列的周期是(2^n -1),没有全0的状态。

伪随机码发生器的初始状态由微处理器通过SEED寄存器发出。seed不能为全0的状态 ,因为0^0=0,会陷入0的死循环 。

上图中,C0…Cn表示反馈系数,与本原多项式中的各项系数相对应。如果反馈系数Ci为1则表示参与反馈,为0则表示不参与反馈,且 因为m 序列是由循环序列发生器产生的,所以 C0=Cn=1。

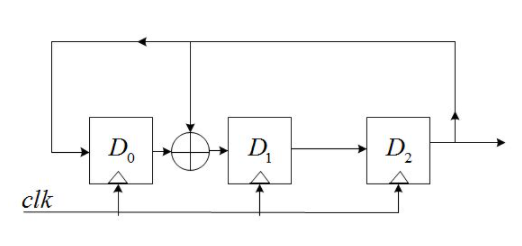

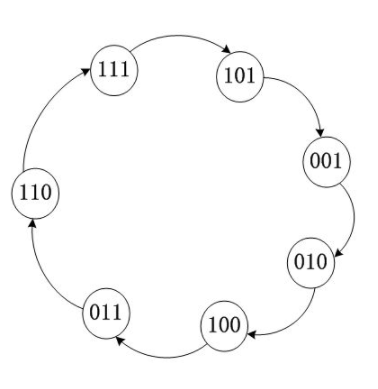

3位伪随机码

用3级线性反馈移位寄存器生成,会产生7个随机数循环。其电路示意图如下,并根据电路示意图给出状态转移图。

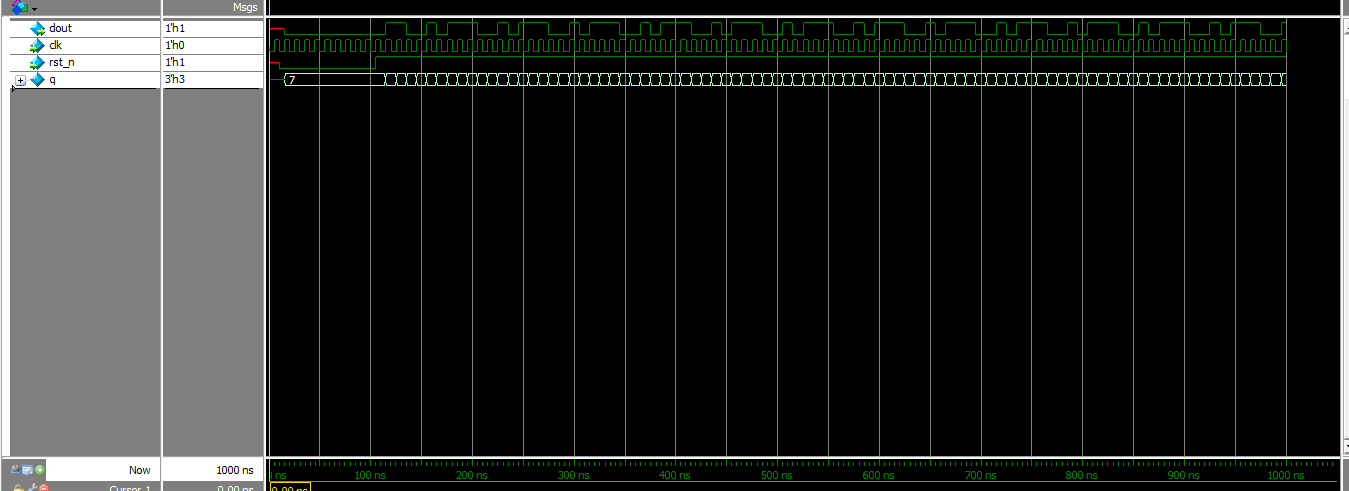

module fake_rand3(dout,clk,rst_n);

output dout;

input clk,rst_n;

reg dout;

reg [2:0]q;

always@(posedge clk)begin

if(!rst_n)begin

q <= 3'b111;//不能复位成全0

dout <= 0;

end

else begin

q[2] <= q[1];

q[1] <= q[2]^q[0];

q[0] <= q[2];

dout <= q[2];

end

end

endmodule

`timescale 1ns/1ps

module fake_rand3_tb;

wire dout;

reg clk,rst_n;

fake_rand3 dut(.dout(dout),.clk(clk),.rst_n(rst_n));

initial begin

clk <= 0;

forever begin

#5 clk <= !clk;

end

end

initial begin

#10 rst_n <= 0;

repeat(10) @(posedge clk);

rst_n <= 1;

end

endmodulee

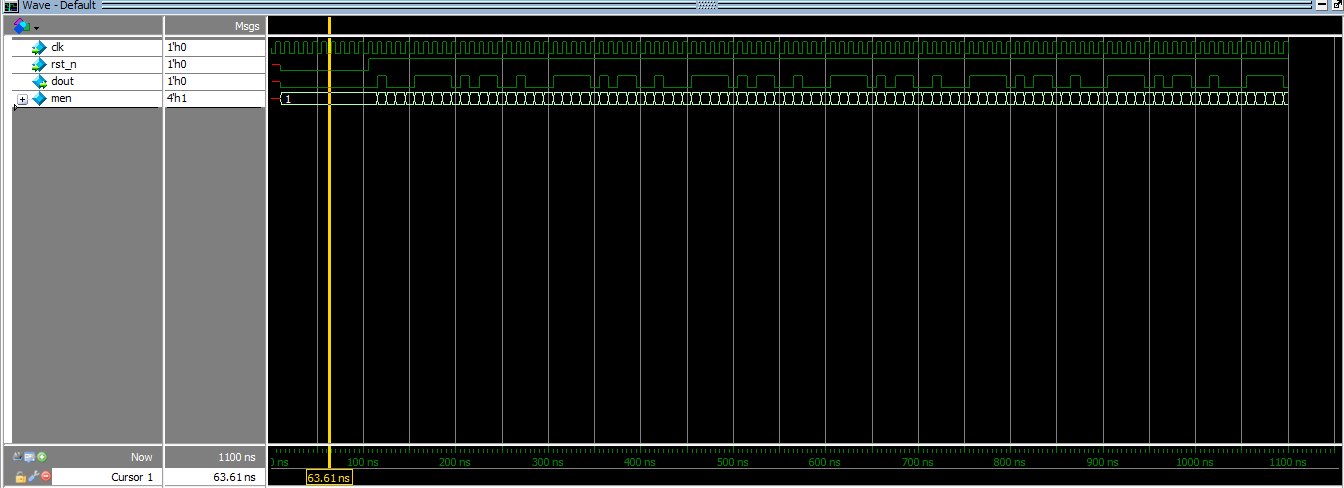

4位伪随机码

代码如下:

module m_gen5(clk,rst_n,dout);

input clk,rst_n;

output dout;

reg [3:0]men;

reg dout;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

dout <= 0;

men <= 4'b0001;//注意不能复位成全0,全0电路就会进入死循环

end

else begin

men[2:0] <= men[3:1];//左移1位

men[3] <= men[0] ^ men[3];//模2加

dout <= men[0];

end

end

endmodule

`timescale 1ns/1ps

module m_gen5_tb;

wire dout;

reg clk,rst_n;

m_gen5 dut(.dout(dout),.clk(clk),.rst_n(rst_n));

initial begin

clk <= 0;

forever begin

#5 clk <= !clk;

end

end

initial begin

#10 rst_n <= 0;

repeat(10) @(posedge clk);

rst_n <= 1;

end

endmodule

最后

以上就是单纯红牛最近收集整理的关于伪随机码(verilog)简介3位伪随机码4位伪随机码的全部内容,更多相关伪随机码(verilog)简介3位伪随机码4位伪随机码内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复